存儲器的區(qū)別是沒有外部讀寫地址線,這樣使用起來非常簡單,但缺點(diǎn)就是只能順序?qū)懭霐?shù)據(jù),順序的讀出數(shù)據(jù),其數(shù)據(jù)地址由內(nèi)部讀寫指針自動加1完成,不能像普通存儲器那樣可以由地址線決定讀取或?qū)懭肽硞€(gè)指定的地址。 用途1: 異步FIFO讀寫分別采用相互異步的不同時(shí)鐘。在現(xiàn)代集

2018-06-21 11:15:25 6164

6164

之前介紹了 SelectIO 邏輯資源,本篇咱們就聊一聊與SelectIO 邏輯資源水乳交融、相得益彰的另一個(gè)概念I(lǐng)O_FIFO。 1個(gè)IO_FIFO包括1個(gè)IN_FIFO 和1個(gè)OUT_FIFO

2020-11-29 10:08:00 2340

2340

FIFO是隊(duì)列機(jī)制中最簡單的,每個(gè)接口上只有一個(gè)FIFO隊(duì)列,表面上看FIFO隊(duì)列并沒有提供什么QoS保證,甚至很多人認(rèn)為FIFO嚴(yán)格意義上不算做一種隊(duì)列技術(shù),實(shí)則不然,FIFO是其它隊(duì)列的基礎(chǔ)

2022-07-10 09:22:00 1338

1338 FIFO (先入先出, First In First Out )存儲器,在 FPGA 和數(shù)字 IC 設(shè)計(jì)中非常常用。 根據(jù)接入的時(shí)鐘信號,可以分為同步 FIFO 和異步 FIFO 。

2023-06-27 10:24:37 1199

1199

相鄰的格雷碼只有1bit的差異,因此格雷碼常常用于異步fifo設(shè)計(jì)中,保證afifo的讀地址(或?qū)懙刂罚┍粚憰r(shí)鐘(或讀時(shí)鐘)采樣時(shí)最多只有1bit發(fā)生跳變。

2023-11-01 17:37:31 779

779

FIFO為什么不能正常工作?復(fù)位信號有效長度不夠,接口時(shí)序不匹配,可看下面這篇文章。 本文將介紹: 非DFX工程如何確保異步FIFO自帶的set_max_delay生效? DFX工程如何確保異步

2023-11-02 09:25:01 475

475

最近加的群里面有些萌新在進(jìn)行討論**FIFO的深度**的時(shí)候,覺得 **FIFO的深度計(jì)算比較難以理解** 。所

2023-11-28 16:19:46 347

347

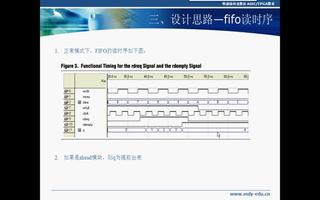

我使用CY7C68013與GPIF模型中的FPGA通信,我的問題是FIFO寫波不能觸發(fā)。我的進(jìn)度已經(jīng)附上了,有人能幫我嗎?非常感謝。 以上來自于百度翻譯 以下為原文i'm using a

2019-04-02 06:44:09

我使用68013A、GPIF模式、FIFO寫,發(fā)現(xiàn)每個(gè)寫入N個(gè)數(shù)據(jù),WRIFFIFO信號的長度比N個(gè)數(shù)據(jù)的長度長,結(jié)果是N+1數(shù)據(jù)寫入FIFO。為什么? 以上來自于百度翻譯 以下為原文I use

2019-03-14 06:38:42

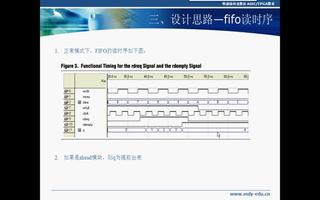

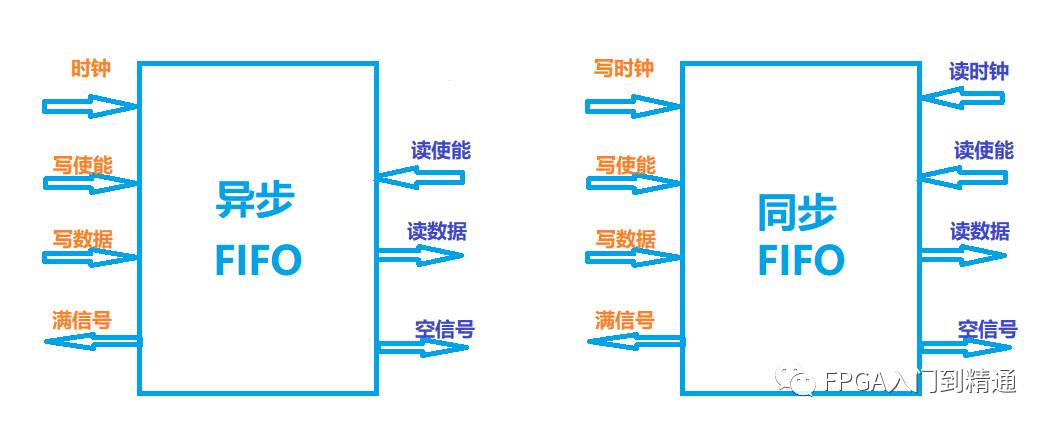

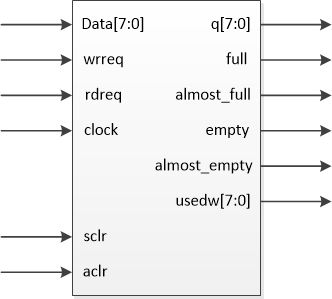

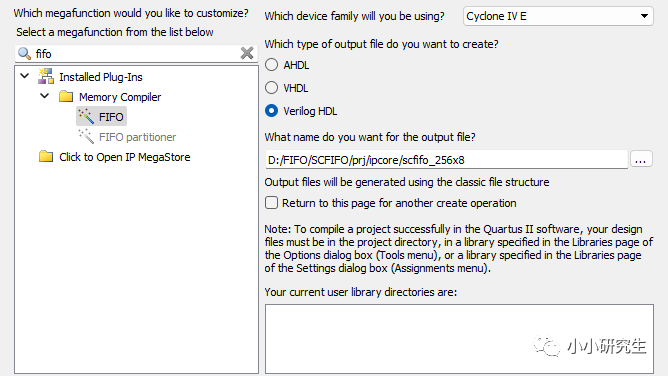

小梅哥FPGA:嵌入式塊RAM使用之FIFO課程目標(biāo):學(xué)會調(diào)用QuartusⅡ軟件中提供的FIFO核并通過仿真,了解其接口時(shí)序?qū)崿F(xiàn)現(xiàn)象:通過QuartusⅡ軟件中調(diào)用FIFO核,通過仿真來驗(yàn)證其接口

2021-12-27 08:05:35

入的指令先完成并引退,跟著才執(zhí)行第二條指令。 1.什么是FIFO? FIFO是英文First In First Out 的縮寫,是一種先進(jìn)先出的數(shù)據(jù)緩存器,他與普通存儲器的區(qū)別是沒有外部讀寫地址線,這樣使用起來非常簡單,但缺點(diǎn)就是只能順序?qū)懭霐?shù)據(jù),順序的讀出數(shù)據(jù),其數(shù)據(jù)地址由內(nèi)部讀寫指針自動加1完成

2022-02-16 06:55:41

大家好。現(xiàn)在我可以用評估板運(yùn)行奴隸FIFO異步示例。我仍然想知道如何檢查從FIFO GPIF的傳輸速度。使用UART調(diào)試器,我發(fā)現(xiàn)在從FIFO異步示例中數(shù)據(jù)傳輸不是那么快。如何提高傳輸速度和最大傳輸

2019-04-29 14:10:58

)-SPIXMOSI)來配置FPGA,然后使GPFI到32位從FIFO模式,顯然是可行的。在固件運(yùn)行時(shí),我想再次用SPI接口重新配置FPGA,但在那個(gè)時(shí)候,GPIF是32位從FIFO模式,我可以停止

2019-01-29 12:35:48

嗨,當(dāng)我們在FIFO或GPIF FIFO中討論FIFO時(shí),FIFO是終結(jié)點(diǎn)緩沖器嗎?也就是說,如果使用奴隸FIFO,當(dāng)外部CPU將一個(gè)字節(jié)寫入從屬FIFO時(shí),CPU直接將字節(jié)寫入端點(diǎn)緩沖器中,或者

2019-07-08 11:13:26

本帖最后由 一只耳朵怪 于 2018-6-13 15:01 編輯

SPI使用FIFO和不使用有什么區(qū)別,是不是使用FIFO效率更高

2018-06-13 11:12:07

首先介紹異步FIFO 的概念、應(yīng)用及其結(jié)構(gòu),然后分析實(shí)現(xiàn)異步FIFO的難點(diǎn)問題及其解決辦法; 在傳統(tǒng)設(shè)計(jì)的基礎(chǔ)上提出一種新穎的電路結(jié)構(gòu)并對其進(jìn)行綜合仿真和FPGA 實(shí)現(xiàn)。

2009-04-16 09:25:29 46

46 1.什么是FIFO?FIFO是英文First In First Out 的縮寫,是一種先進(jìn)先出的數(shù)

2009-07-22 16:00:48 0

0 FIFO中文應(yīng)用筆記

2009-07-28 10:03:31 30

30 A7105 Reference code for FIFO mode:1. 簡介這文件系對 RF chip -A7105 FIFO mode 做一簡單的應(yīng)用范程序,供使用者能夠快速應(yīng)用這 RF chip。2. 系統(tǒng)概述本范程序使用簡單的跳頻(frequency hop

2009-09-29 10:22:17 36

36 系統(tǒng)在上電復(fù)位時(shí),SPI工作在標(biāo)準(zhǔn)SPI模式,禁止FIFO功能。FIFO的寄存器SPIFFTX、SPIFFRX和SPIFFCT不起作用。通過將SPIFFTX寄存器中的SPIFFEN的位置為1,使能FIFO模式。SPIRST能在操作的任一階

2009-09-29 10:38:26 33

33 設(shè)計(jì)一個(gè)FIFO是ASIC設(shè)計(jì)者遇到的最普遍的問題之一。本文著重介紹怎樣設(shè)計(jì)FIFO——這是一個(gè)看似簡單卻很復(fù)雜的任務(wù)。一開始,要注意,FIFO通常用于時(shí)鐘域的過渡,是雙時(shí)鐘設(shè)計(jì)

2009-10-15 08:44:35 94

94 本文主要研究了用FPGA 芯片內(nèi)部的EBRSRAM 來實(shí)現(xiàn)異步FIFO 設(shè)計(jì)方案,重點(diǎn)闡述了異步FIFO 的標(biāo)志信號——空/滿狀態(tài)的設(shè)計(jì)思路,并且用VHDL 語言實(shí)現(xiàn),最后進(jìn)行了仿真驗(yàn)證。

2010-01-13 17:11:58 40

40 給出了一個(gè)利用格雷碼對地址編碼的羿步FIFO 的實(shí)現(xiàn)方法,并給出了VHDL 程序,以解決異步讀寫時(shí)鐘引起的問題。

2010-07-16 15:15:42 26

26 介紹了異步FIFO在Camera Link接口中的應(yīng)用,將Camera Link接口中的幀有效信號FVAL和行有效信號LVAL引入到異步FIFO的設(shè)計(jì)中。分析了FPGA中設(shè)計(jì)異步FIFO的難點(diǎn),解決了異步FIFO設(shè)計(jì)中存在的兩

2010-07-28 16:08:06 32

32 設(shè)計(jì)工程師通常在FPGA上實(shí)現(xiàn)FIFO(先進(jìn)先出寄存器)的時(shí)候,都會使用由芯片提供商所提供的FIFO。但是,由于其通用性使得其針對性變差,某些情況下會變得不方便或者將增加硬

2010-10-27 15:40:30 38

38 摘要:使用FIFO同步源自不同時(shí)鐘域的數(shù)據(jù)是在數(shù)字IC設(shè)計(jì)中經(jīng)常使用的方法,設(shè)計(jì)功能正確的FUFO會遇到很多問題,探討了兩種不同的異步FIFO的設(shè)計(jì)思路。兩種思路

2006-03-24 12:58:33 680

680

摘要:首先介紹異步FIFO的概念、應(yīng)用及其結(jié)構(gòu),然后分析實(shí)現(xiàn)異步FIFO的難點(diǎn)問題及其解決辦法;在傳統(tǒng)設(shè)計(jì)的基礎(chǔ)上提出一種新穎的電路結(jié)構(gòu)并對其進(jìn)行

2009-06-20 12:46:50 3667

3667

基于FPGA的FIFO設(shè)計(jì)和應(yīng)用

引 言

在利用DSP實(shí)現(xiàn)視頻實(shí)時(shí)跟蹤時(shí),需要進(jìn)行大量高速的圖像采集。而DSP本身自帶的FIFO并不足以支持系統(tǒng)中大量數(shù)據(jù)的暫時(shí)存儲

2009-11-20 11:25:45 2127

2127

什么是VALU/FIFO

(Vector Arithmetic Logic Unit,向量算術(shù)邏輯單元)在處理器中用于向 量運(yùn)算的部分。

(First Input First Out

2010-02-04 10:17:50 379

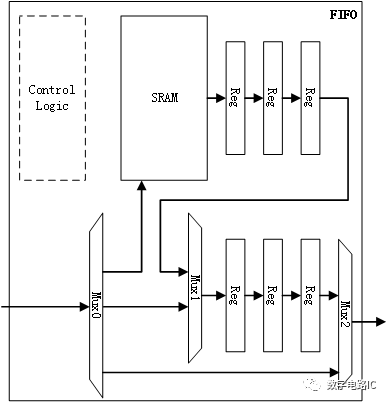

379 FPGA設(shè)計(jì)的高速FIFO電路技術(shù)

本文主要介紹高速FIFO電路在數(shù)據(jù)采集系統(tǒng)中的應(yīng)用,相關(guān)電路主要有高速A/D轉(zhuǎn)換器、FPGA、SDRAM存儲器等。圖1為本方案的結(jié)構(gòu)框圖。在大容量

2010-05-27 09:58:59 2226

2226

1 FIFO概述

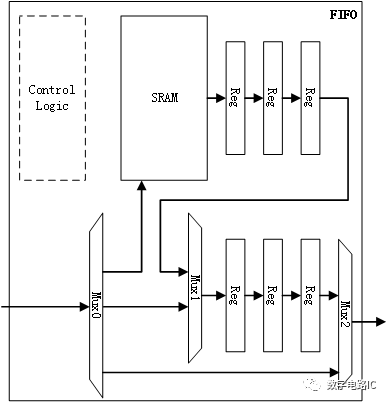

FIFO芯片是一種具有存儲功能的高速邏輯芯片,可在高速數(shù)字系統(tǒng)中用作數(shù)據(jù)緩存。FIFO通常利用雙口RAM和讀寫地址產(chǎn)生模塊來實(shí)現(xiàn)其功能。FIFO的接口信號包括異步

2010-08-06 10:22:04 5019

5019

為了解決基于LabVIEWFPGA模塊的DMAFIFO深度設(shè)定不當(dāng)帶來的數(shù)據(jù)不連續(xù)問題,結(jié)合LabVIEWFPGA的編程特點(diǎn)和DMA FIFO的工作原理,提出了一種設(shè)定 FIFO 深度的方法。對FIFO不同深度的實(shí)驗(yàn)表明,采

2011-09-26 13:45:17 6922

6922

關(guān)于fifo攝像頭的有關(guān)資料,非常全,還內(nèi)有代碼

2015-11-03 11:22:07 0

0 FIFO_學(xué)習(xí)心得。 FIFO_學(xué)習(xí)心得

2015-11-09 14:07:47 6

6 異步FIFO結(jié)構(gòu)及FPGA設(shè)計(jì),解決亞穩(wěn)態(tài)的問題

2015-11-10 15:21:37 4

4 Proteus程序之AMP應(yīng)用UART0_FIFO

2016-01-18 17:44:11 4

4 基于FLASH的FIFO讀寫,介紹的比較詳細(xì),值得一讀。

2016-04-28 10:30:27 22

22 最經(jīng)典的FIFO原理,詳細(xì)講述了FIFO的原理,適合入門新手,仔細(xì)分析閱讀,也適合高手查閱。

2016-05-03 15:15:08 0

0 異步FIFO在FPGA與DSP通信中的運(yùn)用

2016-05-19 11:17:11 0

0 VHDL例程 FIFO程序,感興趣的小伙伴們可以瞧一瞧。

2016-11-10 17:12:34 4

4 FIFO的使用非常廣泛,一般用于不同時(shí)鐘域之間的數(shù)據(jù)傳輸,比如FIFO的一端是AD數(shù)據(jù)采集,另一端是計(jì)算機(jī)的PCI總線,假設(shè)其AD采集的速率為16位100KSPS,那么每秒的數(shù)據(jù)量為100K

2017-09-16 09:09:09 1

1 基于異步FIFO在FPGA與DSP通信中的運(yùn)用

2017-10-19 10:30:56 10

10 基于FIFO的高速A_D和DSP接口設(shè)計(jì)

2017-10-19 14:10:23 9

9 本文首先對異步 FIFO 設(shè)計(jì)的重點(diǎn)難點(diǎn)進(jìn)行分析,最后給出詳細(xì)代碼。 一、FIFO簡單講解 FIFO的本質(zhì)是RAM, 先進(jìn)先出 重要參數(shù):fifo深度(簡單來說就是需要存多少個(gè)數(shù)據(jù)) fifo

2017-11-15 12:52:41 7993

7993

在現(xiàn)代電路設(shè)計(jì)中,一個(gè)系統(tǒng)往往包含了多個(gè)時(shí)鐘,如何在異步時(shí)鐘間傳遞數(shù)據(jù)成為一個(gè)很重要的問題,而使用異步FIFO可以有效地解決這個(gè)問題。異步FIFO是一種在電子系統(tǒng)中得到廣泛應(yīng)用的器件,文中介紹了一種基于FPGA的異步FIFO設(shè)計(jì)方法。使用這種方法可以設(shè)計(jì)出高速、高可靠的異步FIFO。

2018-07-17 08:33:00 7873

7873

FIFO( First In First Out)簡單說就是指先進(jìn)先出。由于微電子技術(shù)的飛速發(fā)展,新一代FIFO芯片容量越來越大,體積越來越小,價(jià)格越來越便宜。作為一種新型大規(guī)模集成電路,FIFO芯片以其靈活、方便、高效的特性。

2017-12-06 14:29:31 10173

10173

在現(xiàn)代的集成電路芯片中,隨著設(shè)計(jì)規(guī)模的不斷擴(kuò)大,一個(gè)系統(tǒng)中往往含有數(shù)個(gè)時(shí)鐘。多時(shí)鐘域帶來的一個(gè)問題就是,如何設(shè)計(jì)異步時(shí)鐘之間的接口電路。異步FIFO(Firstln F irsto ut)是解決這個(gè)

2018-02-07 14:22:54 0

0 FIFO是英文First In First Out 的縮寫,是一種先進(jìn)先出的數(shù)據(jù)緩存器,他與普通存儲器的區(qū)別是沒有外部讀寫地址線,這樣使用起來非常簡單,但缺點(diǎn)就是只能順序?qū)懭霐?shù)據(jù),順序的讀出數(shù)據(jù),其數(shù)據(jù)地址由內(nèi)部讀寫指針自動加1完成,不能像普通存儲器那樣可以由地址線決定讀取或?qū)懭肽硞€(gè)指定的地址。

2018-07-20 08:00:00 22

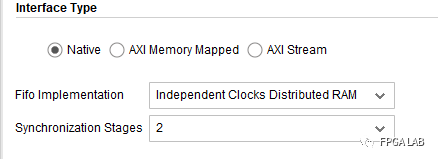

22 配置FIFO的方法有兩種:

一種是通過QUARTUS II 中TOOLS下的MegaWizard Plug-In Manager 中選擇FIFO參數(shù)編輯器來搭建自己需要的FIFO,這是自動生成FIFO的方法

2018-07-20 08:00:00 17

17 設(shè)計(jì)工程師通常在FPGA上實(shí)現(xiàn)FIFO(先進(jìn)先出寄存器)的時(shí)候,都會使用由芯片提供商所提供的FIFO。但是,由于其通用性使得其針對性變差,某些情況下會變得不方便或者將增加硬件成本。此時(shí),需要進(jìn)行自行

2018-11-28 08:10:00 6709

6709

無名管道應(yīng)用的一個(gè)重大限制是它沒有名字,因此,只能用于具有親緣關(guān)系的進(jìn)程間通信,在有名管道(named pipe或FIFO)提出后,該限制得到了克服。FIFO不同于管道之處在于它提供

2019-04-02 14:45:10 291

291 FIFO隊(duì)列具有處理簡單,開銷小的優(yōu)點(diǎn)。但FIFO不區(qū)分報(bào)文類型,采用盡力而為的轉(zhuǎn)發(fā)模式,使對時(shí)間敏感的實(shí)時(shí)應(yīng)用(如VoIP)的延遲得不到保證,關(guān)鍵業(yè)務(wù)的帶寬也不能得到保證。

2019-12-02 07:02:00 1471

1471

FIFO隊(duì)列具有處理簡單,開銷小的優(yōu)點(diǎn)。但FIFO不區(qū)分報(bào)文類型,采用盡力而為的轉(zhuǎn)發(fā)模式,使對時(shí)間敏感的實(shí)時(shí)應(yīng)用(如VoIP)的延遲得不到保證,關(guān)鍵業(yè)務(wù)的帶寬也不能得到保證。

2019-11-29 07:10:00 1595

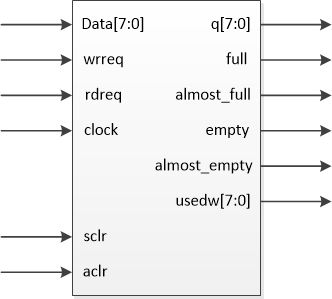

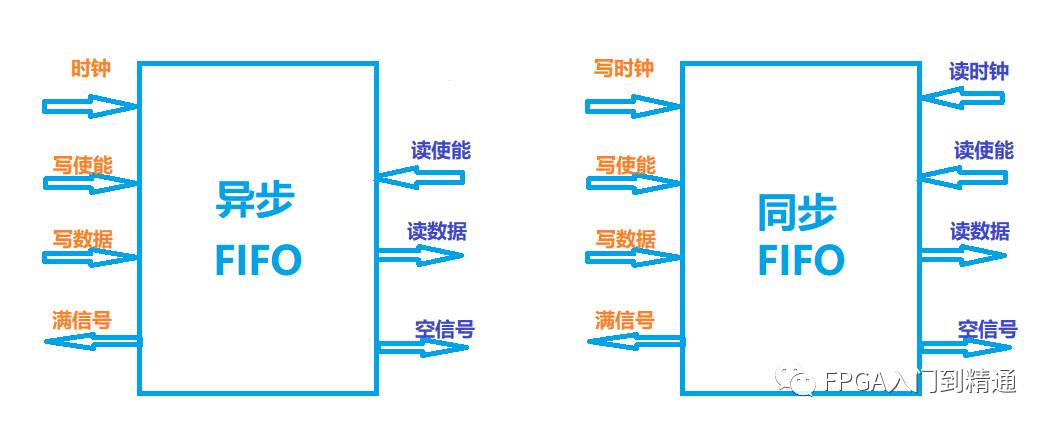

1595 根據(jù)FIFO工作的時(shí)鐘域,可以將FIFO分為同步FIFO和異步FIFO。同步FIFO是指讀時(shí)鐘和寫時(shí)鐘為同一個(gè)時(shí)鐘。在時(shí)鐘沿來臨時(shí)同時(shí)發(fā)生讀寫操作。異步FIFO是指讀寫時(shí)鐘不一致,讀寫時(shí)鐘是互相獨(dú)立的。

2019-11-29 07:08:00 1608

1608 FIFO隊(duì)列不對報(bào)文進(jìn)行分類,當(dāng)報(bào)文進(jìn)入接口的速度大于接口能發(fā)送的速度時(shí),FIFO按報(bào)文到達(dá)接口的先后順序讓報(bào)文進(jìn)入隊(duì)列,同時(shí),FIFO在隊(duì)列的出口讓報(bào)文按進(jìn)隊(duì)的順序出隊(duì),先進(jìn)的報(bào)文將先出隊(duì),后進(jìn)的報(bào)文將后出隊(duì)。

2019-11-29 07:04:00 4345

4345 FIFO( First Input First Output)簡單說就是指先進(jìn)先出。由于微電子技術(shù)的飛速發(fā)展,新一代FIFO芯片容量越來越大,體積越來越小,價(jià)格越來越便宜。

2019-11-18 07:10:00 1605

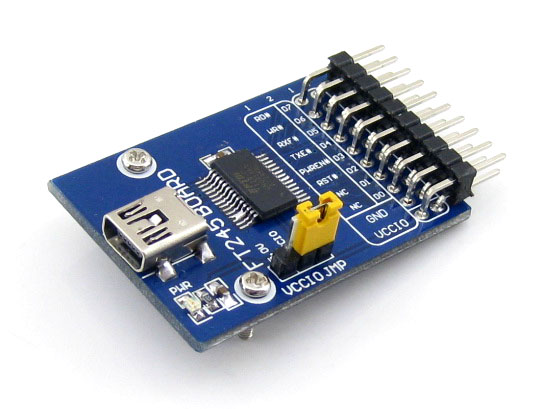

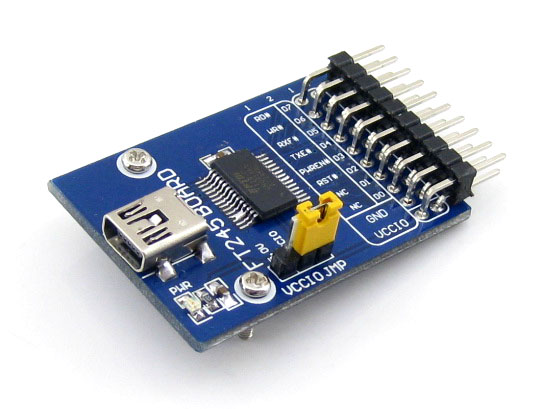

1605 FT245 USB轉(zhuǎn)FIFO模塊 USB mini接口

支持3種供電模式 提供USB驅(qū)動 電路原理圖

型號 FT245 USB FIFO Board (mini)

2019-12-30 11:26:24 4415

4415

FPGA電路FIFO設(shè)計(jì)的源代碼

2020-07-08 17:34:37 15

15 FIFO是FPGA處理跨時(shí)鐘和數(shù)據(jù)緩存的必要IP,可以這么說,只要是任意一個(gè)成熟的FPGA涉及,一定會涉及到FIFO。但是我在使用異步FIFO的時(shí)候,碰見幾個(gè)大坑,這里總結(jié)如下,避免后來者入坑。

2021-03-12 06:01:34 12

12 一:fifo是什么 FIFO的完整英文拼寫為FirstIn First Out,即先進(jìn)先出。FPGA或者ASIC中使用到的FIFO一般指的是對數(shù)據(jù)的存儲具有先進(jìn)先出特性的一個(gè)存儲器,常被用于數(shù)據(jù)

2021-03-12 16:30:48 2795

2795

1.定義 FIFO是英文First In First Out 的縮寫,是一種先進(jìn)先出的數(shù)據(jù)緩存器,他與普通存儲器的區(qū)別是沒有外部讀寫地址線,這樣使用起來非常簡單,但缺點(diǎn)就是只能順序?qū)懭霐?shù)據(jù),順序

2021-04-09 17:31:42 4697

4697

利用ISE的SDRAM設(shè)計(jì)的FIFO實(shí)驗(yàn)(嵌入式開發(fā)轉(zhuǎn)后端開發(fā))-利用ISE的SDRAM設(shè)計(jì)的FIFO實(shí)驗(yàn),適合感興趣的學(xué)習(xí)者學(xué)習(xí),可以提高自己的能力,大家可以多交流哈

2021-08-04 12:14:36 18

18 異步FIFO通過比較讀寫地址進(jìn)行滿空判斷,但是讀寫地址屬于不同的時(shí)鐘域,所以在比較之前需要先將讀寫地址進(jìn)行同步處理,將寫地址同步到讀時(shí)鐘域再和讀地址比較進(jìn)行FIFO空狀態(tài)判斷(同步后的寫地址一定

2021-08-04 14:05:21 3794

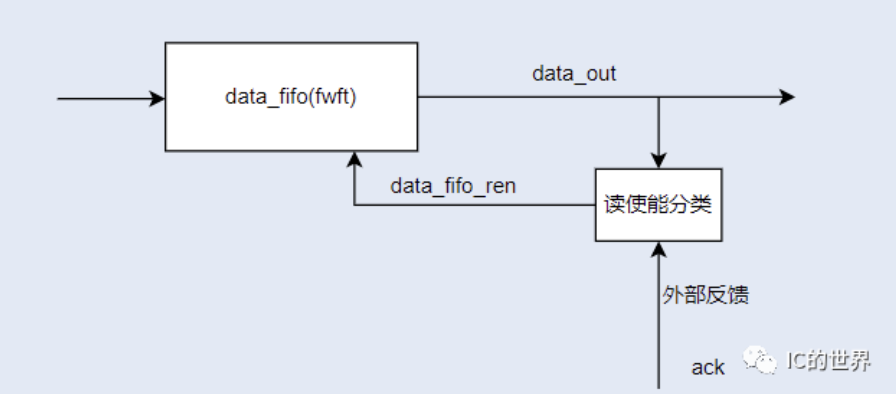

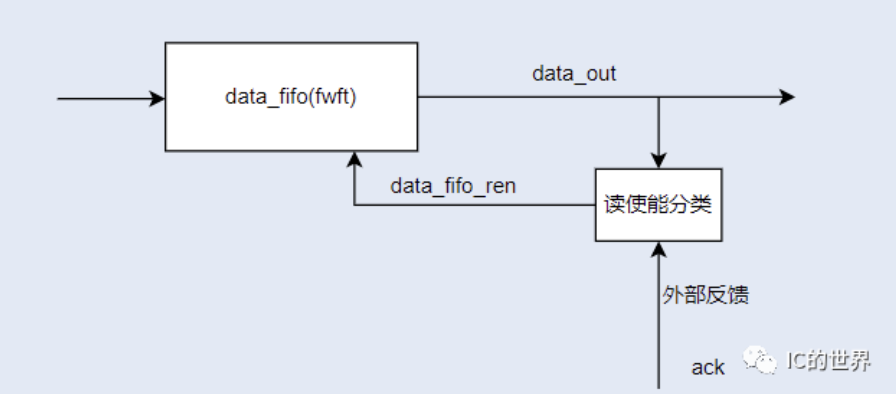

3794 FIFO是在FPGA設(shè)計(jì)中使用的非常頻繁,也是影響FPGA設(shè)計(jì)代碼穩(wěn)定性以及效率等得關(guān)鍵因素。在數(shù)據(jù)連續(xù)讀取時(shí),為了能不間斷的讀出數(shù)據(jù)而又不導(dǎo)致FIFO為空后還錯誤的讀出數(shù)據(jù)。可以將FIFO

2021-09-09 11:15:00 6293

6293 STM32 串口 FIFO

2021-12-03 09:36:08 37

37 入的指令先完成并引退,跟著才執(zhí)行第二條指令。 1.什么是FIFO? FIFO是英文First In First Out 的縮寫,是一種先進(jìn)先出的數(shù)據(jù)緩存器,他與普通存儲器的區(qū)別是沒有外部讀寫地址線,這樣使用起來非常簡單,但缺點(diǎn)就是只能順序?qū)懭霐?shù)據(jù),順序的讀出數(shù)據(jù),其數(shù)據(jù)地址由內(nèi)部讀寫指針自動加1完成

2021-12-17 18:29:31 10

10 FIFO最常被用來解決寫、讀不匹配的問題(時(shí)鐘、位寬),總結(jié)下來,其實(shí)FIFO最大的作用就是緩沖。既然是緩沖,那么就要知道這個(gè)緩存的空間到底需要多大。接下來的討論,都建立在滿足一次FIFO突發(fā)傳輸

2022-02-26 17:41:52 3045

3045

FIFO是FPGA項(xiàng)目中使用最多的IP核,一個(gè)項(xiàng)目使用幾個(gè),甚至是幾十個(gè)FIFO都是很正常的。通常情況下,每個(gè)FIFO的參數(shù),特別是位寬和深度,是不同的。

2022-03-08 11:06:12 4520

4520

在FPGA中對圖像的一行數(shù)據(jù)進(jìn)行緩存時(shí),可以采用FIFO這一結(jié)構(gòu),如上圖所示,新一行圖像數(shù)據(jù)流入到FIFO1中,FIFO1中會對圖像數(shù)據(jù)進(jìn)行緩存,當(dāng)FIFO1中緩存有一行圖像數(shù)據(jù)時(shí),在下一行圖像數(shù)據(jù)來臨的時(shí)候,將FIFO1中緩存的圖像數(shù)據(jù)讀出,并傳遞給下一個(gè)FIFO

2022-05-10 09:59:29 3056

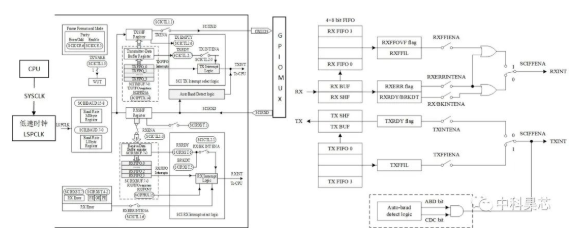

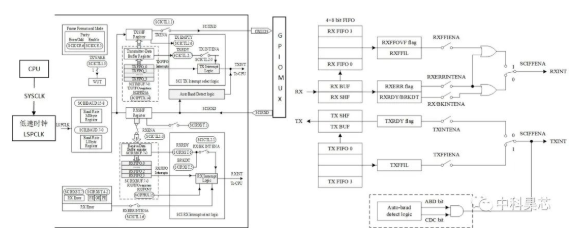

3056 自中科昊芯推出專題講解SCI串口通信以來,第一期主要講解SCI串口FIFO通信原理,第二期主要講解SCI串口自動波特率,本期主要講解FIFO中斷通信邏輯。

2022-05-16 09:53:28 2301

2301

由于平時(shí)我們工作中,FIFO都是直接調(diào)用IP核,對于FIFO深度選擇并沒有很在意,而在筆試面試過程中,經(jīng)常被問及的問題之一就是如何計(jì)算FIFO深度。

2022-07-03 17:25:28 2222

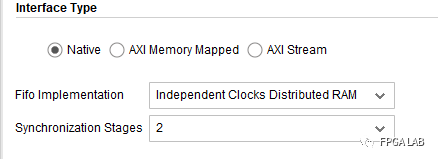

2222 FIFO的使用非常廣泛,一般用于不同時(shí)鐘域之間的數(shù)據(jù)傳輸,或者用于不同數(shù)據(jù)寬度之間的數(shù)據(jù)匹配。在實(shí)際的工程應(yīng)用,可以根據(jù)需要自己寫FIFO。不考慮資源的情況下,也可以使用Xilinx提供的IP核來完成。

2022-08-14 10:49:47 3567

3567 FIFO是First in First out 的縮寫,一般是由寄存器reg或者ram搭起來的,相對于普通存儲器而言,FIFO沒有地址可操作的地址總線,因而使用比較方便,但是數(shù)據(jù)只能像水流一樣排隊(duì)進(jìn)排隊(duì)出。

2022-08-19 09:02:47 1829

1829 邏輯核? IP FIFO生成器用戶指南描述了FIFO生成器,以及有關(guān)設(shè)計(jì)、定制和實(shí)現(xiàn)的信息核心。

2022-08-28 11:09:00 2

2 FIFO可以緩存串口接收到的數(shù)據(jù),因此我們可以利用FIFO來減少中斷次數(shù)。以NXP的lpc1778芯片為例,接收FIFO的觸發(fā)級別可以設(shè)置為1、2、4、8、14字節(jié),推薦使用8字節(jié)或者14字節(jié),這也是PC串口接收FIFO的默認(rèn)值。

2022-10-18 10:01:18 695

695 FIFO的分類根均FIFO工作的時(shí)鐘域,可以將FIFO分為同步FIFO和異步FIFO。同步FIFO是指讀時(shí)鐘和寫時(shí)鐘為同一個(gè)時(shí)鐘。在時(shí)鐘沿來臨時(shí)同時(shí)發(fā)生讀寫操作。異步FIFO是指讀寫時(shí)鐘不一致,讀寫時(shí)鐘是互相獨(dú)立的。

2022-11-01 09:57:08 1315

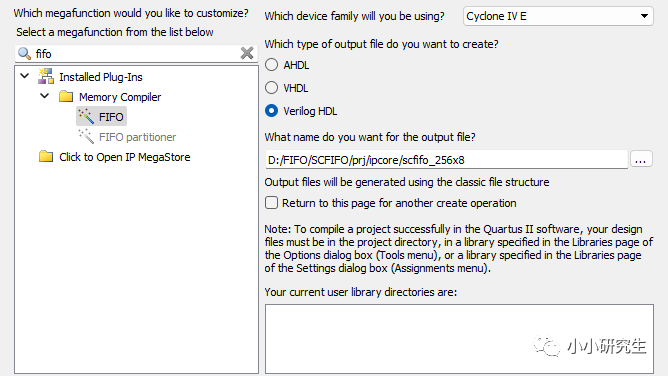

1315 同步FIFO的意思是說FIFO的讀寫時(shí)鐘是同一個(gè)時(shí)鐘,不同于異步FIFO,異步FIFO的讀寫時(shí)鐘是完全異步的。同步FIFO的對外接口包括時(shí)鐘,清零,讀請求,寫請求,數(shù)據(jù)輸入總線,數(shù)據(jù)輸出總線,空以及滿信號。

2022-11-01 09:58:16 1189

1189 FIFO 是我們設(shè)計(jì)中常用的工具,因?yàn)樗鼈兪刮覀兡軌蛟谶M(jìn)行信號和圖像處理時(shí)緩沖數(shù)據(jù)。我們還使用異步FIFO來處理數(shù)據(jù)總線的時(shí)鐘域交叉問題。

2022-11-04 09:14:11 3214

3214 異步fifo詳解 一. 什么是異步FIFO FIFO即First in First out的英文簡稱,是一種先進(jìn)先出的數(shù)據(jù)緩存器,與普通存儲器的區(qū)別在于沒有外部讀寫的地址線,缺點(diǎn)是只能順序的讀取

2022-12-12 14:17:41 2789

2789 FIFO(First In First Out)是異步數(shù)據(jù)傳輸時(shí)經(jīng)常使用的存儲器。該存儲器的特點(diǎn)是數(shù)據(jù)先進(jìn)先出(后進(jìn)后出)。其實(shí),多位寬數(shù)據(jù)的異步傳輸問題,無論是從快時(shí)鐘到慢時(shí)鐘域,還是從慢時(shí)鐘到快時(shí)鐘域,都可以使用 FIFO 處理。

2023-03-26 16:00:21 1823

1823

FIFO(First In First Out )先入先出存儲器,在FPG設(shè)計(jì)中常用于跨時(shí)鐘域的處理,FIFO可簡單分為同步FIFO和異步FIFO。

2023-04-25 15:55:28 2892

2892

今天咱們開始聊聊FIFO的設(shè)計(jì)。FIFO是一個(gè)數(shù)字電路中常見的模塊,主要作用是數(shù)據(jù)產(chǎn)生端和接受端在短期內(nèi)速率不匹配時(shí)作為數(shù)據(jù)緩存。FIFO是指First In, First Out,即先進(jìn)先出,跟大家排隊(duì)一樣。越早排隊(duì)的人排在越前面,輪到他的次序也越早,所以FIFO有些時(shí)候也被稱為隊(duì)列queue。

2023-05-04 15:48:20 544

544 FIFO是異步數(shù)據(jù)傳輸時(shí)常用的存儲器,多bit數(shù)據(jù)異步傳輸時(shí),無論是從快時(shí)鐘域到慢時(shí)鐘域,還是從慢時(shí)鐘域到快時(shí)鐘域,都可以使用FIFO處理。

2023-05-26 16:12:49 978

978

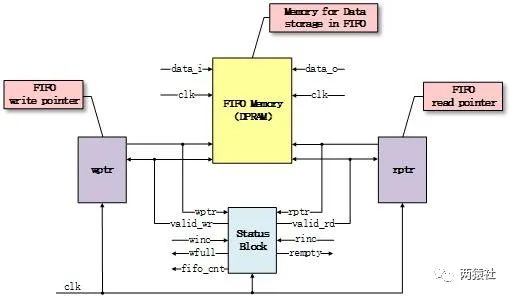

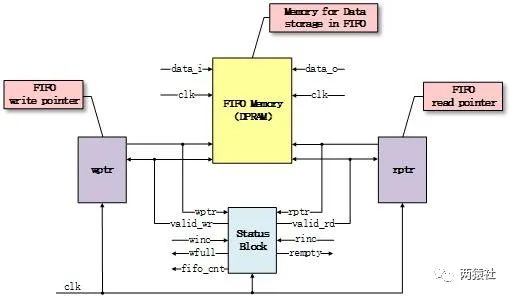

異步FIFO主要由五部分組成:寫控制端、讀控制端、FIFO Memory和兩個(gè)時(shí)鐘同步端

2023-05-26 16:17:20 911

911

FIFO,F(xiàn)irst In First Out,先入先出隊(duì)列,顧名思義,即第一個(gè)到達(dá)的數(shù)據(jù)也將會是第一個(gè)離開。

2023-06-05 14:39:33 535

535

FIFO 是FPGA設(shè)計(jì)中最有用的模塊之一。FIFO 在模塊之間提供簡單的握手和同步機(jī)制,是設(shè)計(jì)人員將數(shù)據(jù)從一個(gè)模塊傳輸?shù)搅硪粋€(gè)模塊的常用選擇。

2023-06-14 08:59:29 223

223 ? FIFO 是FPGA設(shè)計(jì)中最有用的模塊之一。FIFO 在模塊之間提供簡單的握手和同步機(jī)制,是設(shè)計(jì)人員將數(shù)據(jù)從一個(gè)模塊傳輸?shù)搅硪粋€(gè)模塊的常用選擇。 在這篇文章中,展示了一個(gè)簡單的 RTL 同步

2023-06-14 09:02:19 461

461 FIFO?還是FIFO IP核?這也需要寫總結(jié)嗎?太容易了吧。如果我是一個(gè)正在處于面試找工作中的年輕人,肯定關(guān)注的是如何手撕FIFO,這也是當(dāng)時(shí)校招時(shí)候干過的事情。

2023-06-21 14:22:09 817

817

在FPGA的設(shè)計(jì)中的,內(nèi)部的FIFO和RAM是兩種非常常見的存儲單元

2023-07-11 17:23:33 956

956 FIFO,先進(jìn)先出。在FPGA中使用的FIFO一般是指對數(shù)據(jù)的存儲具有先進(jìn)先出的緩沖器,FIFO與普通的存儲器的不同在于它沒有讀寫地址線。舉個(gè)例子,當(dāng)FPGA從外部傳感器讀取到一連串?dāng)?shù)據(jù)時(shí),首先

2023-07-23 11:47:03 369

369

Vivado IP核提供了強(qiáng)大的FIFO生成器,可以通過圖形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 1625

1625

FPGA廠商提供了豐富的IP核,基礎(chǔ)性IP核都是可以直接免費(fèi)調(diào)用的,比如FIFO、RAM等等。

2023-08-07 15:41:28 1293

1293

FIFO(First In First Out, 先入先出 ),是一種數(shù)據(jù)緩沖器,用來實(shí)現(xiàn)數(shù)據(jù)先入先出的讀寫方式。數(shù)據(jù)按順序?qū)懭?FIFO,先被寫入的數(shù)據(jù)同樣在讀取的時(shí)候先被讀出,所以 FIFO存儲器沒有地址線,有一個(gè)寫端口和一個(gè)讀端口。

2023-09-07 18:30:11 819

819

上文XILINX FPGA IP之FIFO對XILINX FIFO Generator IP的特性和內(nèi)部處理流程進(jìn)行了簡要的說明,本文通過實(shí)際例子對該IP的使用進(jìn)行進(jìn)一步的說明。本例子例化一個(gè)讀數(shù)據(jù)位寬是寫數(shù)據(jù)位寬兩倍的FIFO,然后使用讀時(shí)鐘頻率:寫時(shí)鐘頻率=2:3,進(jìn)行簡單的FIFO跨時(shí)鐘域操作。

2023-09-07 18:31:35 759

759

FIFO在設(shè)計(jì)是一個(gè)非常常見并且非常重要的模塊,很多公司有成熟的IP,所以一部分人并沒有人真正研究寫過FIFO,本文僅簡述FIFO中部分值得保留的設(shè)計(jì)思路。

2023-09-11 17:05:51 356

356

異步FIFO包含"讀"和"寫“兩個(gè)部分,寫操作和讀操作在不同的時(shí)鐘域中執(zhí)行,這意味著Write_Clk和Read_Clk的頻率和相位可以完全獨(dú)立。異步FIFO

2023-09-14 11:21:45 545

545

同步FIFO和異步FIFO的區(qū)別 同步FIFO和異步FIFO各在什么情況下應(yīng)用? 1. 同步FIFO和異步FIFO的區(qū)別 同步FIFO和異步FIFO在處理時(shí)序有明顯的區(qū)別。同步FIFO相對來說是較為

2023-10-18 15:23:58 789

789 請問異步FIFO的溢出操作時(shí)怎么樣判斷的? 異步FIFO是數(shù)據(jù)傳輸?shù)囊环N常用方式,在一些儲存器和計(jì)算機(jī)系統(tǒng)中,常常會用到異步FIFO。作為一種FIFO,異步FIFO經(jīng)常面臨兩種情況:溢出

2023-10-18 15:28:41 299

299 本文將簡述一種fifo讀控制的不合理設(shè)計(jì)案例,在此案例中,異常報(bào)文將會堵在fifo中,造成頭阻塞。

2023-10-30 14:25:34 159

159

電子發(fā)燒友App

電子發(fā)燒友App

評論