在聊中斷機(jī)制之前,我想先和大家聊一聊中斷機(jī)制出現(xiàn)的前因后果。最一開始計算機(jī)操作系統(tǒng)的設(shè)計是能夠一次性的執(zhí)行所有的計算任務(wù)的,這被稱為順序執(zhí)行,也是批處理操作系統(tǒng)(Batch system)。

2023-08-07 09:18:28 843

843

ARM處理器是一種流行的處理器架構(gòu),用于許多現(xiàn)代移動設(shè)備和嵌入式系統(tǒng)中。中斷和異常是ARM處理器中的兩個重要概念,它們是處理器中斷程序執(zhí)行的關(guān)鍵機(jī)制。

2023-09-05 15:45:30 695

695

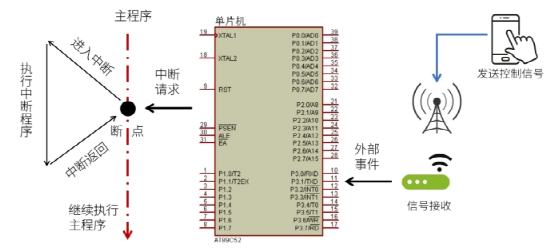

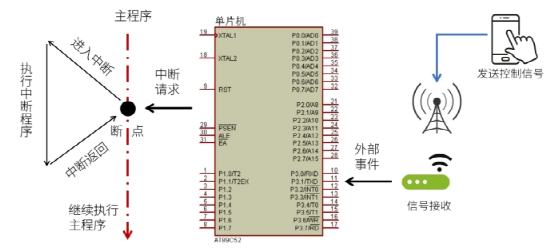

單片機(jī)多用于物聯(lián)網(wǎng)、自動控制系統(tǒng)、智能家電等領(lǐng)域,要求單片機(jī)能夠?qū)崟r響應(yīng)外部觸發(fā)的事件,中斷機(jī)制是單片機(jī)響應(yīng)外部事件的重要方法。

2023-10-31 14:46:34 880

880

慕課蘇州大學(xué).嵌入式開發(fā)及應(yīng)用.第二章.入門與軟件框架.ARM Cortex-M0+中斷機(jī)制和中斷編程步驟0 目錄2 入門與軟件框架2.7 ARM Cortex-M0+中斷機(jī)制和中斷編程步驟

2021-11-08 09:10:10

1、中斷和異常它支持16-4-1=11 種系統(tǒng)異常(同步)(保留了 4+1 個檔位),外加 240 個外部中斷輸入(異步)。在 CM3 中取消了 FIQ 的概念(v7 前的 ARM 都有這個 FIQ

2022-04-27 16:04:21

表:異常處理的大致流程主要針對中斷進(jìn)行講解,其他的類似2. 中斷異常當(dāng)手機(jī)接到一個電話時,電話模塊他會接到這個信號,電話和手機(jī)內(nèi)部的CPU通過某個管腳相連,電話模塊通過這個管教把信號發(fā)給CPU,CPU

2022-04-26 09:37:10

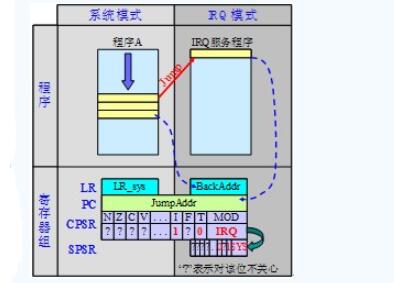

1、ARM中斷硬件機(jī)制ARM 有兩級外部中斷 FIQ,IRQ.可是大多數(shù)的基于ARM 的系統(tǒng)有 >2個的中斷源!因此需要一個中斷控制器(通常是地址映射的)來控制中斷是怎樣傳遞給ARM

2022-05-30 11:03:03

如下表:異常處理的大致流程主要針對中斷進(jìn)行講解,其他的類似2. 中斷異常當(dāng)手機(jī)接到一個電話時,電話模塊他會接到這個信號,電話和手機(jī)內(nèi)部的CPU通過某個管腳相連,電話模塊通過這個管教把信號發(fā)給CPU

2022-05-05 10:16:31

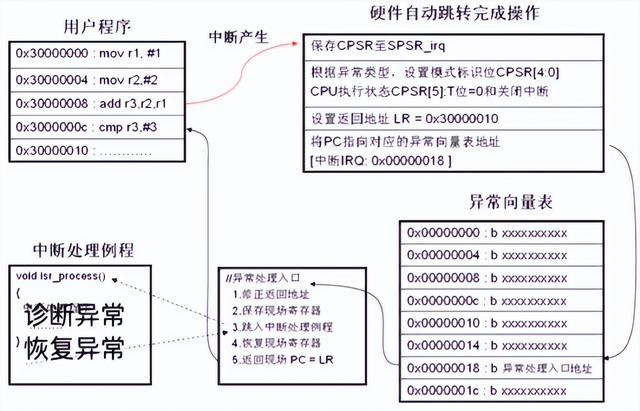

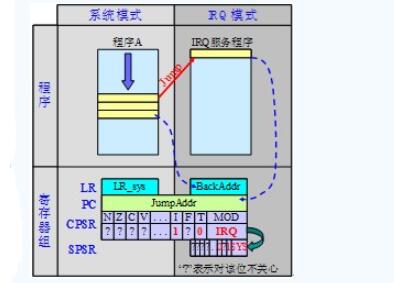

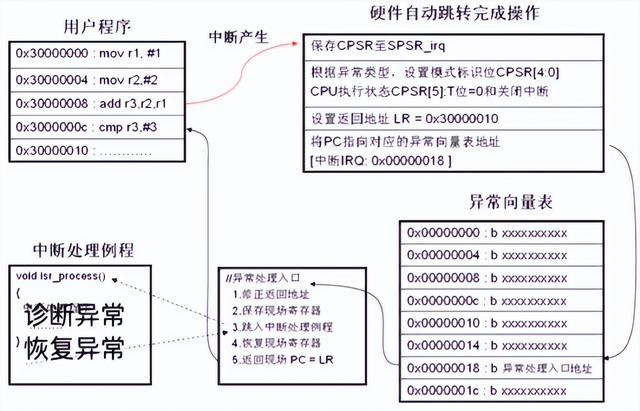

ARM處理器異常相應(yīng)過程:1、保存處理器當(dāng)前狀態(tài)、中斷屏蔽位以及各個條件標(biāo)志位。將當(dāng)前程序狀態(tài)寄存器CPSR保存到對應(yīng)的SPSR寄存器中實現(xiàn)。每個異常中斷都有對應(yīng)的物理SPSR寄存器。2、設(shè)置

2021-12-14 08:57:34

在ARM處理器中一條指令的執(zhí)行分為取指、譯碼、執(zhí)行三個階段,由于指令流水線的存在造成當(dāng)前執(zhí)行的指令的地址是PC-8(ARM指令集),那么當(dāng)前執(zhí)行指令的下一條指令的地址應(yīng)該是PC-4,所以在異常產(chǎn)生

2017-03-02 15:08:27

在ARM處理器中一條指令的執(zhí)行分為取指、譯碼、執(zhí)行三個階段,由于指令流水線的存在造成當(dāng)前執(zhí)行的指令的地址是PC-8(ARM指令集),那么當(dāng)前執(zhí)行指令的下一條指令的地址應(yīng)該是PC-4,所以在異常產(chǎn)生

2017-03-07 16:40:45

在ARM處理器中,我們常常使用SWI指令來產(chǎn)生一個軟中斷。軟中斷指令SWI指令中包含了一個24位的立即數(shù),這個立即數(shù)指示了用戶請求的特定的SWI功能,即這個立即數(shù)表示的是SWI指令所想要觸發(fā)中斷

2017-01-10 15:09:37

寄存器。以及6個32位狀態(tài)寄存器。關(guān)于寄存器這里就不詳細(xì)介紹了,有興趣的人可以上網(wǎng)找找,很多這方面的資料。異常處理當(dāng)正常的程序執(zhí)行流程發(fā)生暫時的停止時,稱之為異常,例如處理一個外部的中斷請求。在處理異常

2011-01-27 11:13:20

寄存器。以及6個32位狀態(tài)寄存器。關(guān)于寄存器這里就不詳細(xì)介紹了,有興趣的人可以上網(wǎng)找找,很多這方面的資料。異常處理當(dāng)正常的程序執(zhí)行流程發(fā)生暫時的停止時,稱之為異常,例如處理一個外部的中斷請求。在處理異常

2011-01-27 14:19:05

,#4PC+4數(shù)據(jù)中止SUBSPC,R14_abt,#8PC+8中斷處理當(dāng)外部中斷IRQ和FIQ(Fast Interrpt Request,快速中斷請求)發(fā)生時,ARM核完成一部分工作。當(dāng)然,這些

2013-05-24 10:30:42

,#4PC+4數(shù)據(jù)中止SUBSPC,R14_abt,#8PC+8中斷處理當(dāng)外部中斷IRQ和FIQ(Fast Interrpt Request,快速中斷請求)發(fā)生時,ARM核完成一部分工作。當(dāng)然,這些

2013-08-09 16:15:24

,R14_abt,#8PC+8中斷處理當(dāng)外部中斷IRQ和FIQ(Fast Interrpt Request,快速中斷請求)發(fā)生時,ARM核完成一部分工作。當(dāng)然,這些工作是任何異常發(fā)生時都必須要做的,所以

2013-04-08 10:53:07

在學(xué)習(xí)與開發(fā)ARM處理器的過程中,一個不能繞開的話題就是異常處理流程。它在ARM的體系架構(gòu)中,占據(jù)著不可動搖的重要地位。此處就以Coterx-A系列的ARM處理器簡單分析一下異常中斷處理流程。說異常

2016-11-11 09:55:57

在學(xué)習(xí)與開發(fā)ARM處理器的過程中,一個不能繞開的話題就是異常處理流程。它在ARM的體系架構(gòu)中,占據(jù)著不可動搖的重要地位。此處就以Coterx-A系列的ARM處理器簡單分析一下異常中斷處理流程。說異常

2016-10-14 16:15:42

現(xiàn)場,在從異常中斷處理程序退出時,要恢復(fù)被中斷的程序的執(zhí)行現(xiàn)場。本文討論ARM體系中的異常中斷機(jī)制。ARM體系中異常中斷種類:ARM體系中異常中斷如下面的介紹。復(fù)位(Reset):當(dāng)處理器的復(fù)位引腳有效

2020-08-28 08:09:17

ARM異常中斷返回的幾種情況異常中斷返回的幾種情況: 重要基礎(chǔ)知識:R15(PC)總是指向“正在取指”的指令,而不是指向“正在執(zhí)行”的指令或正在“譯碼”的指令。一般來說,人們習(xí)慣性約定將“正在執(zhí)行

2016-07-22 11:32:45

[學(xué)習(xí)引導(dǎo)]ARM異常中斷返回的幾種情況 異常中斷返回的幾種情況: 重要基礎(chǔ)知識:R15(PC)總是指向“正在取指”的指令,而不是指向“正在執(zhí)行”的指令或正在“譯碼”的指令。一般來說,人們習(xí)慣性

2016-03-31 16:09:03

處理器或協(xié)處理器遇見不能處理的指令時,產(chǎn)生為定義異常。可使用該異常機(jī)制進(jìn)行軟件仿真(異常向量:0x0000,0004);3、軟件中斷(優(yōu)先級6)有執(zhí)行SWI指令產(chǎn)生,可用于用戶模式下程式調(diào)用特權(quán)操作

2014-10-13 10:06:50

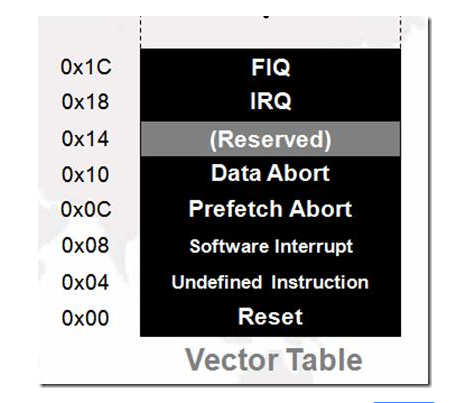

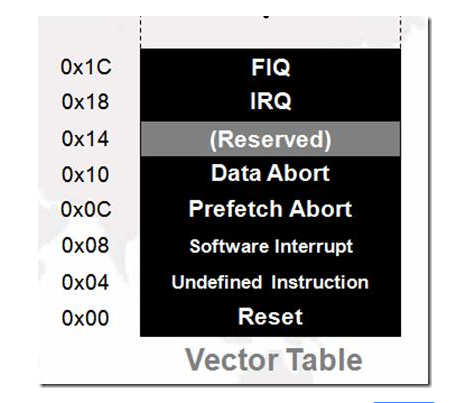

經(jīng)典ARM微處理器包括7種異常:1、 復(fù)位異常2、 未定義指令異常3、 軟件中斷異常4、 預(yù)取指令異常5、 數(shù)據(jù)異常6、 IRQ(中斷)7、 FIQ(快速中斷)異常,單片機(jī)為中斷,籠統(tǒng)來講可以把異常

2021-07-16 07:04:57

寄存器的值寫到PC寄存器中,完成恢復(fù)現(xiàn)場,繼續(xù)之前的代碼執(zhí)行。2. 異常處理機(jī)制:異常向量表是硬件提供的一種機(jī)制,在CPU設(shè)計時就定好了,當(dāng)發(fā)生中斷時就會將對應(yīng)異常向量的值加載到PC中,去執(zhí)行中斷處理函數(shù)

2022-05-17 09:42:16

0xffff00000其始的地址。默認(rèn)是以零地址開始存放的。可能有些同學(xué)還是有些暈,我們來舉個例子說明一下。例如:ARM處理器正在執(zhí)行指令,此時外部硬件產(chǎn)生了一個中斷。此時將產(chǎn)生IRQ異常,然后ARM核

2020-04-20 10:52:02

關(guān)于藍(lán)牙安全機(jī)制的研究,不看肯定后悔

2021-05-26 06:24:05

INtime RTOS內(nèi)部的關(guān)鍵處理機(jī)制是什么?INtime RTOS內(nèi)部的關(guān)鍵處理機(jī)制有哪些相關(guān)的應(yīng)用案例?

2021-09-29 06:28:48

RISC-V對于異常處理的實現(xiàn)復(fù)雜嗎?應(yīng)該沒有ARM Cortex系列的那樣復(fù)雜,有NVIC或GIC中斷控制器吧。那么它執(zhí)行異常處理的流程是怎樣的?

2023-04-21 15:00:56

程序中存在兩個中斷,一個是定時器下溢中斷,另一個是XINT1中斷。XINT1中斷的優(yōu)先級高于定時器下溢中斷。疑問:當(dāng)定時器下溢中斷正在執(zhí)行時,并且還沒有執(zhí)行完,這是如果XINT1中斷突然到來,cpu會響應(yīng)XINT1中斷嗎?還是等定時器下溢中斷的程序執(zhí)行完,然后再響應(yīng)XINT1中斷程序?

2016-02-16 18:22:29

方面的操作和寄存器等相關(guān)操作。中斷差不多就是就這樣,關(guān)于異常的處理其實和上述中斷中斷處理機(jī)制差不多,再次就不贅余了。

2015-11-06 12:04:49

,R14_abt,#8PC+8中斷處理當(dāng)外部中斷IRQ和FIQ(Fast Interrpt Request,快速中斷請求)發(fā)生時,ARM核完成一部分工作。當(dāng)然,這些工作是任何異常發(fā)生時都必須要做的,所以

2015-07-27 15:31:14

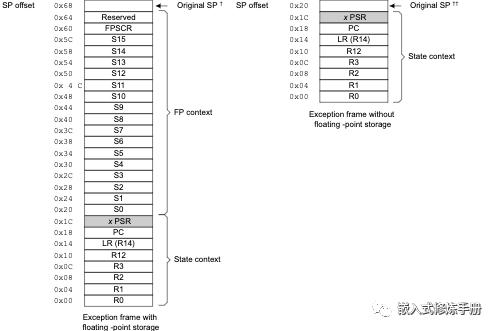

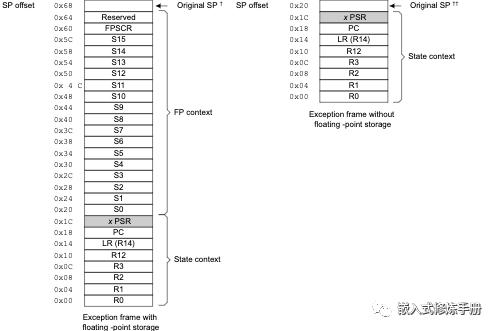

執(zhí)行中斷前的程序。自動保存和恢復(fù)寄存器內(nèi)容的操作被稱為“壓棧”和“出棧”,這種機(jī)制使得異常處理可以跟普通的C函數(shù)一樣處理,同時也減小了軟件開銷以及回路大小,因此也降低了系統(tǒng)的功耗。3、異常返回指令根據(jù)

2021-10-11 10:15:51

,R14_abt,#8PC+8中斷處理當(dāng)外部中斷IRQ和FIQ(Fast Interrpt Request,快速中斷請求)發(fā)生時,ARM核完成一部分工作。當(dāng)然,這些工作是任何異常發(fā)生時都必須要做的,所以

2013-03-22 16:20:47

,R14_abt,#8PC+8中斷處理當(dāng)外部中斷IRQ和FIQ(Fast Interrpt Request,快速中斷請求)發(fā)生時,ARM核完成一部分工作。當(dāng)然,這些工作是任何異常發(fā)生時都必須要做的,所以

2013-03-22 16:34:17

復(fù)制到發(fā)生的異常模式下SPSR中; b.模式切換:將CPSR模式位強(qiáng)制設(shè)置為與異常類型相對應(yīng)的值,同時處理器進(jìn)入到ARM執(zhí)行模式,禁止所有IRQ中斷,當(dāng)進(jìn)入FIQ快速中斷模式時禁止FIQ中斷; c.

2018-05-10 10:58:33

單片機(jī)的中斷處理機(jī)制什么是中斷?為什么要使用中斷(中斷的特點)什么是中斷源?中斷源有哪些中斷機(jī)制的流程中斷優(yōu)先級多個中斷同時發(fā)生什么是中斷?當(dāng)CPU執(zhí)行程序時,由于發(fā)生了某種隨機(jī)的事件(內(nèi)部或外部

2021-12-07 11:14:46

在介紹基于三星exynos4412型號芯片的中斷處理之前,我們需要先做的是理解arm的異常處理機(jī)制,然后在這個基礎(chǔ)之上去學(xué)習(xí)三星的exynos4412芯片的中斷處理。其實exynos4412

2018-05-15 13:49:54

基于stm32串口環(huán)形緩沖隊列處理機(jī)制是什么

2021-12-08 07:06:56

關(guān)于異常處理,分為三部分:ARM異常和模式:core處理異常時的操作,幾種模式介紹。Vector table:異常優(yōu)先級lr偏移:幾種異常如何返回異常和中斷處理簡介在嵌入式系統(tǒng)中異常處理是核心之一

2021-12-14 09:23:07

寄存器指令集中斷、異常處理機(jī)制

2021-01-13 07:56:22

表的最末端,異常處理不需要跳轉(zhuǎn)FIQ 比 IRQ 多5個私有的寄存器(r8-r12),在中斷操作時,壓棧出棧操作的少。三、異常發(fā)生的硬件操作異常發(fā)生后,ARM核的操作步驟可以總結(jié)為4大步3小步。4大步3

2022-08-18 15:26:04

一、異常分類 異在ARM里,中斷有三種,IRQ、FIQ、Software Interrupt;中斷是屬于異常的。包含中斷在內(nèi)的異常一共有8種。 (一)reset:重啟異常: 該異常會讓模式

2022-04-26 09:29:21

嵌入式實時操作系統(tǒng)VxW0rks提供的中斷處理機(jī)制中斷延遲小.應(yīng)用編程方便。MPC860是目前在網(wǎng)絡(luò)與通信領(lǐng)域應(yīng)用非常廣泛的一款微處理器芯片。論文詳細(xì)分析了VxWorks及MPC860的中斷處

2008-12-16 14:15:35 5

5 嵌入式實時操作系統(tǒng)VxWorks提供的中斷處理機(jī)制中斷延遲小,應(yīng)用編程方便。MPC860是目前在網(wǎng)絡(luò)與通信領(lǐng)域應(yīng)用非常廣泛的一款微處理器芯片。論文詳細(xì)分析了VxWorks及MPC860的中斷處理

2009-06-10 14:08:41 12

12 對工作流的異常和案例推理(Case - Based Reasoning,簡稱CBR)的機(jī)制進(jìn)行了介紹,給出了一個應(yīng)用CBR 技術(shù)進(jìn)行異常處理的工作流模型,并研究了應(yīng)用CBR 方法處理工作流異常的機(jī)制。

2009-06-15 10:20:46 14

14 傳統(tǒng)的Java異常-捕獲機(jī)制已不能滿足當(dāng)今大型企業(yè)級開發(fā)的要求。本文對Struts2提供的異常處理機(jī)制進(jìn)行了研究和擴(kuò)展,提出將檢查型(Checked)異常轉(zhuǎn)化為非檢查型(Unchecked)異常

2009-06-18 08:19:24 27

27 通過基于立宇泰S3C44B0X 開發(fā)板的BSP 移植調(diào)試,闡述了VxWorks 的異常中斷處理機(jī)制,實現(xiàn)了VxWorks 基于S3C44B0X 處理器的中斷處理,并以外部中斷EINT4/5/6/7為例分析了中斷的響應(yīng)過程,

2009-09-03 11:25:12 17

17 嵌入式實時操作系統(tǒng)VxW0rks提供的中斷處理機(jī)制中斷延遲小.應(yīng)用編程方便。MPC860是目前在網(wǎng)絡(luò)與通信領(lǐng)域應(yīng)用非常廣泛的一款微處理器芯片。論文詳細(xì)分析了VxWorks及MPC860的中斷

2009-11-28 16:32:46 15

15 提出了一種在iFix 組態(tài)軟件中創(chuàng)建消息隊列的方法,利用這種消息隊列實現(xiàn)了對控制命令的執(zhí)行情況的跟蹤與處理。這種基于隊列的命令處理機(jī)制確保了組態(tài)軟件的控制命令能夠

2009-12-23 14:06:15 22

22 嵌入式實時操作系統(tǒng)VxW0rks提供的中斷處理機(jī)制中斷延遲小.應(yīng)用編程方便。MPC860是目前在網(wǎng)絡(luò)與通信領(lǐng)域應(yīng)用非常廣泛的一款微處理器芯片。論文詳細(xì)分析了VxWorks及MPC860的中斷處

2010-01-09 15:09:51 40

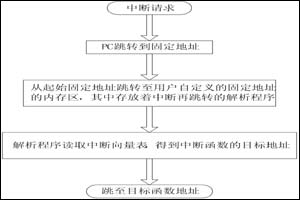

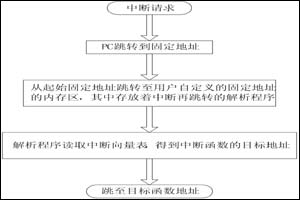

40 摘要:本文首先簡要概述了ARM處理器的異常中斷種類、響應(yīng)和返回過程;然后重點討論了中斷解析程序的原理和實現(xiàn),并分別給出了普通中斷和向量中斷的處理示例流程圖和詳細(xì)

2006-03-11 12:18:54 760

760

Cortex-M3的異常處理機(jī)制分析

詳細(xì)闡述CortexM3異常的分類、優(yōu)先級、進(jìn)入和退出,以及在CortexM3異常處理機(jī)制中使用的新技術(shù)——遲到(late?arriving)和

2009-03-29 15:07:38 1780

1780

對ARM處理器的普通中斷處理、任務(wù)切換中斷處理、可重人中斷處理和基于優(yōu)先級的可重人性中斷處理的上下文保存技術(shù)進(jìn)行分析與總結(jié)。為保證理論的正確性,核心的程序代碼都經(jīng)過了

2011-07-06 12:08:09 4166

4166

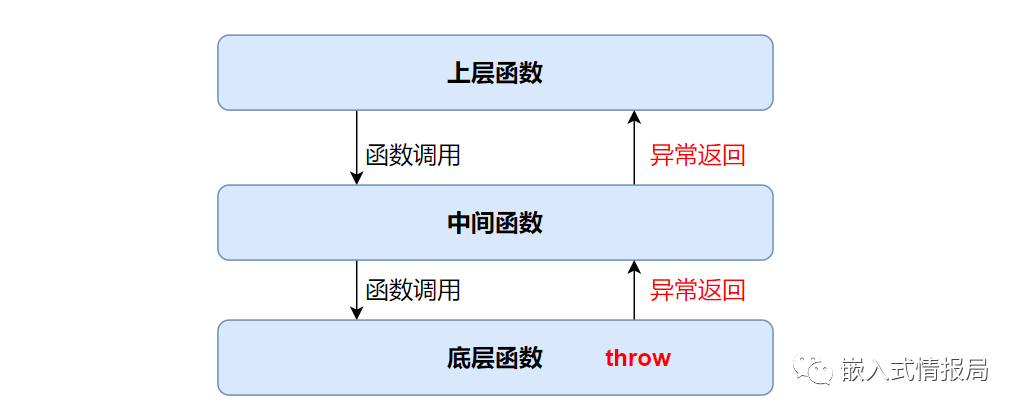

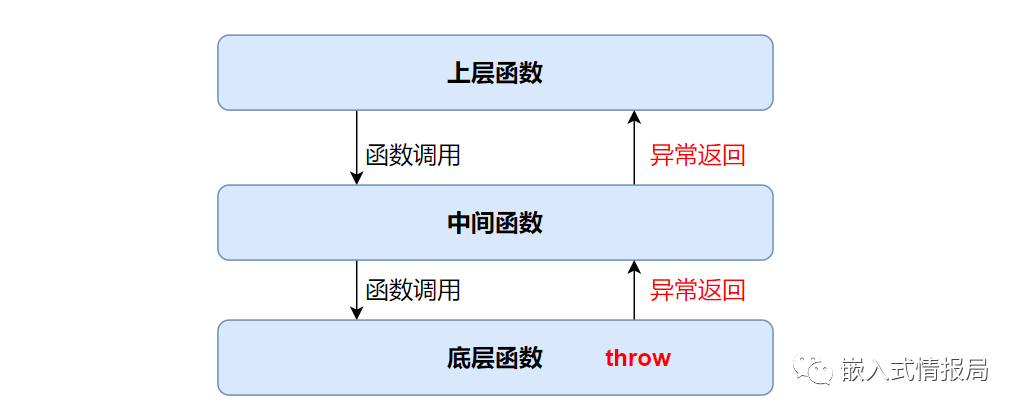

C++的異常機(jī)制為我們提供了更好的解決方法。異常處理的基本思想是:當(dāng)出現(xiàn)錯誤時拋出一個異常,希望它的調(diào)用者能捕獲并處理這個異常。

2011-11-23 11:04:47 3314

3314

嵌人式微處理器的應(yīng)用設(shè)計中,中斷處理通常是系統(tǒng)的核心任務(wù)之一。ARM 作為嵌入式微處理器的典型代表,為保證系統(tǒng)的實時性和穩(wěn)定性,建立了一套完整的異常處理機(jī)制。ARMTTDMI內(nèi)核

2011-12-01 15:51:10 0

0 VxWorks提供的中斷處理機(jī)制延遲小,符合實時性要求。文中分析了基于Powerpc440處理器的中斷處理機(jī)制,并詳細(xì)闡述了中斷處理的編程過程。

2012-01-10 17:22:18 30

30 TTNT數(shù)據(jù)鏈?zhǔn)瞻l(fā)機(jī)消息處理機(jī)制的MATLAB仿真

2016-01-04 14:59:05 0

0 ARM體系中的異常中斷及其應(yīng)用

2017-09-22 16:51:52 4

4 基于ARM Cortex-M4的MQX中斷機(jī)制分析與中斷程序框架設(shè)計

2017-09-25 08:29:38 6

6 3.4 異常中斷處理 異常或中斷是用戶程序中最基本的一種執(zhí)行流程和形態(tài)。這部分主要對ARM架構(gòu)下的異常中斷做詳細(xì)說明。 ARM有7種類型的異常,按優(yōu)先級從高到低的排列如下:復(fù)位異常(Reset

2017-10-18 13:29:56 1

1 引言 CortexM3是ARM公司第一款基于ARMv7M的微控制器內(nèi)核,在指令執(zhí)行、異常控制、時鐘管理、跟蹤調(diào)試和存儲保護(hù)等方面相對于 ARM7有很大的區(qū)別。尤其在異常處理機(jī)制方面有很大的改進(jìn)

2017-11-30 09:23:09 649

649

嵌入式系統(tǒng)要求對異常及中斷處理器能快速響應(yīng)。文中分析了ARM體系結(jié)構(gòu)下 異常處理 特點,提出一種基于 ARM處理器 的高效異常處理解決方案,以LPC3250硬件平臺為基礎(chǔ),對該方案進(jìn)行了設(shè)計與實現(xiàn)

2018-02-03 03:38:01 1139

1139

本文介紹A了RM S3C4510B系統(tǒng) 的 異常中斷 機(jī)制,包括異常中斷的分類,響應(yīng)與返回;中斷處理程序的安裝與調(diào)用;SWI,IRQ中斷的實例與關(guān)鍵代碼。隨著人們對于電子產(chǎn)品的要求越來越高

2018-02-03 05:32:01 1561

1561

ARM單片機(jī)是大多數(shù)新手選擇的入門切入點,但由于知識的不足,在設(shè)計過程中新手們經(jīng)常會遇到這樣或那樣的問題,ARM異常中斷返回就是這樣一種令人頭疼的問題。在ARM的使用問題中異常中斷返回是新手們較為苦惱的問題,本文就將對ARM異常中斷的集中情況進(jìn)行總結(jié),并給出了一些解決方法。

2018-02-08 09:29:45 6187

6187

CortexM3是ARM公司第一款基于 ARMv7M 的微控制器內(nèi)核,在指令執(zhí)行、異常控制、時鐘管理、跟蹤調(diào)試和存儲保護(hù)等方面相對于 ARM7有很大的區(qū)別。尤其在 異常處理機(jī)制 方面有很大的改進(jìn)

2018-04-17 12:54:00 1535

1535

編寫異常處理代碼的建議 如果你寫方法時沒辦法處理未知意外情況,可以考慮在方法的聲明中用throws關(guān)鍵字把檢查型異常傳播出去,強(qiáng)制要求客戶端程序員自己來處理這中意外情況(缺點: 增加客戶端程序員

2018-03-26 11:44:52 6

6 異常中斷通常用在下面幾種情況: 1、系統(tǒng)加電時 2、系統(tǒng)復(fù)位時 3、跳轉(zhuǎn)到復(fù)位中斷向量處執(zhí)行,稱為軟復(fù)位 未定義的指令 當(dāng)ARM處理器或者是系統(tǒng)中協(xié)處理器認(rèn)為當(dāng)前指令未定義時,產(chǎn)生未定義指令異常中斷。可以通過該異常中斷機(jī)制仿真浮點向量運算。

2018-04-05 10:51:00 1148

1148 以前,我一直很疑惑這個“ ARM異常 、 中斷以 及他們的 向量表 ”是怎么回事,他們到底是怎么實現(xiàn)的,沒有想到今天偶然看到(ARM System Developers Guide

2018-06-14 10:34:00 3975

3975

關(guān)于各種中斷在中斷返回時還需要給LR減去一個不同的偏移量的問題我覺得沒必要深入研究了,這還要涉及到ARM指令的流水線技術(shù),平時寫中斷代碼都是用C寫的,沒必要知道這個。用到時再去查表即可。

2018-08-27 17:45:34 18582

18582

器核的接口緊密相連,可以實現(xiàn)低延遲的中斷處理和有效處理地處理晚到的中斷。嵌套向量中斷控制器管理著包括核異常等中斷。

2018-11-16 15:35:40 7627

7627

本文檔的詳細(xì)介紹的是Java程序設(shè)計教程之異常處理的詳細(xì)資料說明主要內(nèi)容包括了:1 什么是異常,2異常處理機(jī)制,3異常的處理,4 創(chuàng)建用戶異常類

2019-02-22 10:27:55 13

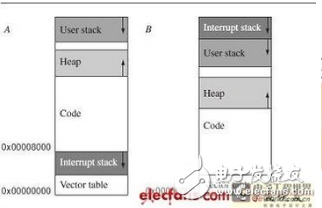

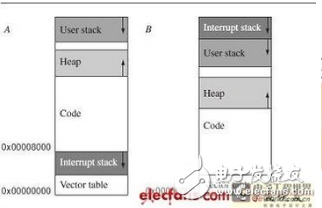

13 ARM體系結(jié)構(gòu)中,存在7種異常處理。當(dāng)異常發(fā)生時,處理器會把PC設(shè)置為一個特定的存儲器地址。這一地址放在被稱為向量表(vector table)的特定地址范圍內(nèi)。向量表的入口是一些跳轉(zhuǎn)指令,跳轉(zhuǎn)到專門處理某個異常或中斷的子程序。

2019-03-20 10:25:32 7

7 研究了ARM核處理器S3C4510B 的中斷異常處理機(jī)制和啟動代碼的任務(wù)及運行過程。分析了在REMAP(存儲系統(tǒng)重映射) 情況下中斷向量設(shè)置、存儲系統(tǒng)配置、堆棧初始化、代碼拷貝、應(yīng)用程序運行環(huán)境

2019-10-12 16:44:03 11

11 當(dāng)ARM處理器或協(xié)處理器遇見不能處理的指令時,產(chǎn)生為定義異常。可使用該異常機(jī)制進(jìn)行軟件仿真(異常向量:0x0000,0004);

2019-10-24 15:52:18 3426

3426 STM32Cube HAL庫中斷處理機(jī)制,以及回調(diào)函數(shù)實現(xiàn)原理

2020-03-03 14:01:55 12409

12409 當(dāng)ARM異常中斷發(fā)生時,系統(tǒng)執(zhí)行完當(dāng)前指令后,將跳轉(zhuǎn)到相應(yīng)的異常中斷處理程序處執(zhí)行。當(dāng)異常中斷處理程序執(zhí)行完成后,程序返回到發(fā)生中斷指令的下條指令處執(zhí) 行。在進(jìn)入異常中斷處理程序時,要保存被中斷程序的執(zhí)行現(xiàn)場,從異常中斷處理程序退出時,要恢復(fù)被中斷程序的執(zhí)行現(xiàn)場。

2020-06-17 10:05:12 7044

7044 對于我們所開發(fā)的程序而言,錯誤是無法避免的。本文闡述了如何運用java的異常處理機(jī)制為我們控制和處理異常的出現(xiàn),從而保證程序的安全性和可用性。

2020-07-08 16:14:08 19

19 關(guān)于“進(jìn)入異常”:在異常發(fā)生后,ARM7TDMI內(nèi)核會作以下工作:

2020-07-21 09:10:32 2485

2485

外部中斷請求(IRQ) 當(dāng)處理器的外部中斷請求引腳有效,而且CPSR的寄存器的I控制位被清除時,處理器產(chǎn)生外部中斷請求異常中斷。系統(tǒng)中個外設(shè)通過該異常中斷請求處理服務(wù)。

2020-08-27 14:21:29 2354

2354 電子發(fā)燒友網(wǎng)為你提供總結(jié):ARM的異常處理機(jī)制分析資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-15 08:45:10 7

7 異常是能夠引起程序流偏離正常流程的事件,當(dāng)異常發(fā)生時,正在執(zhí)行的程序就會被掛起,處理器轉(zhuǎn)而執(zhí)行一塊與該事件相關(guān)的代碼(異常處理)。事件可以是外部輸入,也可以是內(nèi)部產(chǎn)生的,外部產(chǎn)生的事件通常被稱作中斷

2021-10-12 17:14:18 4165

4165 慕課蘇州大學(xué).嵌入式開發(fā)及應(yīng)用.第二章.入門與軟件框架.ARM Cortex-M0+中斷機(jī)制和中斷編程步驟0 目錄2 入門與軟件框架2.7 ARM Cortex-M0+中斷機(jī)制和中斷編程步驟

2021-11-03 13:51:01 10

10 單片機(jī)的中斷處理機(jī)制什么是中斷?為什么要使用中斷(中斷的特點)什么是中斷源?中斷源有哪些中斷機(jī)制的流程中斷優(yōu)先級多個中斷同時發(fā)生什么是中斷?當(dāng)CPU執(zhí)行程序時,由于發(fā)生了某種隨機(jī)的事件(內(nèi)部或外部

2021-11-24 16:21:08 2

2 一:中斷概述中斷是指在CPU正常運行期間,由于內(nèi)外部事件或由程序預(yù)先安排的事件引起的CPU暫時停止正在運行的程序,轉(zhuǎn)而為該內(nèi)部或外部事件或預(yù)先安排的事件服務(wù)的程序中去,服務(wù)完畢后再返回去繼續(xù)運行被暫時中斷的程序。中斷類型:...

2021-11-30 18:06:04 13

13 那么C++設(shè)計了一套異常處理機(jī)制,一方面能夠使得異常處理和正常運行代碼進(jìn)行分離,使得程序更加模塊化;另一方面,C++的異常處理可以不需要異常處理在異常發(fā)生時的同一個函數(shù),而是可以在更上層合適的位置進(jìn)行處理。

2023-02-21 10:37:02 525

525

如果異常的優(yōu)先級高于當(dāng)前執(zhí)行優(yōu)先級,則可以先發(fā)制人當(dāng)前執(zhí)行。 當(dāng)一個異常優(yōu)先于另一個異常時,這些異常被稱為嵌套異常。

2023-07-24 09:57:38 1131

1131

正確處理,處理器可能會崩潰或數(shù)據(jù)損毀。ARM處理器有七種異常模式,即:重置模式、用戶模式、FIQ模式、IRQ模式、監(jiān)督模式、中斷模式和異常模式。 1. 重置模式 當(dāng)ARM處理器啟動時,它將進(jìn)入重置模式。在這種模式下,處理器處于其最初狀態(tài)

2023-09-05 16:22:25 2036

2036 當(dāng)異常中斷發(fā)生時,程序?qū)?dāng)前執(zhí)行指令的下一條指令的地址存入新的異常模式的鏈接寄存器LR中(R14_<mode>),以便程序在異常處理完后,能正確返回原程序。

2023-10-18 17:25:43 302

302 arm處理器有哪些中斷源?arm處理器對異常中斷的響應(yīng)過程? ARM處理器是一種廣泛使用的嵌入式處理器,運行著各種不同類型的應(yīng)用程序。為了保證應(yīng)用程序的穩(wěn)定性和正確性,ARM處理器需要在遇到異常

2023-10-19 16:35:59 675

675 機(jī)制。ARM處于操作系統(tǒng)和硬件之間,因此異常處理機(jī)制在有效性、安全性、可靠性方面必須經(jīng)過充分測試和驗證。 ARM異常指令是程序中不受控制的分支或其他例外情況,如硬件故障、訪問非法地址、非法指令、軟件中斷等。雖然大多處理器都有異常響應(yīng)和處理

2023-10-19 16:36:05 454

454 ARM中的異常中斷是如何實現(xiàn)進(jìn)入中斷程序的?如何進(jìn)入呢? 在計算機(jī)系統(tǒng)中,異常和中斷是兩個常見的概念。 在ARM中,異常和中斷的主要目的是幫助處理器響應(yīng)與系統(tǒng)操作相關(guān)的事件。 由于處理器必須同時執(zhí)行

2023-10-19 16:36:11 481

481 電子發(fā)燒友網(wǎng)站提供《基于ARM核的嵌入式系統(tǒng)異常處理機(jī)制的設(shè)計.pdf》資料免費下載

2023-10-27 09:00:49 0

0 可通過以下幾種不同的錯誤處理機(jī)制進(jìn)行參數(shù)跟蹤或編程或訪問錯誤

2023-11-25 11:35:23 784

784

ARM中斷的實現(xiàn)是通過中斷控制器和異常模式實現(xiàn)的。ARM處理器通過中斷控制器來接收和處理外部的中斷信號,而異常模式用于處理內(nèi)部的異常事件。本文將詳細(xì)介紹ARM中斷的原理和實現(xiàn)方式。 一、ARM中斷

2024-01-05 15:18:11 206

206

正在加载...

電子發(fā)燒友App

電子發(fā)燒友App

評論