像ARM926EJ 和ARM946E這兩個最常見的ARM9E處理器中,都帶有一套存儲器子系統,以提高系統性能和支持大型操作系統。如圖2所示,一個存儲器子系統包含一個 MMU(存儲器管理單元)或MPU

2018-05-21 08:57:29 6924

6924 ARM-CP15協處理器 ARM處理器使用協處理器15(CP15)的寄存器來控制cache、TCM和存儲器管理。CP15的寄存器只能被MRC和MCR(Move to Coprocessor from

2020-10-29 10:41:07 3506

3506

之前我們在學習MMU的時候, **知道這個內存的分配和CP15協處理器** 。這里先介紹一下CP15寄存器以及訪問CP15寄存器的匯編指令。

2023-09-08 17:50:52 890

890

ARM架構通過支持協處理器來擴展處理器的功能。ARM架構的處理器支持最多16個協處理器,通常稱為CP0~CP15。下述的協處理器被ARM用于特殊用途。

2023-10-31 16:07:40 562

562

ARM720T是一款通用的32位微處理器,具有8KB的高速緩存、擴大的寫入緩沖區和內存管理單元(MMU),組合在一個芯片中。ARM720T中的CPU是ARM7TDMI。ARM720T是與ARM處理器

2023-08-02 11:36:56

ARM946E-S是一款可合成處理器,結合了ARM9E-S? 具有可配置存儲器系統的處理器核心。它是ARM9E的成員? 高性能32位片上系統處理器解決方案系列。

ARM946E-S是哈佛體系結構

2023-08-02 10:17:36

(AXI),用于支持優先級的二級接口

多處理器實現

?九級管道

?帶返回堆棧的分支預測

?低中斷延遲

?外部協處理器接口和協處理器CP14和CP15

?可選的指令和數據存儲器保護單元(MPU)

?可選的指令

2023-08-02 09:15:45

14和CP15

?矢量浮點(VFP)協處理器支持

?外部協處理器接口

?使用MicroTLB管理的指令和數據存儲器管理單元(MMU)

由統一的主TLB支持的結構

?指令和數據緩存,包括具有

2023-08-02 10:30:50

9TDMI處理器核心是一種哈佛體系結構的設備,使用由Fetch、Decode、Execute、Memory和Write階段組成的五級流水線實現。它可以作為一個獨立的核心提供,可以嵌入到更復雜的設備中。獨立內核有一個

2023-08-02 13:05:00

對調試信道的訪問。CP15:系統控制處理器,提供 16 個額外寄存器來配置與控制緩存、MMU、系統保 護、時鐘模式及其他系列選項。 ARM920T 處理器的主要特征如下。ARM9TDMI 內核,ARM

2019-09-26 09:43:55

300MHz。ARM9E 系列微處理器主要應用于下一代無線設備、數字消費品、成像設備、工業控制、 存儲設備和網絡設備等領域。ARM9E 系列微處理器包含 ARM926EJ-S、ARM946E-S 和 ARM966E-S 三種類型,以適 用于不同的應用場合。

2019-09-26 09:36:52

請問: S3C2440可以通過設置/清除CP15協處理器的寄存器1的bit13來設置高端/低端異常向量地址,我從網上看到說也可以通過硬件電路控制,但是我一直沒有查到硬件如何配置???我想了解下,謝謝誰來解惑,

2019-04-25 07:45:05

寄存器中,并且把高24位清零LDRH:將一個16位的數據送到寄存器中,并且把高16位清零STR:從源寄存器32位存入到存儲器中,和前幾個指令相比是不清零協處理器指令CDP:用于ARM處理器通知ARM協

2022-04-12 10:36:38

(und):當未定義的指令執行時進入該模式,可用于支持硬件協處理器的軟件仿真。 更多的ARM處理器開發板應用,請關注深圳電子 :http://shop57047166.taobao.com [/url

2014-03-20 11:15:00

ARM微處理器支持7種運行模式,分別如下。 用戶模式(usr):ARM處理器正常的程序執行狀態。 快速中斷模式(fiq):用于高速數據傳輸或通道處理。 外部中斷模式(irq):用于通用的中斷處理

2014-10-13 10:08:55

0000。 4. ARM啟動代碼設計 ARM啟動代碼直接面對處理器內核和硬件控制器進行編程,一般使用匯編語言。啟動代碼一般包括: 中斷向量表 初始化存儲器系統 初始化堆棧初始化有特殊要求的端口

2020-11-17 16:13:49

ARM處理器狀態ARM微處理器的工作狀態一般有兩種,并可在兩種狀態之間切換:第一種為ARM狀態,此時處理器執行32位的字對齊的ARM指令;第二種為Thumb狀態,此時處理器執行16位的、半字對齊

2011-01-27 11:13:20

ARM處理器狀態ARM微處理器的工作狀態一般有兩種,并可在兩種狀態之間切換:第一種為ARM狀態,此時處理器執行32位的字對齊的ARM指令;第二種為Thumb狀態,此時處理器執行16位的、半字對齊

2011-01-27 14:19:05

(32位)數據,從第四個字節到第七個字節放置第二個存儲的字數據,一次排列。作為32位的微處理器,arm體系結構所支持的最大尋址空間為4GB。存儲器格式1、大端格式:高字節在低地址,低字節在高地址;2、小端

2017-11-06 10:43:47

32位的微處理器,arm體系結構所支持的最大尋址空間為4GB。存儲器格式1、大端格式:高字節在低地址,低字節在高地址;2、小端格式:高字節在高地址,低字節在低地址。指令長度Arm微處理器的指令長度是32位

2017-10-12 11:30:08

32位的微處理器,arm體系結構所支持的最大尋址空間為4GB。 存儲器格式1、大端格式:高字節在低地址,低字節在高地址;2、小端格式:高字節在高地址,低字節在低地址。 指令長度Arm微處理器的指令長度

2017-10-25 16:55:35

ARM處理器都是RISC結構,單周期操作,指令流水線,使用加載或存儲指令訪問內存。ARM7采用馮-諾依曼結構,3級流水線;ARM9采用哈佛結構,5級流水線;Cortex-A15采用13級流水線

2021-12-21 07:16:24

Memory ordering為了提高指令執行速度,最新的arm處理器不再one bye one的執行指令,采取了一系列的措施來提高指令執行速度,包括重排序指令、存儲訪問方式(cache

2022-04-22 09:36:08

ARM處理器模式和ARM處理器狀態有何區別?

2022-11-01 15:15:13

CPU是計算機/微控制器的核心,進行算數/邏輯運算MCU?MicroController Unit 微控制器是一個完整的計算機系統,在單個芯片上包含了處理器、存儲器和所有的外設IO模塊。MCU包含

2021-11-03 07:12:01

人士的面前。ARM這家不生產芯片卻也能數錢數到手抽筋的公司到底有著怎樣的發展史。今天小編,就帶大伙一探究竟,其中包括ARM處理器的詳細介紹。 ARM發展史 1978年12月5日,物理學家赫爾曼·豪澤

2016-12-16 19:24:17

位決定處理器的工作模式,如表所示。3)其他位 程序狀態寄存器的其他位保留,用作以后的擴展。 ARM核工作在用戶模式,R0~R15可用。 存儲器格式 ARM體系結構將存儲器看作是從零地址開始的字節

2018-07-06 07:59:05

處理器內核二、經典ARM處理器編程模型三、Cortex-M4處理器四、STM32F407芯片簡潔一、ARM處理器特點1.ARM處理器主要特點(1)ARM7系列采用馮諾依曼結構(輸入輸出、控制器、存儲器、處理器),ARM9~11采用哈佛體系結構(存儲器分為程序存儲器和數據存儲器)(2)屬于RISC型處理器結

2021-12-13 07:18:29

時的實現工藝。容易實現高性能。RISC體系結構的簡單性、有效性很容易設計出低成本、高性能的處理器。RISC技術的歷史貢獻在計算機設計技術的發展變化中,20世紀60年代初引入的虛擬存儲器、Cache和流水線

2022-04-24 10:02:29

首先來了解 ARM 體系結構中的字長。字(Word),在 ARM 體系結構中,字的長度為 32 位,而在 8 位/16 位處理器體系結構中,字的長度一般為 16 位。半字(Half Word),在

2019-09-27 09:37:35

一、ARM七種處理器工作模式:用戶模式 usr:正常程序執行模式快速中斷模式FIQ:用于高速數據傳輸和通道處理外部中斷模式IRQ:用于通常的中斷處理管理模式svc:供操作系統使用的一種保護模式

2021-07-16 06:52:30

1、ARM微處理器指令系統ARM指令集可以分為跳轉指令、數據處理指令、程序狀態寄存器傳輸指令、Load/Store指令、協處理器指令和異常中斷產生指令。根據使用的指令類型不同,指令的尋址方式分為

2022-04-26 10:30:57

2.ARM微處理器的指令系統ARM微處理器的指令集是加載/存儲型的,即指令集僅能處理寄存器中的數據,而且處理結果都要放回寄存器中,而對系統存儲器的訪問則需要通過專門的加載/存儲指令來完成。ARM

2021-12-20 06:54:28

體系結構中,字節的長度為8位。2. ARM處理器存儲格式ARM體系結構將存儲器看作是從0地址開始的字節的線性組合。作為32位的微處理器,ARM體系結構所支持的最大尋址空間為4GB。ARM體系結構可以用

2022-04-13 12:08:30

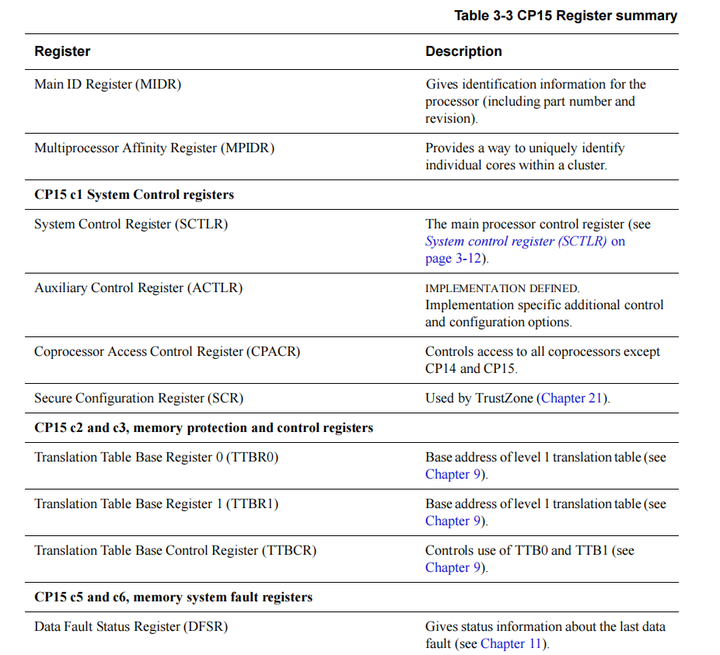

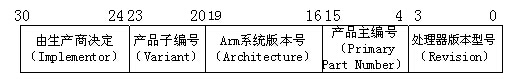

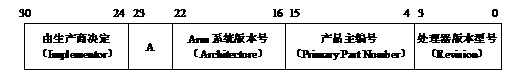

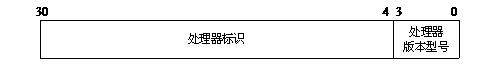

ARM核心通過兩種機制進行識別。

第一種是通過系統控制協處理器的寄存器0,也稱為協處理器15或CP15。

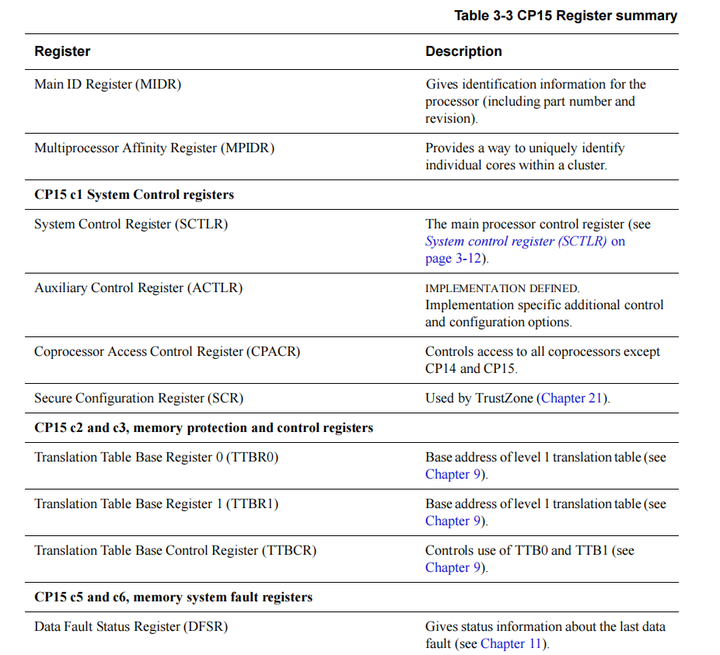

CP15僅在包含MMU或MPU的處理器內核上可用,并包含多個配置寄存器(實際數量取決于內核

2023-08-23 06:55:04

[table][tr][td=670][table][tr][td]arm處理器本身所產生的地址為虛擬地址,每一個arm芯片內都有存儲器,而這個芯片內的存儲器的地址為物理地址。我們寫程序的目的是為了

2014-03-24 11:57:18

,集成了一個被稱為 CP15 的協處理器,該協處理器的 C2 寄存器中用于保存頁表的基地址,下面以一級頁表變換為例說明 MMU 實現地址變換的過程。4 、節訪問的轉換過程節和大頁是支持允許只用一個

2020-10-23 15:29:49

CP15 - STANDARD CAPACITANCE TVS ARRAY - Protek Devices

2022-11-04 17:22:44

記憶“1/0”能記憶 1 位“1/0”數據的電子單元,稱之為存儲元,計算機中的存儲器通常將每8 個這樣的存儲元組成一個單元,稱之為字節,字節是處理器訪問存儲器的最小單位。ARM 處理器對存儲器空間

2022-04-29 16:41:53

ARM的MMU主要實現什么功能?協處理器cp15主要主要實現何功能?簡述MMU使能時存儲訪問過程

2021-03-16 07:57:10

第一套在8086的微計算機系統中,存儲器是如何組織的?是如何與處理器總線連接的?#BHE信號起什么作用?答:8086 為 16 位處理器,可訪問 1M 字節的存儲器空間;1M 字節的存儲器分為兩個

2021-07-26 06:06:49

想了解常見的arm處理器里面,哪些系列用了具體的哪些技術。比如m0-m4猜測都是第一種方式。那m7呢?r系列呢?a系列呢?

2022-08-31 14:49:23

字處理器內核(The VLIW core)、一個可編程位流協處理器(The VLx)、視頻濾波協處理器(VF)、片內存儲器、顯示刷新控制器(DRC)和大量可用的數字I/O接口組成。 BSP-15支持

2018-11-27 11:49:31

ARM Cortex-M33處理器的五大特色

2021-01-29 07:35:54

DSP的五大發展趨勢雙SHARC+內核加Cortex-A5,提升工業和實時音頻處理性能單片處理器可應對多種應用需求開源操作系統是工業領域必然趨勢

2021-02-19 06:11:21

傳統的、基于通用DSP處理器并運行由C語言開發的算法的高性能DSP平臺,正在朝著使用FPGA預處理器和/或協處理器的方向發展。這一最新發展能夠為產品提供巨大的性能、功耗和成本優勢。

2011-09-29 16:28:38

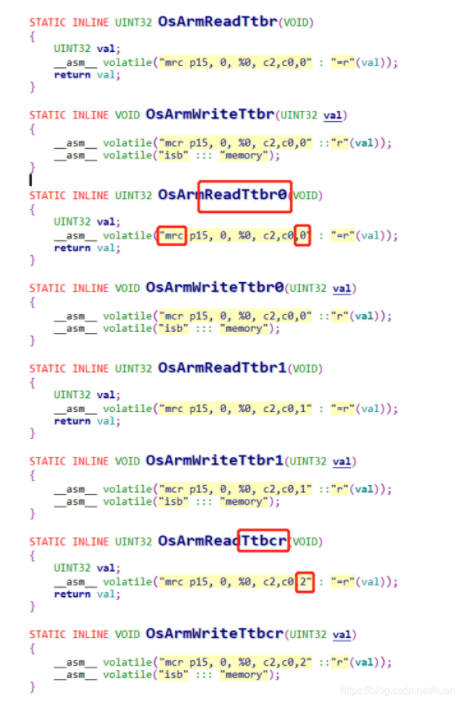

MCR指令將ARM處理器的寄存器中的值傳到協處理器的寄存器中去這里用CP15協處理器來作為例子MCR{cond} p15,

2022-01-20 06:08:02

。 PSoC模擬協處理器通過提供可擴展和可重新配置的架構來簡化基于傳感器的系統的設計,該架構集成了可編程的模擬前端(AFE)和信號處理引擎(32位Arm?Cortex?-M0+),可以對其進行校準和調整

2020-09-01 16:50:45

呵呵,s3c2410...在vivi中的s3c2410.h文件中設置時鐘時 有這么一段mrc p15,0,r1,c1,c0,0orr r1,r1,#0xc0000000;mcr p15,0,r1,c1,c0,0這段的每句 的意思是什么?為什么要用到些處理器指令?協處理器指令的作用是干什么?

2019-02-25 12:34:48

可以包含一個存儲器存取(DMA)引擎。在增加額外的邏輯情況下,DMA引擎允許協處理器工作在位于連接到總線的存儲器上的數據塊,獨立于CPU。2. I/O連接與I/O連接的加速器直接連接到一個專用的I/O

2015-02-02 14:18:19

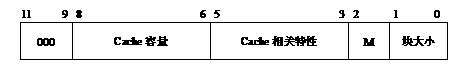

Cache分開為I-Cache(指令緩存)和D-Cache(數據緩存)。系統剛上電時,I-Cacche中的內容是無效的,并且I-Cacche的功能也是關閉的,CP15協處理器的SCTLR寄存器

2016-10-13 18:02:50

代碼加速和代碼轉換到硬件協處理器的方法如何采用FPGA協處理器實現算法加速?

2021-04-13 06:39:25

舉例說明FPGA作為協處理器在實時系統中有哪些應用?FPGA用于協處理器有什么結構特點和設計原則?

2021-04-08 06:48:20

可以實現相同的ISA,但是需要在功率效率或執行速度等方面進行權衡。最基本的處理器將包括一個寄存器文件,一個ALU,系統存儲器和一個控制單元,該控制單元使處理器可以根據其執行的指令來做出決定。ARM寄存器

2020-10-09 07:46:49

ARM處理器本身是32位設計,但也配備16位指令集。一般來講存儲器比等價32位代碼節省達35%,然而保留了32位系統的所有優勢。

2019-11-11 06:48:04

戶模式進入系統模式。ARM 處理器是一個綜合體,ARM 公司自身并不制造微處理器。它們是由 ARM 的合作 伙伴(Intel 或 LSI)制造。ARM 還允許將其處理器通過協處理器接口進行緊耦合。它還

2019-09-24 17:47:38

廠商的x86架構處理器,有IBM的power架構處理器,高通蘋果海思有ARM架構處理器。說PC端的處理器大家比較熟悉,移動端現在幾乎ARM架構處理器一統天下。那么什么是ARM處理器呢?這就要介紹一下ARM公司的產品線,ARM屬于英國一家公司,專門設計內核,目前的內核有M0,M3,M4,M7..

2021-11-24 07:05:38

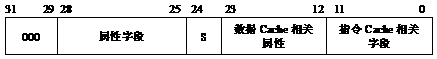

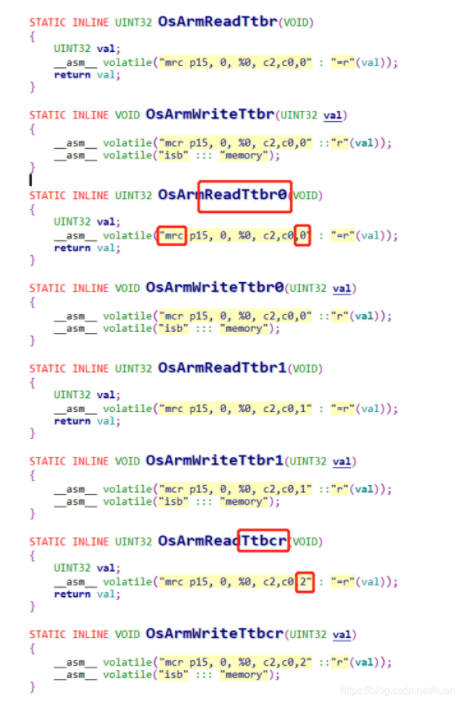

一、ARM中對于存儲管理的協處理器CP15CP15可以包含16個32bit的寄存器,分別標記為0~15。但是對于同一個寄存器的物理寄存器可能會對應多個。實際上對于CP15的訪問的指令相當簡單,只有

2022-05-17 14:19:33

1、通過一段MMU的創建來說明MMU的工作方式下面這段代碼是OAL進入kernel Start的一段代碼,它也就是wince的頁表初始化代碼,涉及到兩部分內如,分別為二級頁表的創建和一級頁表的創建

2022-05-18 16:19:41

1、基于二級頁表的地址查詢方式 上節討論了當一級描述符[1:0]為01或者11的時候表示這是一種二級頁表查詢方式,而一級頁表描述符僅僅做為二級頁表的索引。下面我們將coarse page與fine

2022-05-17 14:29:49

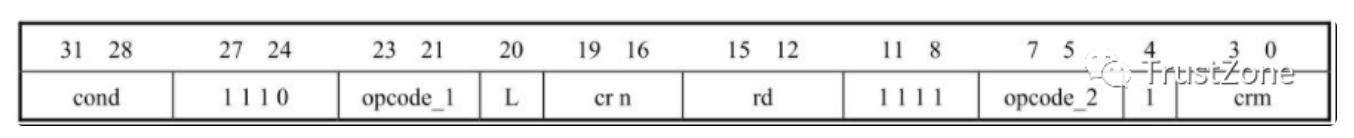

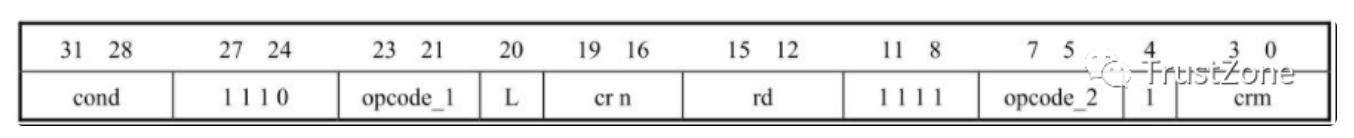

ARM訪問MMU,一般cp15就是MMU。 {cond} p#, ,Rd,cn,cm{, }MRC 從協處理器移到ARM7寄存器(L=1)MCR 從ARM7寄存器移到協處理器(L=0){cond

2018-01-28 16:39:44

今天了解了一下單片機的處理器,記錄下這些知識點。單片機由處理器、存儲器和輸入輸端口組成的微型控制器。處理器有基于復雜指令集和基于精簡指令集兩類。而單片機的處理器是基于精簡指令集的。常見的Intel

2021-11-29 06:41:51

在基于ARM的嵌入式應用系統中,存儲系統通常是通過系統控制協處理器CP15完成的。CP15包含16個32位的寄存器,其編號為0~15。訪問CP15寄存器的指令MCR ARM寄存器到協處理器寄存器

2022-05-17 14:38:17

80C186XL16位嵌入式微處理器是Intel公司在嵌入式微處理器市場的上導產品之一,已廣泛應用于電腦終端、程控交換和工控等領域。在該嵌入式微處理器片內,集成有DRAM RCU單元,即DRAM刷新

2019-07-29 07:54:57

是程序存儲區和數據存儲器都是可以放到內存中,統一編碼的,而哈弗結構是分開編址的。哈佛架構哪些處理器是哈佛架構、馮諾依曼架構?「哈佛架構」MCU(單片機)幾乎都是用哈佛結構,譬如廣泛使用的51單片機、典型

2022-08-17 15:20:52

了設計的一大挑戰。FPGA可通過在單個FPGA中實現多個視頻處理器來提供強大的處理能力。那么現在的挑戰就變成了要使數據盡快且高效地從FPGA進出。DDR3存儲器系統在大多數情況下可以為這些基于FPGA的系統

2019-05-27 05:00:02

的,CP15協處理器的SCTLR寄存器(系統控制寄存器)的bit[12]控制I-Cache的打開和關閉。I-Cache關閉時,CPU每次取指令都要讀主存,所以性能比較低。因此應該盡快打開I-Cache。同樣

2016-08-31 16:30:26

按照這句話的意思,協處理器拓展指令只能實現讀寫操作嗎,官方的案例貌似也只是讀寫指令。那如何用協處理器拓展指令實現更高級運算呢,用內聯匯編嗎

2023-08-16 07:41:54

的數據類型,所以每個寄存器傳送的字數與協處理器有關。ARM產生的存儲器地址,但協處理器控制傳送的字數。協處理器可能執行一些類型轉換作為傳送的一部分。例如,浮點協處理器將讀取的值轉換成它的80位內部表示形式

2022-04-24 09:36:47

`微機原理--數學協處理器[hide][/hide]`

2017-04-30 21:19:48

使用存儲器訪問的時序分析來揭示否則將被保密的數據。

每種機制都略有不同,有些機制依賴于微體系結構。

在《ARM內核軟件概述》一文中介紹了每種變體對ARM內核的影響,以及解決方案和應用方法。

2023-08-25 07:15:47

高速緩存作為中央處理器 (CPU) 與主存之間的小規模快速存儲器,解決了兩者數據處理速度的平衡和匹配問題,有助于提高系統整體性能。多處理器 (SMP) 支持共享和私有數據的緩存,Cache 一

2021-02-23 07:12:38

本文設計了一種在多處理器系統中的Nios II軟核處理器的啟動方案,這個方案在外部處理器向Nios II的程序存儲器和數據存儲器加載數據時,可以控制Nios II處理器的啟動。

2021-04-27 06:52:42

數據存儲器 FLASH程序存儲器 FLASH數據存儲器 片內RAM數據存儲器16M字節外部數據存儲器各有什么區別?特點?小弟看到這段 很暈。ADuC812的用戶數據存儲器包含三部分,片內640字節的FLASH數據存儲器、256字節的RAM以及片外可擴展到16M字節的數據存儲器。求助高手。解釋一下不同。

2011-11-29 09:50:46

指令操作的協處理器名.標準名為pn,n,為0~15 opcode1協處理器的特定操作碼. 對于CP15寄存器來說,opcode1永遠為0,不為0時,操作結果不可預知CRd 作為目標寄存器的協處理器

2017-01-12 21:10:30

STM32F103處理器內部存儲器結構及映射???STM32F103存儲器映像為預定義形式,嚴格規定了哪個位置使用哪條總線。???STM32F103的程序存儲器、數據存儲器、寄存器和IO端口被組織到

2021-12-09 07:51:09

狀態及程序的運行狀態,均為32位,目前只使用了其中的一部分。7種運行模式ARM微處理器支持7種運行模式,分別為:usr(用戶模式):ARM處理器正常程序執行模式。fiq(快速中斷模式):用于高速數據傳輸

2018-11-27 19:32:01

mrc p15,0,r1,c1,c0,0s3c2410芯片手冊上只是說這個指令是把p15協處理器中c1和c0寄存器里面的值傳給r1.但是協處理器的結構是什么樣的?c1和c0兩個寄存器里的值怎么存到

2015-01-23 14:05:28

ARM920到底有幾個協處理器,手冊上只看到了CP14,CP15,為什么說是若干個,是不是可以擴展,是不是每個協處理器只有一種功能?

2019-05-22 05:45:26

請問FPGA協處理器有哪些優勢?

2021-05-08 08:29:13

ARM 官網文檔是如何描述這部分內容,如下圖所示。 上面紅色框中,第一行翻譯為“系統控制協處理器”,我覺得用“系統控制協處理器”還是容易理解,可以接收。它包含了 15 個特殊的寄存器,主要提供“所有

2019-07-29 15:36:26

處理器。這些可配置協處理器可幫助設計人員解決傳統ASIC仿真中存在的許多問題,并更省力、更快捷地實現更精確的設計。

2019-07-23 06:24:16

什么是陶瓷傳感器?陶瓷傳感器的五大應用分別是什么?

2021-05-12 07:08:09

如果協處理器CP15:c1:c0中的1位和22位均為0,則ARM指令ldr的返回值是memory(addr & ~3, 4) ROR ((addr & 3) * 8)。前半句的含義是對4邊界向下取整,在本例中就是0x10960,再取其內容就是 0x40302010,后半

2011-09-28 10:14:30 1348

1348 ARM存儲系統有非常靈活的體系結構,可以適應不同的嵌入式應用系統的需要。ARM存儲器系統可以使用簡單的平板式地址映射機制(就像一些簡單的單片機一樣,地址空間的分配方式是固定的,系統中各部分都使

2017-10-17 16:34:58 1

1 2.4 I/O管理 ARM系統完成I/O功能的標準方法是使用存儲器映射I/O。這種方法使用特定的存儲器地址。當從這些地址加載或向這些地址存儲時,它們提供I/O功能。某些ARM系統也可能有直接存儲器

2017-10-18 13:57:03 2

2 ARM核具有協處理器15(CP15)、保護模塊和數據和程序存儲器。管理單元(MMU)具有表旁側緩沖器。它有單獨的16K字節指令和16KB字節。數據緩存。兩者都是與虛擬索引虛擬標簽(VIVT)的四路關聯。手臂核心也具有8KB RAM(向量表)和64KB ROM。

2018-04-24 15:12:17 0

0 本文首先介紹了ARM處理器特點與主要模式,其次介紹了arm的協處理器有幾個,最后介紹了CP14和CP15系統控制協處理器。

2018-04-24 15:34:25 8504

8504 ARM處理器使用協處理器15(CP15)的寄存器來控制cache、TCM和存儲器管理。CP15的寄存器只能被MRC和MCR(Move to Coprocessor from ARM Register )指令訪問,包含16個32位的寄存器,其編號為0~15。本篇重點講解其中的 C7C2C13三個寄存器。

2020-11-19 15:34:05 14

14 處理器使用 C15 協處理器的寄存器來控制 cache、TCM(Tightly-Coupled Memory)和存儲器管理。CP15 的各個寄存器的概要信息如下圖,圖片來自官方資料《ARM

2024-02-20 14:28:03 150

150

正在加载...

電子發燒友App

電子發燒友App

評論