長久以來,計算機系統的抗干擾一直是人們關心的重要問題,因為計算機用得越來越廣,可靠性越來越重要,而抗干擾本身就是可靠性的重要組成部分。為了汽車、飛機、衛星、反應堆的安全,人們在抗干擾問題上花費了大量精力與金錢,盡管已經取得了長足的進展,但在性價比上遠不能滿足要求,以致高抗干擾的要求只是在高技術領域才加以考慮。本文討論了干擾對錯誤的形成機制,提出了對MCU改進的建議。這個建議如果實施,不僅有利于高技術領域的應用,也會惠及一般的民用領域。

1 干擾源的討論

很久以前,還在“8031+2764+14433”的年代,我們做了一批過程監控儀表,用于滅菌過程F0的監控,遇到了強烈的干擾問題。滅菌過程約30 min,由電觸點壓力表控制進氣電磁閥,間接控制溫度。F0是一個溫度函數的積分值,可以反映滅菌的效果,它綜合考慮了溫度波動的影響。當時采取了一些抗干擾措施,例如,硬件上對信號線屏蔽,信號濾波;軟件上的智能濾波,程序復執,程序分段保護,數據后備,端口等重復初始化,ROM的定時校驗和檢驗,多種出錯報警,出錯時重新熱啟動(可使問題有所緩和,但偶然會有判為ROM校驗和錯而停機的情況出現)。由于當時F0只是用作參考,問題尚不嚴重,如要掩蓋,也可以用熱啟動代替停機;但很快F0要作為產品工藝參數,用記錄紙備案,于是就重新設計了監控儀。新的監控儀用89C51+14433,再加上光耦和TI5617 D/A轉換器,將溫度和F0變為模擬量后送到雙筆記錄儀,實現產品工藝過程的記錄與存檔。硬件上,光耦隔離后部分是D/A和模擬電路,軟件在原有基礎上添加與TI5617有關的串行通信部分。TI5617的串行通信類似I2C,由CS、DIN和SCLK三條線構成,SCLK數據位時鐘可達到25 ns,速度很高。用于計算的周期是6 s,儀表用定點算法配以查表,所以留出了充足的時間做許多抗干擾的工作。在D/A用的串行通信中甚至考慮了多次重復發送的子程序,希望減少通信錯誤的影響;但結果卻很壞,記錄紙上是一片墨帶。由于不知道通信對錯,很可能最后一次傳送就是錯的,于是不得不重新處理抗干擾問題。

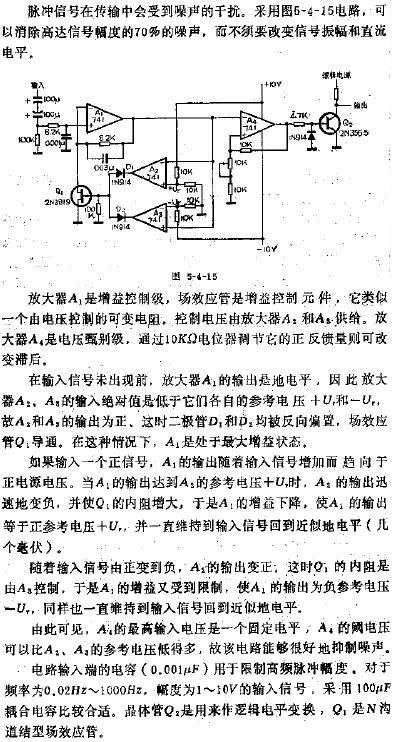

經查干擾主要發生在電磁閥動作的時候,由于不可能在現場為每一個簡單的小表制作一個良好的地線,一般的市售電源濾波器件根本不起作用。現場用的是220 V交流電磁閥,無法設計緩沖線路。分析認為,電磁閥斷開時會在電源上產生很大的反向電壓。交流電源的示波器受到干擾,在無法看清干擾的情況下,就用數字萬用表觀察,可以觀察到1 300 V以上的讀數。考慮到數字萬用表輸入的濾波效果,真正的峰值還要大,因此推想,高頻的干擾穿越了變壓器繞組間電容,造成變壓器次級交流電壓瞬間反向。盡管反向波幅的衰減很大,但因方向已改變,整流二極管來不及響應,已不供電,而濾波的電解電容器動態上來不及反應,也不供電,造成穩壓前直流電源瞬間下降。同時它通過整流二極管,78L15、78L05等低頻器件到達二組隔離的電源,造成直流電源跌落。循此思路,發現TI5617的SCLK可能出現不正確的時鐘信號,造成數據傳送的錯誤。TI5617的讀數發生在SCLK的下降沿,說明書上強調,在非傳送時減少饋通應使SCLK=LOW,為節省電流消耗,SCLK是從光耦的基極輸出的。因此若光耦次級電源跌落,確實會造成SCLK下降而誤讀。然后我們在基極電阻(20 kΩ)上并聯0.1 μF電容,在光耦次級電源上串接高頻二極管,以防0.1 μF電容器通過光耦反向放電。采取此措施后,記錄曲線不再有墨帶。對本應用而言,干擾問題初步解決,但仍不徹底。干擾得到解決本身證實了分析是正確的——來自電源的干擾有可能進到直流電源部分。

國際標準ISO 7637是針對汽車電子領域電源的傳導干擾問題的。它規定有5a/b等多種測試波形,反映實際應用中會遇到的情形。其中,關斷感性負載(例如雨刮器的馬達)引起的電壓升高,在12 V系統中可達50 V,雖有瞬間超過元器件耐壓而引起損傷的可能性,但不會直接引起誤動作。而在波形#1中,關斷感性負載(例如電動座椅的馬達和座椅的加熱系統)產生的脈沖,在電源為12 V的系統中1 μs可達到-100 V,衰減到10%的時間為2 ms。在波形#3a中,電源為12 V的系統里5 ns可達到-138 V,回到0 V的時間大約為100 ns。這些是典型數據,實際上電源線不是匹配的傳輸線,干擾波還要來回反射,情況更為復雜。在這些場合,也可能發生直流電源的跌落干擾。

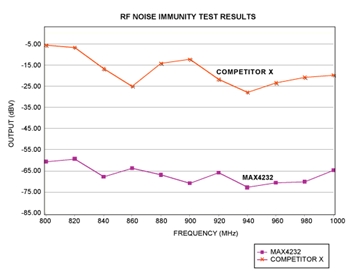

空間的幅射干擾也是經常遇到的問題,例如在太空或反應堆附近,電子器件會受到重離子的轟擊而產生故障;又如在空港區或大電流、高電壓區域,電子器件也會受到強電磁輻射而發生故障。在這些場合,干擾也會引起MCU的基本門電路工作失誤。

2 Watchdog不能解決軟件可靠性問題

Vcc的跌落會引起MCU的誤動作。MCU里每一個讀/寫操作都是由門電路實現的,門的開關依賴于門的閾值和信號的時序。電源跌落時閾值發生變化,振蕩器產生的信號時序也會變形。下面以8051單片機為例,考察如果干擾發生在執行指令“MOV dir1, dir2”時會產生什么后果。假定錯誤發生在指令的第1字節,最壞的情形是每個bit都反轉,而最大的概率是只有一個bit發生反轉。一個bit發生反轉的情況如表1所列。

表1

從表1可見,一個bit的變化完全改變了指令的意義,程序流或數據產生不可預測的變化。例如,表中的跳轉部分(bit 0, 2或5發生變化)可能不轉入死循環,不引起Watchdog動作,也有可能跳到非正常指令處,直至死循環。表中非跳轉指令則有可能改變累加器(bit 0, 1, 3, 4,6或7發生變化),數據RAM(bit 1,3, 6或7發生變化)或狀態寄存器(bit 0, 1, 3, 4,6或7發生變化)。如果錯誤發生在指令的第2或第3字節,數據的源或目的地址就錯了。因此,即使Watchdog沒動作,也不表示程序運行正常。對8051其他指令作分析可得到類似的結果。由此可見,Watchdog至多保證系統不死機,卻有可能掩蓋了數據的錯誤。

F0設計中,在關鍵點大量采用了“MOV dir1,tmp”,“MOV tmp, dir2”的形式將數據從dir1送到dir2,而不采用“MOV A,@R1”類指令,以減小對原始數據破壞的可能性,從而為程序復執創造條件。例如在備份數據Treh到Tbkh時,先將Treh送tmp1,然后將數據由tmp1送到備份Tbkh,再校驗Tbkh與Treh是否一樣。若不一樣,就重作備份。采用的部分程序如下:

MOVtmp1, Tbkh85 53 19

MOVA, tmp1E5 19

XRLA, Treh65 4C

JNZtbkp70 F1

其中“MOV A, tmp1”仍有破壞tmp1的可能性,但tmp1是Treh的拷貝,壞了可重做;“XRL A, Treh”有可能破壞Treh,但已無法作其他選擇。

在硬件抗干擾方面,有許多專用的電源監控芯片,如TL7705等,但是它們只適合在較慢的電源擾動下使用。對于直流電源的跌落干擾,MCU根本來不及作現場的保護工作,所以它不是解決快速干擾問題的辦法。

在F0中使用的辦法也不盡完善,一般單片機線路中還有很多外圍線路,例如F0中的光耦,3個光耦同時導通時要消耗約50 mA的電流,它們形成的動態電阻很小,發生電源跌落時,并聯于MCU的解耦電容對此電阻放電,無法保證MCU正常工作的額定電壓。如在MCU電源中串接高頻二極管,就會引起額外的電源消耗,在低功耗的應用中也會形成新的缺點。有些功能強大的MCU本身功耗就大,容許的電源變化范圍小,能否依靠解耦電容對抗電源跌落還需要檢驗。綜上所述,軟件解決辦法不徹底,硬件解決辦法也有很多缺點與限制。

3 MCU要增加的功能

由于干擾而使指令出錯的問題不是Watchdog能解決的,特別是造成源數據錯時,程序復執也不能糾正錯誤的結果。程序設計者要在現成的指令體系中找到對源數據危害性概率最小的指令不容易。即使找到,也不能保證指令在有多bit跳變時源數據不錯。另外,有些指令錯誤也可能破壞其他處的數據。利用破壞數據概率最小的指令設計程序也不是好辦法,它既耗ROM空間,又費運行時間。

增大指令的Hamming距離可以改善這一情況。例如,給指令增加一到數位校驗位,一旦指令通不過校驗,就不執行,并重新取指。這樣,問題就有可能在產生后果前解決。就目前MCU的設計與生產水平而言,在技術與成本上這種增加不會有很大困難。雖然這一辦法在添加的校驗位有限時仍會有一定出錯概率,但這種概率可以小到能接受的程度。

為了更為可靠,作校驗的線路可有某種冗余。連續重取指可能反映有其他故障,應通過某種方式通知應用層。為了不打擾程序設計者,這些指令的添加位應該在寫入ROM時自動生成,這樣就不會產生與現有產品的兼容性問題。

在早期的MCU應用中,Watchdog是外置的,后來都集成到MCU里面去了。如果實現上述功能,MCU的抗干擾能力會更強,Watchdog可能就不需要了。軟件的可靠性分析就可以將程序走飛和數據的完整性問題分割出來加以處理,軟件部分更專注于邏輯分析,意義深遠。

電子發燒友App

電子發燒友App

評論