主控制板的硬件系統(tǒng)結(jié)構(gòu)

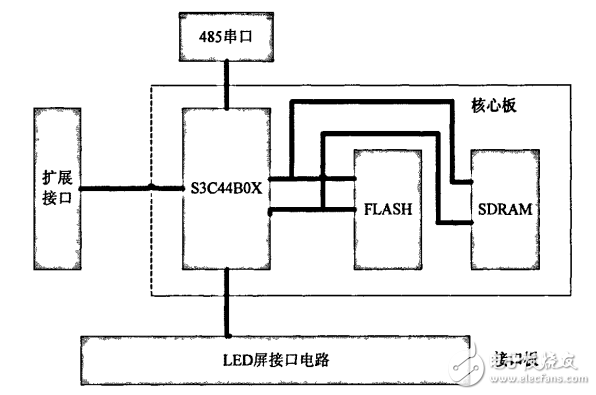

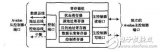

圖3-3硬件結(jié)構(gòu)框圖

大型LED顯示系統(tǒng)的主控制板應該能夠完成以下功能:

(1)接收PC端發(fā)送來要求顯示的點陣碼以及顯示模式并且存儲。

(2)根據(jù)顯示模式對原始點陣碼進行排序,以符合DMA的傳輸數(shù)據(jù)要求。

(3)將排序好的點陣碼映射到LED顯示屏相應顯示位置的列數(shù)據(jù)鎖存器并且控制行驅(qū)動循環(huán)掃描顯示。

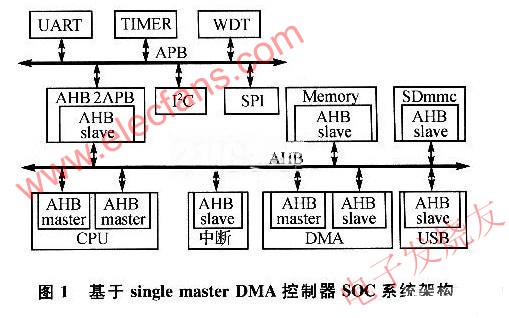

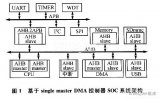

根據(jù)系統(tǒng)要求,以及未來擴展需求,系統(tǒng)結(jié)構(gòu)框圖如圖3.3所示。本系統(tǒng)設(shè)計采用核心板和接口板分開設(shè)計的方式,增強了系統(tǒng)應用的靈活性和可擴展性。其中圖中虛線框內(nèi)為核心板,虛線框外為到LED顯示屏的接口板。核心板完成任務(wù)(1)、(2)、(3)。接口板完成邏輯電平轉(zhuǎn)換、譯碼、鎖存等邏輯功能以配合核心板完成任務(wù)(3)并且驅(qū)動輸出信號。

采用并行DMA數(shù)據(jù)傳輸可選擇MCU加DMA芯片和具有內(nèi)部DMA控制器的CPU兩種方案,從系統(tǒng)結(jié)構(gòu)和成本以及開發(fā)復雜度方面考慮,后者更加合理。由于使用硬件DMA并行傳輸列數(shù)據(jù),將LED顯示屏上的一系列同行列數(shù)據(jù)鎖存器視為一段連續(xù)的存儲單元,由于并行數(shù)據(jù)傳輸LED顯示模塊電路結(jié)構(gòu)并不能完全滿足16bit并行DMA數(shù)據(jù)傳輸?shù)囊螅譃榱四苁股洗腖ED顯示驅(qū)動模板產(chǎn)品仍能使用,列顯示數(shù)據(jù)需要根據(jù)顯示模塊電路結(jié)構(gòu)及并行DMA數(shù)據(jù)傳輸方式重新排序,并以重序排列格式存放在指定的顯存地址中.當在靜態(tài)顯示模式時,重新排序的數(shù)據(jù)量并不大,但當動態(tài)模式顯示時(如上滾顯示時),重新排序的列數(shù)據(jù)以頁面的方式存儲在顯存內(nèi),這樣將占用大量的存儲空間,甚至達到幾十M字節(jié).若使用SRAM作顯存成本太高,體積太大,使用廉價大容量的SDRAM可以很好的解決該問題,但由于SDRAM的電路特點【2I】,必須在系統(tǒng)中有SDRAM數(shù)據(jù)刷新控制器。為減小系統(tǒng)成本和系統(tǒng)復雜度,期望找到自帶外部存儲控制器的微處器。出于上述考慮于是本系統(tǒng)設(shè)計選擇使用三星公司ARM7TDM【田】內(nèi)核具有內(nèi)部DMA控制器和SDRAM存儲控制器的S3C44BOX作系統(tǒng)的主控制器;廉價大容量的SDRAM選擇使用4Mxl6Bit×4Bank的K4S561632D,它對于512x256(8平方米)的單色屏來說完全滿足要求了。

由于S3c44BOx自身不具有非易失性存儲器,所以必須外接非易失性存儲

器來存放代碼及需要保存的點陣碼和顯示的控制信息。考慮到點陣碼和顯示控制信息會經(jīng)常更新,所以非易失性存儲器需要能夠電重復擦寫,由于原始點陣碼的數(shù)據(jù)量可能很大(幾百kByte),并考慮到系統(tǒng)的升級選擇使用IMxl6Bit的SST39VFl601作系統(tǒng)的代碼數(shù)據(jù)存儲器,在本系統(tǒng)應用中SST39VFl601的IM×16Bit存儲空間分為代碼部分與原始點陣碼部分。

3.2.2存儲空間配置

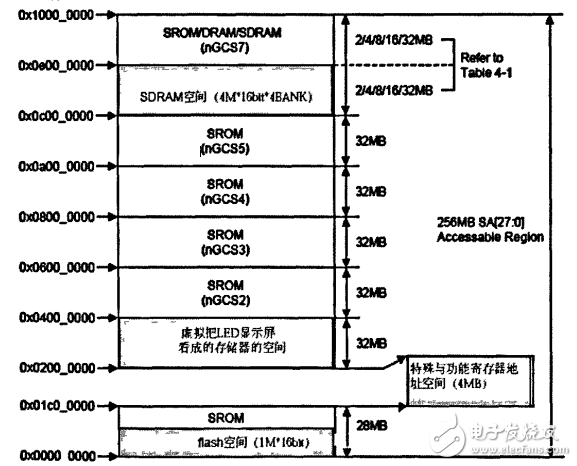

圖3--4系統(tǒng)存儲空間分配圖

ARM微處理器的理論尋址空間是4GB,采用統(tǒng)一編址的方式,將系統(tǒng)的各類存貯器(如FLASH、SRAM、SDRA~D、外設(shè)、特殊功能寄存器都映射到該地址空間[231.為了便于管理,又將地址空間劃分為若干小塊,每一個小塊稱為一個存貯器組(MEMORYBANK),通常由硬件電路提供每一個存儲器組的選擇信

號.S3C44BOX提供一共256MB的地址空間,分為8個組,每組地址空間為32MB,S3CA4BOX的[nG-CSo~nGCS7l弓l腳就g分別選通這八組地址空間的選通信號引腳田】。本系統(tǒng)設(shè)計存儲空間分配圖如圖3.4所示.

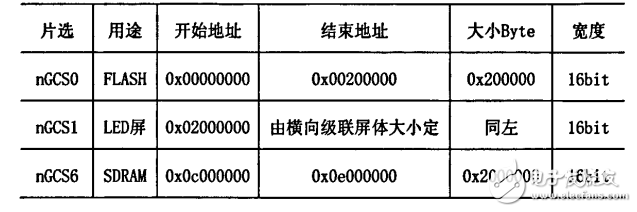

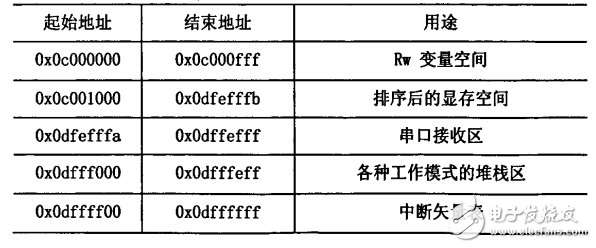

主控板的存儲空間映射如表3.1所示:

表3-l存儲空間分配表

LED顯示屏所占的存儲空間由LED的橫向級聯(lián)屏數(shù)決定,如對于512“256的屏體,橫向級聯(lián)數(shù)是8,存儲空間為:16*8*16bit共256Byte,可以看出為LED屏留出的地址空間是綽綽有余了.

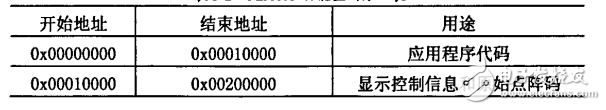

主控板的FLASH地址范圍從0x00000000到0x00200000,共2Mbytes。其空間范圍被分為兩個區(qū)域用途見表3-2.

表3-2FLASH功能空間分配表

主控板的SDRAM地址范圍從0xoc000000到0xodffi珊空間分配與用途如表3.3所示。

表3-3SDRAM功能空間分配表

3.3硬件電路的詳細設(shè)計

3.3.1S3C44BOX簡介

32位RISC處理器S3C44BOX采用ARM7TDMI內(nèi)核,提供全面的、通用的片上外設(shè),大大減小了系統(tǒng)電路中除處理器以外的元器件配置,從而最小化系統(tǒng)成本,本系統(tǒng)關(guān)注的特性如下:

(1)2.5VRISC體系結(jié)構(gòu)和ARM7TDMI內(nèi)核處理器強大指令系統(tǒng),支持Thumb代碼,提高代碼密度;支持JTAG片上集成ICE解決方案。

(2)支持大/小端方式;支持8個存儲器BANK。其中7個具有固定的BANK起始地址和可編程大小,1個具有可編程BANK起始地址和BANK大小;

其中6個支持ROM/SRAM訪問BANK,2個RohⅣS融呦RAM訪問

BANK;所有的存儲器BANK具有可編程的訪問操作周期。

(3)內(nèi)部集成可編程選擇使用的8KB高速緩存cache,未用的cache可用作0/4/8kByte的SRAM空間。采用保持主存儲器與cache內(nèi)容一致性的“寫穿式”策略。

(4)片內(nèi)的鎖相環(huán)使MCU工作時鐘最大達75MHz

(5)30個中斷源,采用向量化的IRQ中斷模式以減少中斷的延遲,并支持

FIQ為緊急的中斷請求進行服務(wù)。

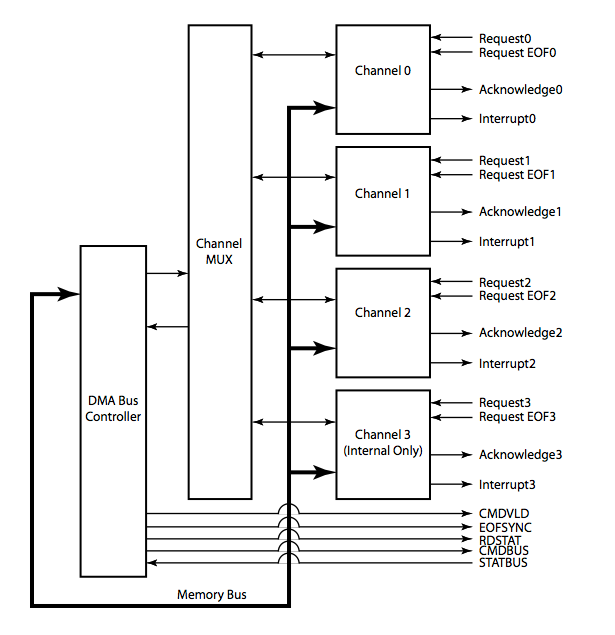

(6)2通道通用DMA控制器,2通道接口DMA控制器,不需要CPU干預,支持存儲器到存儲器,存儲器到10,Io到存儲器,Io到IO的DMA數(shù)據(jù)傳輸。并支持ontheny模式。

S3C44BOX還有很多其他的應用資源,在此不贅述。在本系統(tǒng)設(shè)計中僅使用了l通道通用DMA控制器,1通道的串口UART。內(nèi)部的看門狗定時器及內(nèi)部的8KSRAM,以及PC,PG口,在總線選擇上使用16bit總線,并使系統(tǒng)工作在小端工作模式。

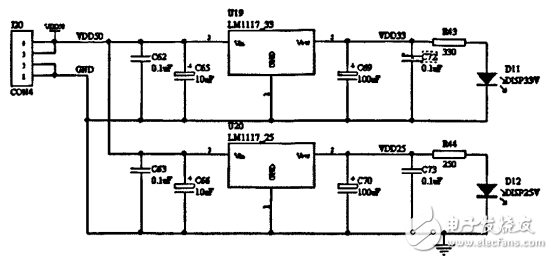

3.3.2電源電路

電源電路設(shè)計主要的考慮因素有:電源的種類、上電次序、數(shù)字,模擬混合電源處理方法、空間、輸入電壓、輸出電壓、輸出電流等,在本系統(tǒng)主控板中需要使用5V、3.3V、2.5V穩(wěn)壓數(shù)字直流電源。其中CPU分別需要3.3V和2.5V分別給片上Io口和CPU內(nèi)核供電,而LED顯示屏接口電路部分需要5V電源

供電。需要注意的是:CPU內(nèi)核和Io口應按照內(nèi)核先于IO口上電,后于Io口掉電的規(guī)則,但盡可能同時供電,二者的時差不能太長,否則可能毀壞芯片剛。為簡化電源電路設(shè)計,使用5V直流開關(guān)電源輸入,通過3.3V和2.5V的線性穩(wěn)壓電源芯片[251得到3.3v和2.5V的直流穩(wěn)壓電源。電路如圖3.5所示.

圖3-5電源電路原理圖

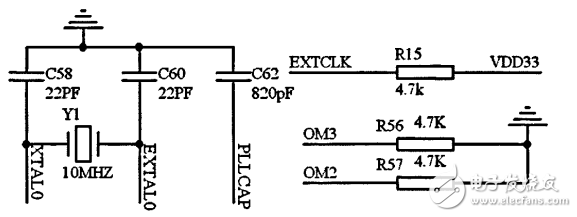

3.3.3晶振復位電路

由于本系統(tǒng)中串口使用9600波特率,使用的系統(tǒng)時鐘最好是9600的整數(shù)倍,故選用3.6864MHz的晶振并配置S3C44BOX內(nèi)部的PLL六倍頻后得到22.1184MHz的系統(tǒng)時鐘,S3C44BOX內(nèi)部的PLL電路兼有倍頻和信號放大功能.為節(jié)省控制板成本,使用無源晶振,需要注意的是:

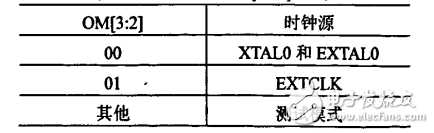

(1)上電后時鐘源的選用取決OM[3:21弓1腳的邏輯電平狀態(tài),如表3-4所示。

(2)3C44BOX的PLLCAP引腳需要接一個680pF的補償電容。

(3)S3C44BOX的EXTCLK引腳需要通過4.7ko的限流電阻接3.3v的高電平,表明不使用EXTCLK引腳提供時鐘[20-1,電路如圖3-6所示.

圖3-6晶振電路原理圖

表3-4時鐘源選擇OM[3:2]配置表

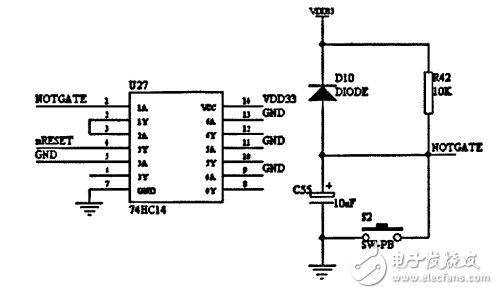

圖3.7所示的是一個簡單實用的上電復位電路。在系統(tǒng)中,復位電路主要完成系統(tǒng)的上電復位和系統(tǒng)在運行時用戶強制按鍵復位功能。復位電路由簡單的Rc電路構(gòu)成,經(jīng)使用證明,其復位邏輯是可靠的。

圖3-7復位電路原理圖

該復位電路的工作原理如下:在系統(tǒng)上電時,通過電阻R42向電容C55充電,當C55兩端的電壓未達到高電平的門限電壓時,NOTGATE端輸出為低電平,系統(tǒng)處于復位狀態(tài);當C55兩端的電壓達到高電平的門限電壓時,NOTGATE端輸出為高電平,系統(tǒng)進入正常工作狀態(tài)。當用戶按下按鈕S2時,C55兩端的電荷通過D10和R42被泄放掉,NOTGATE端輸出為低電平,系統(tǒng)進入復位狀態(tài),再重復以上的充電過程,系統(tǒng)進入正常工作狀態(tài)。NOTGATE通過兩級非門電路用于按鈕去抖動和波形整形;通過調(diào)整R42和C55的參數(shù),可調(diào)整復位狀態(tài)的時間,值得注意的是要使上電后S3C44BOX的nRESET要持續(xù)4個時鐘的低電平,即當系統(tǒng)時鐘為22.1184MHz時為200ns。但是,在上電后,系統(tǒng)的晶振往往需要100ms~200ms的時間穩(wěn)定腳l所以上電后C55正極應保持足夠長的低電平的時間。復位時間主要由R和C確定,C55正極電壓礦=3.30一e-t/7),f=RC。設(shè)0.8V為低電平的上限,選R42為100kQ,C55為10uF,可得t*277ms,從而滿足復位要求。

3.3.4FLASH接口電路

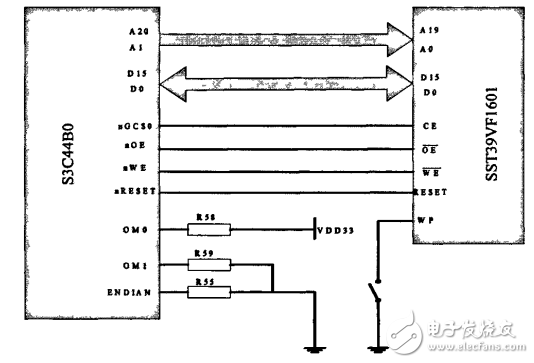

系統(tǒng)的代碼與從上位機接受到的原始點陣碼以及顯示控制信息數(shù)據(jù)存放在CPU外的FLASH芯片中,當S3C44BOX上電復位后,它立即從0x00000000地址處取指并開始執(zhí)行,并把定位在地址0x00000000處的存儲器稱為BOOTROM。因此系統(tǒng)的啟動代碼應放置在0x00000000處,ARM系統(tǒng)中通常使用能夠快速讀取、因此方便寫入的FLASH作為代碼和常量存儲器。剛上電時CPU對FLASH的接口不需要任何軟件上的配置,因為S3CA4BOX內(nèi)部的存儲器訪問控制寄存器默認的控制時序足夠慢,可以讀出任何速度的ROM芯片數(shù)據(jù),但為了充分發(fā)揮FLASH芯片的性能,應在初始化中配置相應存儲器的訪問時序四l。值得注意的是要使CPU能正常地對FLASH進行操作,需要注意兩個硬件設(shè)置:3cY4,端和BANK0的總線寬度岡.ARM體系結(jié)構(gòu)可以用兩種方式來存儲字(這里的字是32bit即4Byte),稱為大端格式和小端格式.S3C44BOX的ENDIAN引腳的輸入電平的邏輯來確定數(shù)據(jù)類型是大端還是小端【3ll。0為小端,l為大端。在本系統(tǒng)中使用小端方式,所以ENDLAN應該接一下拉電阻后接地,連接示意圖如圖3.7所示.

圖3-8S3C44BOX與FLASH連接示意圖

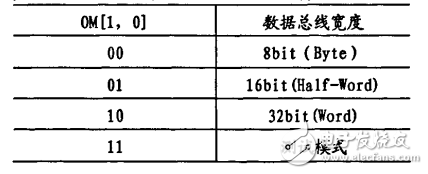

BOOTROM在地址上位于ARM處理器的BANK0區(qū),它可能具有具有多種數(shù)據(jù)總線寬度,這個寬度是可以通過硬件設(shè)定的,即通過S3C44BOX上OM[1,O】引腳上的邏輯電平設(shè)定,如表3-5所示.

表3.5BOOTROM在BANK0的數(shù)據(jù)總線寬度設(shè)定

本系統(tǒng)采用一片SST39VFl601(1Mxl6bit)作為代碼和數(shù)據(jù)存儲器就能夠滿足系統(tǒng)要求了,所以本系統(tǒng)使用16bit外部總線。因此OM[1,o]-腳應該設(shè)為Ol,并且初始化程序中將BWSCON寄存器中的DWO設(shè)為01。本系統(tǒng)采用TSOP封裝的SST39VFl601。應注意的是SST39VFl601的WP引腳,當WP接穩(wěn)定的低電平時扇區(qū)O是不能被擦除的1321,只有WP腳接穩(wěn)定的高電平或浮空時(當該腳浮空時內(nèi)部電路將其拉高)才能擦除,所以應在該腳處設(shè)置一根跳線,下載程序時將其浮空,而在產(chǎn)品運行時使其接低電平。由于S3C44BOX是按照字節(jié)編址的,又由于SST39VFl601是16bit為一個存儲單元,因此處理器的地址向左偏離一位田l,采用ADDRI與SST39VFl601的A0相連,即:S3C44BOX的ADDR[20:l】對應著FLASH的A[19:o】。由于FLASH的映射在BANK0區(qū)域內(nèi),SSl”39VFl601的片選與S3C44BOX的NGCS0。

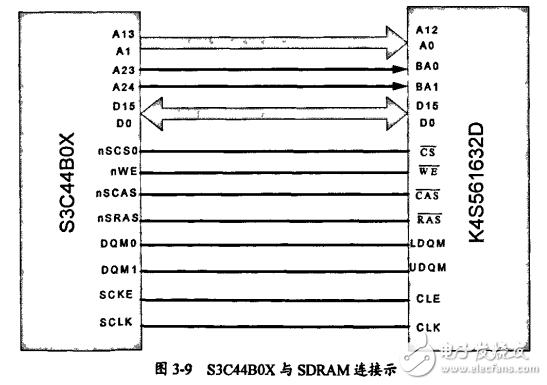

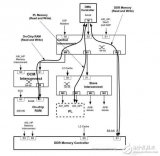

3.3.5SDRAM接口電路

SDRAM是易失性存儲器,在調(diào)電后數(shù)據(jù)立即消失,但是其具有存儲速度快,容量大成本低的特點,廣泛應用于各種嵌入式系統(tǒng),本系統(tǒng)采用4Mxl6bhx4b£mk,即32MByte的SDR■uM芯片K4S561632D作為系統(tǒng)的R/W段、顯存、上位機通信段,中斷向量表,堆棧數(shù)據(jù)的存儲器,存儲空間的詳細配置見第3.2.2節(jié)。由于SDRAM的存儲單元電路的特點,存儲單元可以理解為一個電容,總是傾向于放電,為了避免數(shù)據(jù)丟失,必須定時充電刷新。S3C4480X芯片本身提供了與DRAM和SDRAM進行直接接口的方案,因為不需要編程外圍的邏輯電路來實現(xiàn)SDRAM的刷新時序,只需對S3C44BOX內(nèi)容相應若干個存儲器接口控制寄存器進行適當?shù)呐渲眉纯伞3C44BOX與K4S561632D的連接示意圖如圖3-9所示。

K4S561632D是一款容量為32MB的SDRAM(同步動態(tài)隨機存儲器),所有的輸入與輸出信號與CPU的前端總線的系統(tǒng)時鐘相同,所以S3C4480X為其提供同步時鐘腳SCLK,該腳與K4S561632D的CLK腳相連。

K4S561632D的存儲空間組織方式是:4M×16bit×4bank,是多bank結(jié)構(gòu)口‘1.前面提到過DRAM的存儲單元電路特點相一個電容,在讀取數(shù)據(jù)前需要進行預充電,采用多bank結(jié)構(gòu)可以在一個bank進行預先充電時間對另外一個bank進行讀寫操作,這樣當進行一行讀取后,對已預充電的bank又可以馬上讀取了,這樣就省去了預先充電的時間,大大提高了存儲器的訪問速度。K4s561632D分為4個bank,它內(nèi)部對4個bank進行管理。控制各個bank進行預先充電,它上面的BA0,BAI引腳就是用來實現(xiàn)4個bank間的選擇。由于K4S561632D的容量為32MB,其BAl與BA2接地址線A24、A23。由于高速數(shù)字布線的需要,在PCB布線時,幾根重要的信號線端應接20歐阻抗匹配電阻,以保證高速數(shù)字信號的畸變不超過要求的范圍。

再讀取操作時候首先使CKE引腳有效,激活K4S561632D,隨后是一個讀或者寫有效,在激活后的地址用來選擇需要的操作的bank和行(BA0、BAI用來選擇bank,A0道All用來選擇行)。在行地址被讀取并延遲一到幾個時鐘后(潛伏期)地址總線上A0到A8用來選擇操作開始的列地址,這樣,數(shù)據(jù)就被讀取出來了。

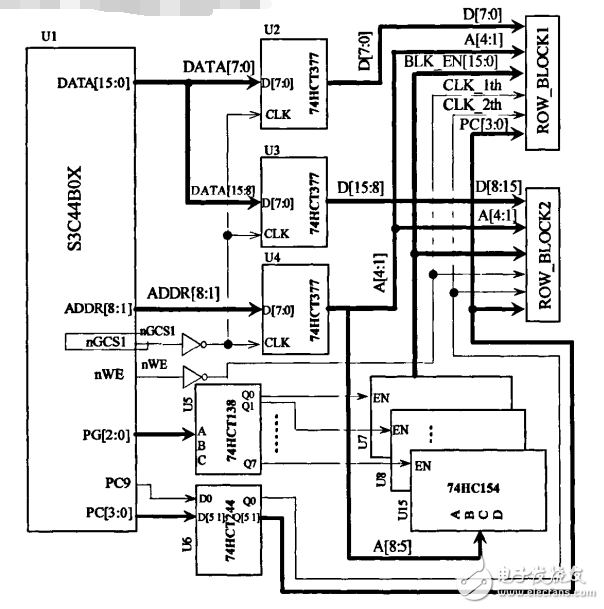

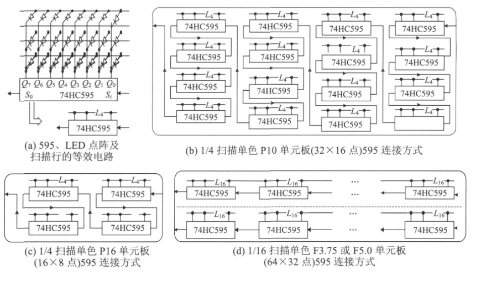

3.3.6主控電路與LED屏的接口電路設(shè)計

本顯示系統(tǒng)選用基于ARM7TDMI內(nèi)核并帶有內(nèi)部DMA控制器的S3C44BOX作主控制器,使其工作在ARM狀態(tài),為了加快傳輸數(shù)據(jù)的速度,提高傳輸數(shù)據(jù)的效率,本系統(tǒng)的設(shè)計思想是:

(1)將LED顯示屏虛擬的視為一段連續(xù)的存儲空問【3習.C2)使用S3C44BOX內(nèi)部的DMA控制器實現(xiàn)數(shù)據(jù)的準確傳輸,在傳輸過程中CPU不參與,實現(xiàn)在連續(xù)的讀寫操作時就完成一段數(shù)據(jù)的傳輸。

(3)使用并行技術(shù),主控板到LED屏的數(shù)據(jù)總線寬為16bit,同時對縱向級聯(lián)的兩個顯示模式傳輸數(shù)據(jù)。

在第2.2.4節(jié)中已說明了將LED顯示屏視為一段連續(xù)的存儲空間是可能的,它是使用DMA控制器在連續(xù)的讀寫操作完成一段數(shù)據(jù)傳輸?shù)幕A(chǔ)。由第2.2.4節(jié)可知,并行數(shù)據(jù)傳輸顯示模板上的譯碼電路與錯位級聯(lián)思想可使每個顯示模板及顯示模板上的各個列數(shù)據(jù)鎖存器準確選通,如圖2-6所示,橫向級聯(lián)的顯示模板可看成一段連續(xù)的存儲單元,所以對顯示驅(qū)動板傳輸列數(shù)據(jù)實際上就是對存儲單元的寫操作.這樣就可以利用CPU寫存儲器的控制線、數(shù)據(jù)總線、地址總線上出現(xiàn)的信號作傳輸列數(shù)據(jù)到顯示驅(qū)動板第一級列數(shù)據(jù)鎖存器鎖存的控制信號。第一級列數(shù)據(jù)鎖存器的選通譯碼器的譯碼信號可以利用微控制器的地址線,由于LED顯示屏一個顯示驅(qū)動模塊上共有16對鎖存器,所以需要4根低位地址線作第一級列數(shù)據(jù)鎖存的譯碼信號,而橫向級聯(lián)可最多級聯(lián)8塊顯示驅(qū)動模塊,所以需要三根地址高位地址線,但為了以后擴展需要預留一根高位地址線共8根地址線。列數(shù)據(jù)由數(shù)據(jù)總線傳送。

由第2.2.4節(jié)可知,并行數(shù)據(jù)傳輸?shù)腖ED顯示模板上的數(shù)據(jù)總線寬度是8bit的,而主控板到LED顯示屏的數(shù)據(jù)總線寬度是16bit,所以主控板對LED顯示屏的一次寫操作實際上是同時對縱向級聯(lián)的兩個顯示模板的同名行同名列傳輸了數(shù)據(jù),這樣提高了數(shù)據(jù)傳輸?shù)乃俣群托省5沁@樣使用16bit寬度的并行DMA傳輸技術(shù)需要軟件先將原始的點陣碼按要求進行排序,排序算法僅需在接收到新的顯示內(nèi)容后或重新上電后運行一次,這樣對于異步顯示系統(tǒng)是可以接受的。算法將在第3.4.4節(jié)詳細討論,在此我們假設(shè)顯存中的數(shù)據(jù)都是按要求完成排序的,可以直接進行DMA傳輸。

圖3-10主控板與LED屏接口電路原理圖

所以主控電路與LED顯示屏接口電路應能實現(xiàn)一下功能:

(1)選通任意位置的顯示模塊及該模塊上的第一級列數(shù)據(jù)鎖存器。將該位置要顯示的點陣碼準確鎖存,并能控制在第一級列數(shù)據(jù)鎖存器數(shù)據(jù)刷新后將刷新數(shù)據(jù)鎖存到第二級列數(shù)據(jù)鎖存器并輸出。

(2)能控制選通驅(qū)動16行同名行中一行進行逐行掃描顯示.

(3)實現(xiàn)主控芯片3.3v到LED屏5V的邏輯電平轉(zhuǎn)換136】。主控板與LED屏接口電路原理圖示意圖如圖3·10所示。對于一個大型LED屏其結(jié)構(gòu)可分為縱向級聯(lián)和橫向級聯(lián),這種結(jié)構(gòu)類似于一個三維數(shù)組.們假設(shè)一個三維數(shù)組LED[i][j]啕,其中;

i=0,l‘2…,m表示LED屏縱向級聯(lián)級的序號。

j=O,1’2…,n表示LED屏橫向級聯(lián)級的序號。

k=0,l,2…,15表示顯示模塊上16個第一級列數(shù)據(jù)鎖存器的序號.

由于系統(tǒng)使用16bit并行總線數(shù)據(jù)傳輸方式,并將LED屏視為一段連續(xù)的存儲單元,故使用A【4:l】顯示模塊上選通第一級列數(shù)據(jù)鎖存器譯碼器(圖2.5U2)的譯碼輸入,即為三位數(shù)組的k變量;使用A【8:5】作選通橫向級聯(lián)顯示模塊的譯碼器(圖3-9U7-U15)譯碼輸入,即為三位數(shù)組的j變量;由于LED屏要求具有良好的靈活性,又由于采用DMA傳輸數(shù)據(jù)要求點陣碼存放順序的技術(shù)要求,縱向級聯(lián)級選通不滿足使用地址總線譯碼選通的條件,所以使用S3C44BOX的PG[2:0]作縱向級聯(lián)級選通譯碼器的譯碼輸入,即三位數(shù)組的i變量。

由于地址和數(shù)據(jù)總線上的狀態(tài)不斷變化,所以在對LED屏進行寫操作時地

址和數(shù)據(jù)信號應進行鎖存,主控板上分別使用圖3-9中U2、U3和U4鎖存對LED寫操作時的地址、數(shù)據(jù)總線上的狀態(tài).LED屏分配首址0x2000000,當對其進行寫操作時,S3C44BOX的nGCSl和nWE腳會出現(xiàn)可編程控制時延的有效低電平。使nGCSl經(jīng)一個非門作U2、U3和U4的鎖存使能控制信號,保證僅在對LED屏訪問時地址、數(shù)據(jù)總線上的信號才被鎖存;使nWE經(jīng)一個非門作屏端第一級列數(shù)據(jù)鎖存器(圖2.5U3-U19)的鎖存使能控制信號,保證只有當刷新數(shù)據(jù)穩(wěn)定出現(xiàn)在列數(shù)據(jù)鎖存其輸入端時才被鎖存;使S3C44BOX的PCI0作所有屏端第二級鎖存器(圖2-5U20.U35)的鎖存使能控制信號線;使用S3C44BOX

的PCI3:0]作16行驅(qū)動譯碼器(圖2.5U1)的譯碼輸入。由于數(shù)據(jù)傳輸時只需要主控板對LED屏輸出控制,不需要信號反饋,所以接口電路采用廉價的5V供電的HCT電路芯片鯽口8l[391]方案,就可滿足主控芯片3.3v到LED屏5v的邏輯電平轉(zhuǎn)換。

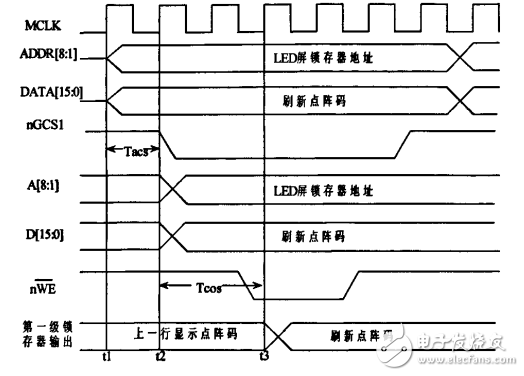

在DMA傳輸數(shù)據(jù)時,我們更關(guān)心的是DMA的寫操作,時序如圖3.1l所示.tl時刻DMA寫操作開始,地址和數(shù)據(jù)總線上出現(xiàn)了咖屏相應位置的地址和刷新數(shù)據(jù);t2時刻nGCSl引腳出現(xiàn)有效低電平,地址和數(shù)據(jù)總線上的數(shù)據(jù)被鎖存到圖3-10中U2-U4并輸出;t3時刻nwE引腳出現(xiàn)有效低電平,圖3.10中U2-U4的輸出數(shù)據(jù)被鎖存到屏端第一級列數(shù)據(jù)鎖存器并輸出。這樣主控制器就完成了一次列數(shù)據(jù)的刷新。

圖3.11DMA的寫操作時序圖

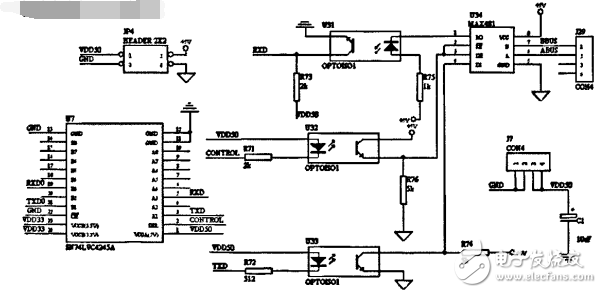

3.3.7串口電路設(shè)計

為消弱電氣噪聲對信號傳輸?shù)挠绊懀骺匕遄由衔粰C通信采用完全電器隔離的半雙工RS485電路㈣。電源使用變壓器隔離,信號線和控制線使用光耦離,電路如圖3-12所示。

圖3-12485串口電路原理圖

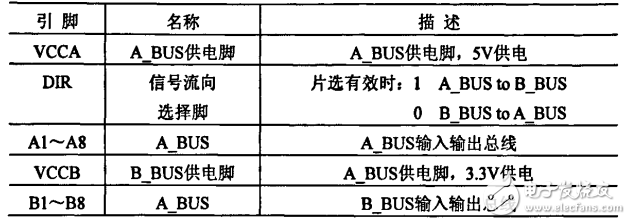

RS485裝換芯片采用半雙工485轉(zhuǎn)換芯片MAX481t411。由于使用485轉(zhuǎn)換電路使用5v供電,而主控芯片S3C44BOX使用3.3V供電,因此存在邏輯電平轉(zhuǎn)換問題.本系統(tǒng)在串口電路中使用能夠?qū)崿F(xiàn)3.3V到5v和5v到3.3V邏輯電平轉(zhuǎn)換芯片SN74LVC4245A,它的引腳說明如表3-6所示。

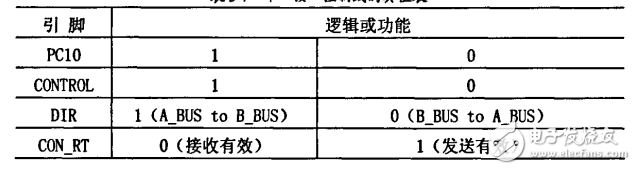

表3-6SN74LVCA245A的引腳描述

本設(shè)計使用S3C44BOX的10口PCIO作串口收發(fā)控制的控制線,但存在邏輯電平轉(zhuǎn)換的問題,PCI0首先通過74HCT244輸出得到5V邏輯電平信號線CONTROL,由它做串口收發(fā)控制的控制線和SN74LVC4245A的數(shù)據(jù)流向控制線。CONTROL控制線經(jīng)光耦隔離成為CONRT控制線控制信號真值表如表3.7所示.

表3-7串口接口控制線的真值表

由真值表可知,S3C44BOX端3.3V邏輯電平的串口引腳RXD0應TXD0應連接在SN74LVCA245A的B總線上;485串口電路5V邏輯電平的引腳RXD和TXD應連接在SN74IⅣC4245A的A總線上。

電子發(fā)燒友App

電子發(fā)燒友App

評論