本文介紹了一種以FPGA作為控制器,F(xiàn)LASH MEMORY作為主存儲(chǔ)器的大容量高速存儲(chǔ)系統(tǒng)方案,并對(duì)關(guān)鍵技術(shù)及實(shí)現(xiàn)途徑進(jìn)行了論述,在存儲(chǔ)容量及存儲(chǔ)速度上實(shí)現(xiàn)了突破。

2020-07-30 17:53:54 1917

1917

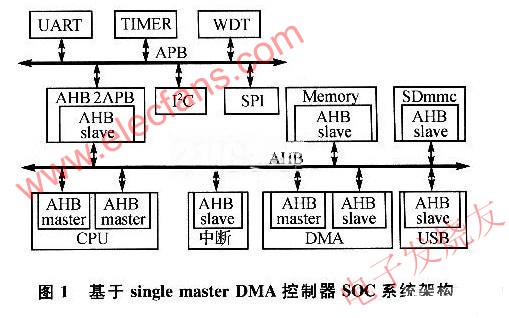

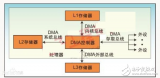

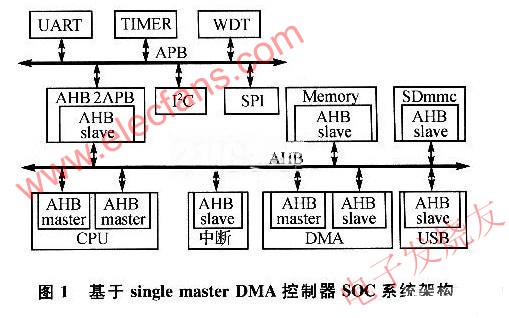

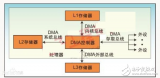

斷給中斷控制器; 5. 擁有8個(gè)DMA觸發(fā)事件并且可以編碼控制; 6. 128個(gè)(64bit)的MFIFO,在傳輸?shù)臅r(shí)候讀寫(xiě)端可寫(xiě)入到此FIFO; 7. 支持任意內(nèi)存到內(nèi)存的傳輸; 整個(gè)系統(tǒng)中的DMA

2020-12-05 10:17:17 3606

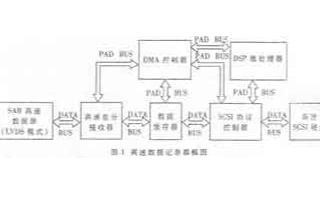

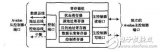

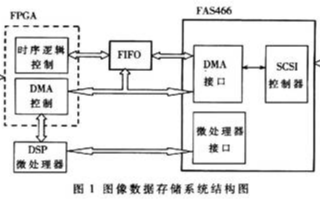

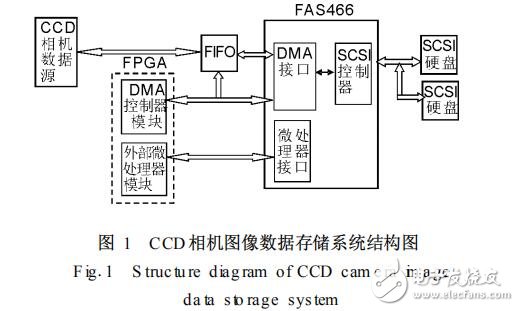

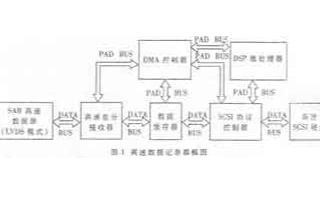

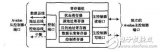

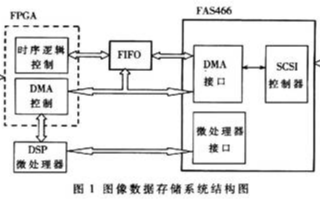

3606 整個(gè)系統(tǒng)的設(shè)計(jì)總體框圖如圖1所示,包括高速數(shù)據(jù)源、高速差分接收器、DMA控制器、數(shù)據(jù)緩存器、DSP微處理器、SCSI協(xié)議控制器和高速SCSI硬盤(pán)等子系統(tǒng);下面分別給出各子系統(tǒng)的設(shè)計(jì)(PAD BUS表示控制信號(hào)線,DATA BUS表示數(shù)據(jù)信號(hào)線)。

2020-11-12 10:23:08 2850

2850

的微控制器總線架構(gòu)和存儲(chǔ)系統(tǒng),是為了提供一個(gè)高的數(shù)據(jù)帶寬,并開(kāi)發(fā)響應(yīng)時(shí)間非常快的軟件。這篇文檔也描述了怎樣充分利用這些特性,以及對(duì)于不同的外設(shè)和子系統(tǒng)怎樣保證正確的響應(yīng)時(shí)間。

2022-12-23 11:42:28 844

844 1 DMA系統(tǒng)簡(jiǎn)介DMA(direct memory access)是一種外設(shè)與存儲(chǔ)器或者存儲(chǔ)器與存儲(chǔ)器之間直接傳輸數(shù)據(jù)的方式,在進(jìn)行DMA存取時(shí),CPU讓出總線控制權(quán),不在采用輸入輸出指令的方法

2021-07-26 08:11:30

本帖最后由 yyeee312 于 2015-11-12 15:17 編輯

DMA控制器是一種在系統(tǒng)內(nèi)部轉(zhuǎn)移數(shù)據(jù)的獨(dú)特外設(shè),可以將其視為一種能夠通過(guò)一組專(zhuān)用總線將內(nèi)部和外部存儲(chǔ)器與每個(gè)具有DMA

2015-11-04 22:50:56

DMA控制器在DSP數(shù)據(jù)采集系統(tǒng)中的應(yīng)用 DMA 控制器可以無(wú)需CPU 介入而在內(nèi)部存儲(chǔ)器、外部存儲(chǔ)器和芯片外設(shè)之間傳送數(shù)據(jù),其在DSP 系統(tǒng)中有廣泛的應(yīng)用價(jià)值。基于以DSP 芯片

2009-04-28 10:47:02

。數(shù)據(jù)傳輸支持從外設(shè)到存儲(chǔ)器或者存儲(chǔ)器到存儲(chǔ)器,這里的存儲(chǔ)器可以是SRAM 或者是FLASH。DMA 控制器包含了DMA1 和DMA2,其中DMA1 有7 個(gè)通道,DMA2 有5 個(gè)通道,這里的通道可以理解為傳輸數(shù)據(jù)的一種管道。注意:DMA2 只存在于大容量的單片機(jī)中。功能描述DMA控制器和Cort

2022-01-26 06:35:22

大家好,當(dāng)使用NWL DMA后端核心的直接控制接口時(shí),有沒(méi)有像我這樣的問(wèn)題?這是NWL提供的DMA后端核心塊適配PCIE。 DMA通過(guò)兩種方式運(yùn)行:方法1:在DMA引擎從存儲(chǔ)在系統(tǒng)存儲(chǔ)器中的描述符

2020-05-18 09:19:24

INT1,當(dāng)其有效時(shí),表明有錯(cuò)誤產(chǎn)生(如校驗(yàn)出錯(cuò))、一個(gè)事件需要服務(wù)(如FAS368M作為目標(biāo)設(shè)備被選中)或已結(jié)束某服務(wù)(如DMA結(jié)束)。·DREQ,FAS368M使DREQ有效向DMA控制器

2011-06-02 09:34:08

文章目錄存儲(chǔ)系統(tǒng)的層次結(jié)構(gòu)技術(shù)指標(biāo)層次結(jié)構(gòu)局部性原理主存儲(chǔ)器讀寫(xiě)存儲(chǔ)器只讀存儲(chǔ)器存儲(chǔ)器地址譯碼主存空間分配高速緩沖存儲(chǔ)器工作原理地址映射替換算法寫(xiě)入策略80486的L1 CachePentium

2021-07-29 09:47:21

存儲(chǔ)系統(tǒng)的層次結(jié)構(gòu)是怎樣的?怎么解決容量/速度和價(jià)格矛盾的問(wèn)題?

2021-11-02 09:22:03

Manager Unit)。arm存儲(chǔ)系統(tǒng)的體系結(jié)構(gòu)適應(yīng)不同的嵌入式系統(tǒng)應(yīng)用,它的差別很大。最簡(jiǎn)單的存儲(chǔ)系統(tǒng)使用平板式的地址映射機(jī)制,地址空間的分配是固定的,系統(tǒng)中各部分都使用物理地址,這樣的處理器不帶

2022-04-20 09:23:59

硬件控制和協(xié)調(diào),最終實(shí)現(xiàn)SCSI協(xié)議、硬盤(pán)的控制和DMA傳輸?shù)取?duì)DSP微處理器的編程,需要完整掌握SCSI-3協(xié)議標(biāo)準(zhǔn)和FAS368M的命令集,工作量比較大,同時(shí)程序的優(yōu)劣也關(guān)系到系統(tǒng)的存儲(chǔ)速度和可靠性。由于篇幅限制,軟件設(shè)計(jì)本文不再多述。

2011-06-02 09:34:29

ESP32存儲(chǔ)系統(tǒng)分為幾部分呢?SPI flash的操作方法是怎樣的?

2022-01-14 07:11:32

的請(qǐng)求,還有一個(gè)仲裁器來(lái)協(xié)調(diào)各個(gè)DMA請(qǐng)求的優(yōu)先權(quán)。DMA 控制器和Cortex-M3核共享系統(tǒng)數(shù)據(jù)總線執(zhí)行直接存儲(chǔ)器數(shù)據(jù)傳輸。當(dāng)CPU和DMA同時(shí)訪問(wèn)相同的目標(biāo)(RAM或外設(shè))時(shí),DMA請(qǐng)求可能會(huì)

2015-01-13 14:02:03

stm32的dma控制器有多少個(gè)通道,DMA簡(jiǎn)介直接存儲(chǔ)器存取(DMA)用來(lái)提供在外設(shè)和存儲(chǔ)器之間或者存儲(chǔ)器和存儲(chǔ)器之間的高速數(shù)據(jù)傳輸。無(wú)須CPU干預(yù),數(shù)據(jù)可以通過(guò)DMA快速地移動(dòng),這就節(jié)省了CPU

2021-08-05 07:29:16

DMA控制器的主要特性有哪些?DMA控制器通道的配置過(guò)程該怎樣去完成呢?

2021-12-13 06:12:53

】:1引言在網(wǎng)絡(luò)存儲(chǔ)[1]應(yīng)用模式下,多種不同類(lèi)型的應(yīng)用共享存儲(chǔ)資源,這些應(yīng)用通常具有不同的優(yōu)先級(jí)和負(fù)載特征,而這里的共享資源[2]主要包括處理器、網(wǎng)卡帶寬、磁盤(pán)機(jī)械臂和緩存空間等四種,其中緩存是決定存儲(chǔ)系統(tǒng)性能的重要因素,這就要求存儲(chǔ)系統(tǒng)中的緩存管理單元應(yīng)能夠提供應(yīng)用全文下載

2010-04-24 09:43:47

到底什么是云存儲(chǔ)?云存儲(chǔ)系統(tǒng)的結(jié)構(gòu)是如何構(gòu)成的?云存儲(chǔ)有哪些技術(shù)前提?

2021-06-02 06:27:45

/tutorial01存儲(chǔ)系統(tǒng)這個(gè)tutorial使用的設(shè)計(jì)是一個(gè)簡(jiǎn)單的存儲(chǔ)系統(tǒng),包含系統(tǒng)總線、round-robin仲裁器、控制四個(gè)SRAM的存儲(chǔ)器控制器和兩個(gè)CPU。下圖顯示了該系統(tǒng)的原理圖。上圖

2022-11-04 11:10:21

這篇應(yīng)用筆記描述了怎么使用STM32F101xx 和 STM32F103xx的直接存儲(chǔ)器訪問(wèn)(DMA)控制器。STM32F101xx和STM32F103xx的DMA控制器、CortexTM-M3內(nèi)核

2023-10-10 08:20:48

設(shè)計(jì)高溫環(huán)境下(最高120°)基于FPGA的數(shù)據(jù)采集存儲(chǔ)系統(tǒng),就是通過(guò)傳感器采集數(shù)據(jù),通過(guò)FPGA來(lái)控制,把數(shù)據(jù)存儲(chǔ)到存儲(chǔ)芯片上,回頭可以通過(guò)接口讀取數(shù)據(jù)顯示在計(jì)算機(jī)上,求大師給我指導(dǎo),我急需整個(gè)系統(tǒng)的protel原理圖,請(qǐng)各位幫忙,我將感激不盡。最好有附件畫(huà)出整個(gè)原理圖,謝謝!

2012-10-29 21:37:12

14bit采樣精度、2GS/s采樣率、高達(dá)1000MB/s直接存儲(chǔ)速率、2TB存儲(chǔ)容量的中頻信號(hào)采集存儲(chǔ)。系統(tǒng)整體圖:系統(tǒng)硬件包括PXIe 3U 8slot機(jī)箱一個(gè)、PXIe控制器一個(gè)(帶機(jī)械磁盤(pán)

2016-08-16 13:58:43

基于SD卡的駕駛行為再現(xiàn)存儲(chǔ)系統(tǒng)設(shè)計(jì)摘要:本文以ABS 采集系統(tǒng)為基礎(chǔ),利用嵌入式技術(shù)設(shè)計(jì)了以SD 卡為存儲(chǔ)介質(zhì)的駕駛行為再現(xiàn)存儲(chǔ)系統(tǒng),對(duì)ABS 的數(shù)據(jù)進(jìn)行讀寫(xiě)操作。本系統(tǒng)采用了目前通用的通信方式

2009-05-17 11:54:45

針對(duì)航天測(cè)試系統(tǒng)的應(yīng)用需求,利用FPGA的設(shè)計(jì)微型數(shù)字存儲(chǔ)系統(tǒng)勢(shì)在必行,那我們具體該怎么做呢?

2019-08-01 08:14:33

的零部件撤底拆掉。拆裝零部件用了我兩個(gè)小時(shí)的時(shí)間,但安裝之后系統(tǒng)又開(kāi)始正常運(yùn)行了。看來(lái),以上的存儲(chǔ)問(wèn)題是隨主板附送的RAID控制器導(dǎo)致的。終于解決了我的存儲(chǔ)問(wèn)題。這個(gè)系統(tǒng)工作了很長(zhǎng)一段時(shí)間。現(xiàn)在我關(guān)心的是,如果2TB的在線存儲(chǔ)系統(tǒng)都滿了,我該如何備份。

2012-12-12 15:56:32

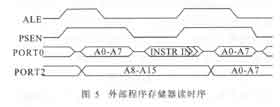

如何去設(shè)計(jì)微型數(shù)字存儲(chǔ)系統(tǒng)的硬件部分?如何去設(shè)計(jì)微型數(shù)字存儲(chǔ)系統(tǒng)的軟件部分?

2021-05-13 07:22:46

本文在FAST-40 SCSI協(xié)議基礎(chǔ)上,對(duì)實(shí)時(shí)高速數(shù)字視頻SCSI存儲(chǔ)系統(tǒng)的軟硬件進(jìn)行了設(shè)計(jì)。

2021-06-07 06:32:21

本文提出了基于SOPC(System On Programmable Chip)的設(shè)計(jì)方案[2],利 用其配置靈活、擴(kuò)展性強(qiáng)、接口豐富等優(yōu)點(diǎn),以Altera 公司的Cyclone II 系列FPGA 為基 礎(chǔ),設(shè)計(jì)傳感器節(jié)點(diǎn)數(shù)據(jù)采集存儲(chǔ)系統(tǒng),降低了設(shè)計(jì)的風(fēng)險(xiǎn),完善了傳感器節(jié)點(diǎn)功能要求。

2021-05-06 08:28:58

怎么實(shí)現(xiàn)基于VW2010的視頻存儲(chǔ)系統(tǒng)的設(shè)計(jì)?

2021-06-03 07:14:51

本文在前兩篇USART串口通信的基礎(chǔ)上,使用DMA控制器來(lái)實(shí)現(xiàn)串口通信文章目錄一、DMA1.DMA簡(jiǎn)介2.DMA主要特性3.部分代碼原理二、實(shí)驗(yàn)代碼三、實(shí)驗(yàn)結(jié)果四、總結(jié)五、參考資料一

2022-02-22 07:00:29

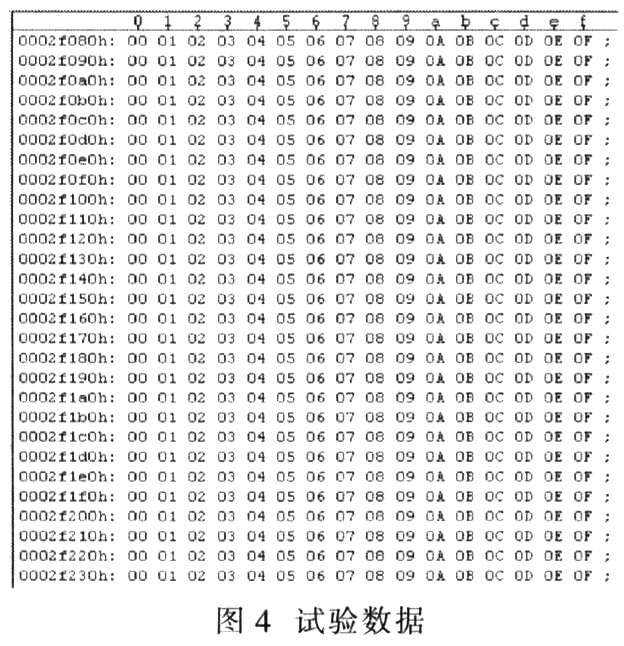

微型數(shù)字存儲(chǔ)系統(tǒng)的硬件設(shè)計(jì)微型數(shù)字存儲(chǔ)系統(tǒng)的軟件設(shè)計(jì)怎樣對(duì)微型數(shù)字存儲(chǔ)系統(tǒng)進(jìn)行驗(yàn)證?

2021-04-29 06:26:29

設(shè)計(jì)高溫環(huán)境下(最高120°)基于FPGA的數(shù)據(jù)采集存儲(chǔ)系統(tǒng),就是通過(guò)傳感器采集數(shù)據(jù),通過(guò)FPGA來(lái)控制,把數(shù)據(jù)存儲(chǔ)到存儲(chǔ)芯片上,回頭可以通過(guò)接口讀取數(shù)據(jù)顯示在計(jì)算機(jī)上,求大師給我指導(dǎo),我急需整個(gè)系統(tǒng)的protel原理圖,請(qǐng)各位幫忙,我將感激不盡。最好有附件畫(huà)出整個(gè)原理圖,謝謝!

2012-10-29 21:29:15

怎樣去設(shè)計(jì)一種MIPS寄存器文件呢?漢字字庫(kù)存儲(chǔ)系統(tǒng)是由哪些部分組成的?怎樣去設(shè)計(jì)呢?

2021-10-22 08:31:23

直接存儲(chǔ)器存取DMACPU太忙了,那DMA你來(lái)幫我吧,這樣很多事情CPU就不用停下來(lái)去管了。在DMA模式下,CPU只須向DMA控制器下達(dá)指令,讓DMA控制器來(lái)處理數(shù)據(jù)的傳送,數(shù)據(jù)傳送完畢再把信息反饋

2021-12-09 06:00:30

【作者】:張益;霍珊珊;【來(lái)源】:《清華大學(xué)學(xué)報(bào)(自然科學(xué)版)》2009年S2期【摘要】:針對(duì)當(dāng)前網(wǎng)絡(luò)存儲(chǔ)系統(tǒng)可生存性評(píng)估缺乏系統(tǒng)的評(píng)估指標(biāo)和量化評(píng)估方法的現(xiàn)狀,提出了量化評(píng)估指標(biāo)體系和基于多指標(biāo)

2010-04-24 09:43:16

為了實(shí)現(xiàn)SCSI協(xié)議和硬盤(pán)存儲(chǔ),一般需要有微處理器、DMA控制器、SCSI協(xié)議控制器、數(shù)據(jù)緩存器等硬件支持和相應(yīng)的軟件控制模塊。·微處理器用來(lái)控制設(shè)備中各部件的工作,實(shí)現(xiàn)設(shè)備本身的特定功能。該專(zhuān)用

2011-06-02 09:33:21

DMA(Direct Memory Access)的概念DMA方式不用處理器干預(yù)完成M與I/O間數(shù)據(jù)傳送。DMA期間系統(tǒng)總線由其它主模塊控

2008-12-09 11:03:56 50

50 傳統(tǒng)的訪問(wèn)控制算法采用有效帶寬進(jìn)行訪問(wèn)控制,效果并不理想。該文建立描述并發(fā)多媒體負(fù)載訪問(wèn)存儲(chǔ)系統(tǒng)的排隊(duì)論模型,提出基于統(tǒng)計(jì)學(xué)的存儲(chǔ)系統(tǒng)訪問(wèn)控制算法。在保證多媒

2009-03-28 09:57:26 16

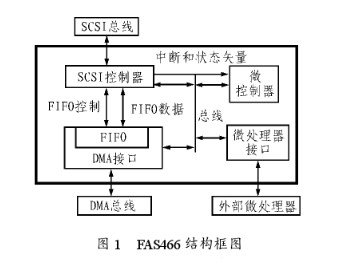

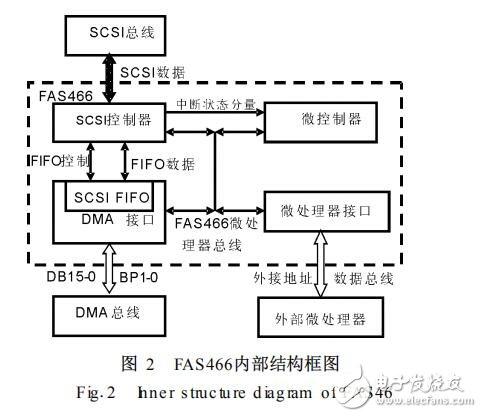

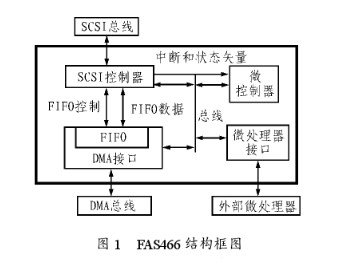

16 介紹QLogic公司最新的Fast結(jié)構(gòu)SCSI處理器FAS466的性能特點(diǎn)、內(nèi)部結(jié)構(gòu)及在國(guó)內(nèi)的應(yīng)用前景.

2009-04-30 14:54:05 22

22 基于FPGA的微型數(shù)字存儲(chǔ)系統(tǒng)設(shè)計(jì)

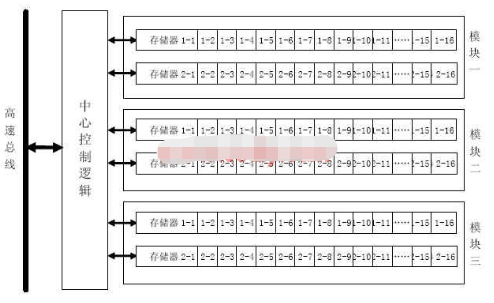

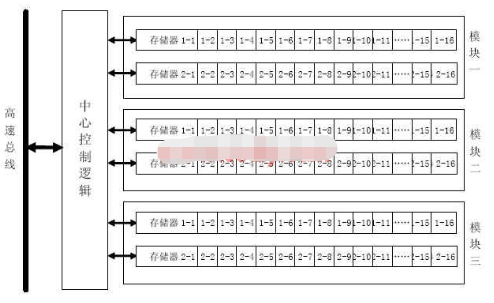

1 引言 針對(duì)航天測(cè)試系統(tǒng)的應(yīng)用需求,提出一種基于FPGA的微型數(shù)字存儲(chǔ)系統(tǒng)設(shè)計(jì)方案。該系統(tǒng)是在傳統(tǒng)存儲(chǔ)測(cè)試系統(tǒng)的基

2009-11-04 10:46:38 716

716

淺析嵌入式存儲(chǔ)系統(tǒng)設(shè)計(jì)方法

嵌入式存儲(chǔ)系統(tǒng)由嵌入式硬件和固化在硬件平臺(tái)中的嵌入式存儲(chǔ)系統(tǒng)軟件組成。傳統(tǒng)的小規(guī)模嵌入式存儲(chǔ)系統(tǒng),軟件多采用前后臺(tái)的方

2010-01-26 16:32:14 930

930

引言

DMA(Direct Memory Access,直接存儲(chǔ)器存取)是一種快速傳送數(shù)據(jù)的機(jī)制。DMA控制器能夠有效替代微處理器的加載/存儲(chǔ)指令,顯著提高系統(tǒng)的并行能力。DMA是在

2010-09-08 11:08:36 2281

2281

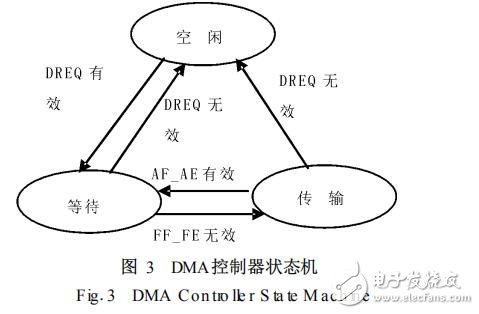

在以SD卡為圖像存儲(chǔ)器件的圖像協(xié)處理器中,基帶芯片和SD卡控制器在速度上的差異經(jīng)常會(huì)導(dǎo)致數(shù)據(jù)傳輸錯(cuò)誤。為解決此問(wèn)題,設(shè)計(jì)了一種可適應(yīng)多種時(shí)序情況的DMA控制器。該DMA控制器的狀態(tài)機(jī),一方面對(duì)基帶芯片和SD卡控制器的操作請(qǐng)求進(jìn)行仲裁,在響應(yīng)基帶芯片請(qǐng)

2011-01-15 17:06:20 0

0 本文采用W78E516B單片機(jī)為核心來(lái)外擴(kuò)FM1808存儲(chǔ)器的存儲(chǔ)電路,并成功地運(yùn)用到了綜合驗(yàn)光儀的數(shù)據(jù)存儲(chǔ)系統(tǒng)中。該存儲(chǔ)系統(tǒng)降低了電路的復(fù)雜性,保證了數(shù)據(jù)的可靠,在整個(gè)綜合驗(yàn)光儀的使用中

2011-01-18 09:58:24 1655

1655

分析當(dāng)前網(wǎng)絡(luò)存儲(chǔ)系統(tǒng)存在的問(wèn)題,給出一種基于企業(yè)卷管理系統(tǒng)技術(shù)的帶外虛擬網(wǎng)絡(luò)存儲(chǔ)系統(tǒng)基本結(jié)構(gòu)。分別闡述該存儲(chǔ)系統(tǒng)的客戶端、內(nèi)部數(shù)據(jù)的讀/寫(xiě)操作、存儲(chǔ)系統(tǒng)在線存儲(chǔ)容量

2011-05-18 18:50:31 38

38 本文利用“FPGA+單片機(jī)”作為存儲(chǔ)控制器,采用基于LZW算法的數(shù)據(jù)壓縮技術(shù),以SDRAM作為周期存儲(chǔ)和緩存,SD卡作為最終存儲(chǔ)載體,實(shí)現(xiàn)車(chē)載CAN總線記錄儀實(shí)現(xiàn)大容量存儲(chǔ)系統(tǒng)。

2011-09-08 16:24:59 2170

2170

如果將原來(lái)所有的硬盤(pán)全部替換為固態(tài)硬盤(pán),那存儲(chǔ)系統(tǒng)肯定會(huì)出現(xiàn)問(wèn)題。存儲(chǔ)控制器剛剛適應(yīng)固態(tài)硬盤(pán),系統(tǒng)可以使用多少個(gè)固態(tài)硬盤(pán)?

2011-12-22 14:21:41 733

733 高速圖像存儲(chǔ)系統(tǒng)中SDRAM控制器的實(shí)現(xiàn)

2016-08-29 15:02:03 10

10 基于FPGA的多通道圖像采集存儲(chǔ)系統(tǒng)設(shè)計(jì)

2016-08-30 15:10:14 11

11 基于閃存的圖像存儲(chǔ)系統(tǒng)設(shè)計(jì),又需要的下來(lái)看看

2016-09-22 14:08:55 13

13 NetApp_E5600_存儲(chǔ)系統(tǒng)

2016-12-28 09:33:36 0

0 NetApp_E5500_存儲(chǔ)系統(tǒng)

2016-12-28 09:33:36 0

0 NetApp_E2700_存儲(chǔ)系統(tǒng)

2016-12-29 12:01:01 0

0 NetApp_FAS8080存儲(chǔ)手冊(cè)

2016-12-29 12:01:01 0

0 NetApp_FAS8000系列存儲(chǔ)手冊(cè)

2016-12-29 12:01:01 0

0 NetApp_FAS2500系列存儲(chǔ)手冊(cè)

2016-12-29 12:01:01 0

0 NetApp_FAS2500_系列存儲(chǔ)手冊(cè)

2016-12-29 12:01:01 0

0 NetApp_FAS2600系列混合存儲(chǔ)系統(tǒng)

2016-12-29 12:01:01 0

0 NetApp_FAS_純閃存存儲(chǔ)手冊(cè)

2016-12-29 12:01:01 0

0 本文中介紹的故障恢復(fù)主要是只單機(jī)存儲(chǔ)系統(tǒng)中的故障恢復(fù),就是只有一臺(tái)電腦,與之相對(duì)的是分布式存儲(chǔ)系統(tǒng),暫且不談。

2018-06-10 01:41:00 777

777 為了避免PCIe傳輸過(guò)程中PIO寫(xiě)延時(shí)、主機(jī)與嵌入式處理系統(tǒng)交互次數(shù)過(guò)多等問(wèn)題對(duì)于傳輸帶寬的影響,設(shè)計(jì)了一種基于命令緩沖機(jī)制的直接存儲(chǔ)訪問(wèn)( DMA)控制器以提高傳輸帶寬利用率。采用FPGA端內(nèi)部

2017-12-05 19:00:45 2

2 在某些單片機(jī)應(yīng)用系統(tǒng)中,往往需要解決外部設(shè)備與存儲(chǔ)貯器之間快速傳送數(shù)據(jù)的問(wèn)題。為此,本文研究了DMA控制器8237與單片機(jī)8031的接口技術(shù)。

2017-12-06 11:28:42 2995

2995

DMA控制器是常見(jiàn)的總線設(shè)備之一,很多廠商都有自己的DMA控制器IP核。比如嵌入式處理器的龍頭ARM公司就有自己的DMA控制器解決方案提供給客戶,另外像Freescale,F(xiàn)ujitsu等芯片

2017-12-06 13:41:59 3329

3329

詳細(xì)地分析了PC/AT機(jī)系統(tǒng)的DMA(直接存儲(chǔ)器存取)控制器結(jié)構(gòu)及其傳輸方式,并給出了C語(yǔ)言編程實(shí)例。

2017-12-06 16:12:57 5092

5092

DMA(Direct Memory Access)

控制器是一種在

系統(tǒng)內(nèi)部轉(zhuǎn)移數(shù)據(jù)的獨(dú)特外設(shè),可以將其視為一種能夠通過(guò)一組專(zhuān)用總線將內(nèi)部和外部

存儲(chǔ)器與每個(gè)具有

DMA能力的外設(shè)連接起來(lái)的

控制器。它之所以屬于外設(shè),是因?yàn)樗窃谔幚砥鞯木幊?b class="flag-6" style="color: red">控制下來(lái) 執(zhí)行傳輸?shù)摹?/div>

2017-12-06 19:19:12 3458

3458 DMA控制器是一種在

系統(tǒng)內(nèi)部轉(zhuǎn)移數(shù)據(jù)的獨(dú)特外設(shè),可以將其視為一種能夠通過(guò)一組專(zhuān)用總線將內(nèi)部和外部

存儲(chǔ)器與每個(gè)具有

DMA能力的外設(shè)連接起來(lái)的

控制器。它之所以屬于外設(shè),是因?yàn)樗窃谔幚砥鞯木幊?b class="flag-6" style="color: red">控制下來(lái) 執(zhí)行傳輸?shù)摹?/div>

2017-12-07 08:51:27 2024

2024

為了具體介紹本多通道 DMA 控制器的設(shè)計(jì)方案,下面首先對(duì)基于 Crossbar 的多通道 DMA 控制器的工作原理進(jìn)行詳細(xì)分析,接著具體說(shuō)明各個(gè)模塊的設(shè)計(jì)實(shí)現(xiàn),然后對(duì)設(shè)計(jì)進(jìn)行驗(yàn)證和分析比較實(shí)驗(yàn)結(jié)果,并進(jìn)行總結(jié)。

2017-12-07 09:37:22 4585

4585

DMA既可以指內(nèi)存和外設(shè)直接存取數(shù)據(jù)這種內(nèi)存訪問(wèn)的計(jì)算機(jī)技術(shù),又可以指實(shí)現(xiàn)該技術(shù)的硬件模塊(對(duì)于通用計(jì)算機(jī)PC而言,DMA控制邏輯由CPU和DMA控制接口邏輯芯片共同組成,嵌入式系統(tǒng)的DMA控制器內(nèi)建在處理器芯片內(nèi)部,一般稱為DMA控制器,DMAC)。

2017-12-07 10:23:24 15810

15810

DMA(Direct Memory Access)

控制器是一種在

系統(tǒng)內(nèi)部轉(zhuǎn)移數(shù)據(jù)的獨(dú)特外設(shè),可以將其視為一種能夠通過(guò)一組專(zhuān)用總線將內(nèi)部和外部

存儲(chǔ)器與每個(gè)具有

DMA能力的外設(shè)連接起來(lái)的

控制器。它之所以屬于外設(shè),是因?yàn)樗窃谔幚砥鞯木幊?b class="flag-6" style="color: red">控制下來(lái) 執(zhí)行傳輸?shù)摹?/div>

2017-12-07 14:43:14 3368

3368

DMA控制器是一種在

系統(tǒng)內(nèi)部轉(zhuǎn)移數(shù)據(jù)的獨(dú)特外設(shè),可以將其視為一種能夠通過(guò)一組專(zhuān)用總線將內(nèi)部和外部

存儲(chǔ)器與每個(gè)具有

DMA能力的外設(shè)連接起來(lái)的

控制器。它之所以屬于外設(shè),是因?yàn)樗窃谔幚砥鞯木幊?b class="flag-6" style="color: red">控制下來(lái) 執(zhí)行傳輸?shù)摹?/div>

2017-12-07 15:41:09 3168

3168

一般而言,DMA控制器的功能與結(jié)構(gòu)是由本單位特定的系統(tǒng)結(jié)構(gòu)決定的。但是作為IP而言,DMA控制器又要有其一般性。DMA是指外部設(shè)備直接對(duì)計(jì)算機(jī)存儲(chǔ)器進(jìn)行讀寫(xiě)操作的I/O方式。這種方式下數(shù)據(jù)的讀寫(xiě)無(wú)需

2017-12-07 15:48:19 5886

5886

DMA既可以指內(nèi)存和外設(shè)直接存取數(shù)據(jù)這種內(nèi)存訪問(wèn)的計(jì)算機(jī)技術(shù),又可以指實(shí)現(xiàn)該技術(shù)的硬件模塊(對(duì)于通用計(jì)算機(jī)PC而言,DMA控制邏輯由CPU和DMA控制接口邏輯芯片共同組成,嵌入式系統(tǒng)的DMA控制器內(nèi)建在處理器芯片內(nèi)部,一般稱為DMA控制器,DMAC)。

2017-12-07 16:08:38 5155

5155

該文檔描述了在TMS3VC5505/5504數(shù)字信號(hào)處理器(DSP)上可用的直接存儲(chǔ)器存取(DMA)控制器的特點(diǎn)和操作。此DMA控制器允許內(nèi)部存儲(chǔ)器、外部存儲(chǔ)器和外圍設(shè)備之間的數(shù)據(jù)不受干預(yù)地發(fā)生。

2018-04-26 10:34:35 3

3 本文主要介紹了PIC24F系列參考手冊(cè)之直接存儲(chǔ)器訪問(wèn)控制器(DMA)。

2018-06-06 17:28:00 5

5 TMS320C64x+網(wǎng)絡(luò)課程2——存儲(chǔ)系統(tǒng),其中包括:存儲(chǔ)控制器,緩存特異性, Internal DMA。此網(wǎng)絡(luò)培訓(xùn)針對(duì)C64x+,每次一個(gè)專(zhuān)題,此視頻由DSP高性能部門(mén)技術(shù)支持工程師為您全程指導(dǎo),敬請(qǐng)期待。

2018-06-26 05:42:00 4023

4023

說(shuō)一說(shuō)AI技術(shù)在存儲(chǔ)中的應(yīng)用,和對(duì)存儲(chǔ)系統(tǒng)帶來(lái)的創(chuàng)新性改進(jìn)。

2018-10-24 15:41:58 4084

4084 關(guān)鍵詞:CCD , 存儲(chǔ)系統(tǒng) 由于高幀頻、大面陣CCD數(shù)字相機(jī)的圖像數(shù)據(jù)量非常巨大,存儲(chǔ)流量超過(guò)50MBps。而且圖像輸出速率也比較高,所以高速圖像數(shù)據(jù)的實(shí)時(shí)記錄是一個(gè)不易解決的問(wèn)題。高幀頻、大面

2019-02-14 15:08:01 302

302 一個(gè)DMA控制器,實(shí)際上是采用DMA方式的外圍設(shè)備與系統(tǒng)總線之間的接口電路,這個(gè)接口電路是在中斷接口的基礎(chǔ)上再加DMA機(jī)構(gòu)組成。習(xí)慣上將DMA方式的接口電路稱為DMA控制器。

2019-04-01 16:08:06 10025

10025 據(jù)了解,全新的Primera存儲(chǔ)系統(tǒng)實(shí)現(xiàn)了存儲(chǔ)介質(zhì)從HDD到SSD的質(zhì)變,并做到了前所未有的100% SLA。而通過(guò)存儲(chǔ)協(xié)議、互聯(lián)架構(gòu)、控制器、OS和應(yīng)用層面的創(chuàng)新,Primera也實(shí)現(xiàn)了在性能、體驗(yàn)和感知層面的全面超越。

2019-08-09 10:28:12 450

450 DMA(Direct Memory Access)

控制器是一種在

系統(tǒng)內(nèi)部轉(zhuǎn)移數(shù)據(jù)的獨(dú)特外設(shè),可以將其視為一種能夠通過(guò)一組專(zhuān)用總線將內(nèi)部和外部

存儲(chǔ)器與每個(gè)具有

DMA能力的外設(shè)連接起來(lái)的

控制器。它之所以屬于外設(shè),是因?yàn)樗窃谔幚砥鞯木幊?b class="flag-6" style="color: red">控制下來(lái) 執(zhí)行傳輸?shù)摹?/div>

2019-11-15 10:25:56 12384

12384 FAS466 微處理器接口可以連接多種微處理器或 DSP;而DMA接口則主要與外部DMA控制器連接?組成DMA通道;SCSI 總線接口可以連接各種 SCSI 設(shè)備。其中,SCSI 控制器與微控制器分別是 SCSI 協(xié)議的執(zhí)行中心和控制核心。

2020-08-10 14:34:53 1242

1242

分布式存儲(chǔ)系統(tǒng)是大數(shù)據(jù)技術(shù)學(xué)習(xí)過(guò)程中會(huì)經(jīng)常接觸到的一個(gè)工具,而今天我們就一起來(lái)了解一下,常見(jiàn)的一些分布式存儲(chǔ)系統(tǒng)都有哪些類(lèi)型。

2020-11-09 10:41:01 27478

27478 近日,中科曙光在北京發(fā)布了基于區(qū)塊鏈存儲(chǔ)應(yīng)用打造的一款智能高效的專(zhuān)屬存儲(chǔ)系統(tǒng)——區(qū)塊鏈存儲(chǔ)系統(tǒng)ChainStor。ChainStor沿用了曙光多年技術(shù)積累的分布式存儲(chǔ)架構(gòu),底層核心是基于裸設(shè)備的數(shù)據(jù)

2020-12-31 11:36:00 13313

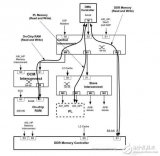

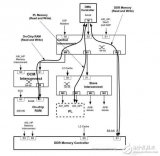

13313 SDRAM作為大容量存儲(chǔ)器在高速圖像處理中具有很大的應(yīng)用價(jià)值。但由于SDRAM的結(jié)構(gòu)和SRAM不同,其控制比較復(fù)雜。文章詳細(xì)介紹了 SDRAM存儲(chǔ)器的結(jié)構(gòu)、接口信號(hào)和操作方法,以及 SDRAM控制器

2021-01-26 15:30:52 13

13 實(shí)現(xiàn)SCSI協(xié)議和硬盤(pán)存儲(chǔ),通常需要有微處理器、DMA控制器、SCSI協(xié)議控制器、數(shù)據(jù)緩存器等硬件支持和相應(yīng)的軟件控制模塊。而本系統(tǒng)。DMA控制通過(guò)對(duì)FPGA編程來(lái)實(shí)現(xiàn)。圖像數(shù)據(jù)存儲(chǔ)系統(tǒng)結(jié)構(gòu)圖如圖l所示。

2021-03-16 14:52:10 2076

2076

AN4104_STM32F0xx的DMA控制器的使用

2022-11-21 08:11:37 2

2 DMA簡(jiǎn)介DMA控制器的作用不僅在增強(qiáng)系統(tǒng)性能并減少處理器的中斷生成,而且還針對(duì)32位MCU應(yīng)用程序?qū)iT(mén)優(yōu)化設(shè)計(jì)。DMA控制器為存儲(chǔ)器到存儲(chǔ)器,存儲(chǔ)器到外設(shè)和外設(shè)到存儲(chǔ)器的傳輸提供了7個(gè)通道。每個(gè)

2024-02-22 08:13:55 148

148

正在加载...

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論