隨著網(wǎng)絡(luò)的飛速發(fā)展,人們可獲取的信息量日益增長,數(shù)據(jù)的處理及存儲(chǔ)速率的要求也越來越高。萬兆網(wǎng)(10Gb以太網(wǎng))的普及,高速存儲(chǔ)設(shè)備的應(yīng)用(如DDR2,傳輸速率可達(dá)800M)對系統(tǒng)帶寬帶來極大的挑戰(zhàn)。

伴隨著FPGA技術(shù)的大規(guī)模的應(yīng)用,越來越多的大型系統(tǒng)采用PCI Express總線連接FPGA處理板和PC以實(shí)現(xiàn)數(shù)據(jù)的交互。盡管很多FPGA公司推出了基于PCI Express協(xié)議相關(guān)的IP硬核,但是掌握這些硬核的使用需要對PCI Express 協(xié)議具有一定的了解,而且直接使用硬核,帶寬很小,開發(fā)難度大,移植性差等缺點(diǎn)這些都是造成目前PCI Express接口設(shè)計(jì)的瓶頸。為了降低開發(fā)難度,提高帶寬和移植性,許多現(xiàn)有的方案是在PCI Express硬核中加入高速DMA控制器單元,以此來達(dá)到設(shè)計(jì)需求。

文中介紹了一種基于高速的I/O串行互聯(lián)技術(shù),PCI-Express(簡稱PCIe),提出了在系統(tǒng)設(shè)計(jì)中基于FPGA的PCIe總線接口設(shè)計(jì)及應(yīng)用于該總線的高速DMAEngine設(shè)計(jì)方案。

PCI Express總線簡介

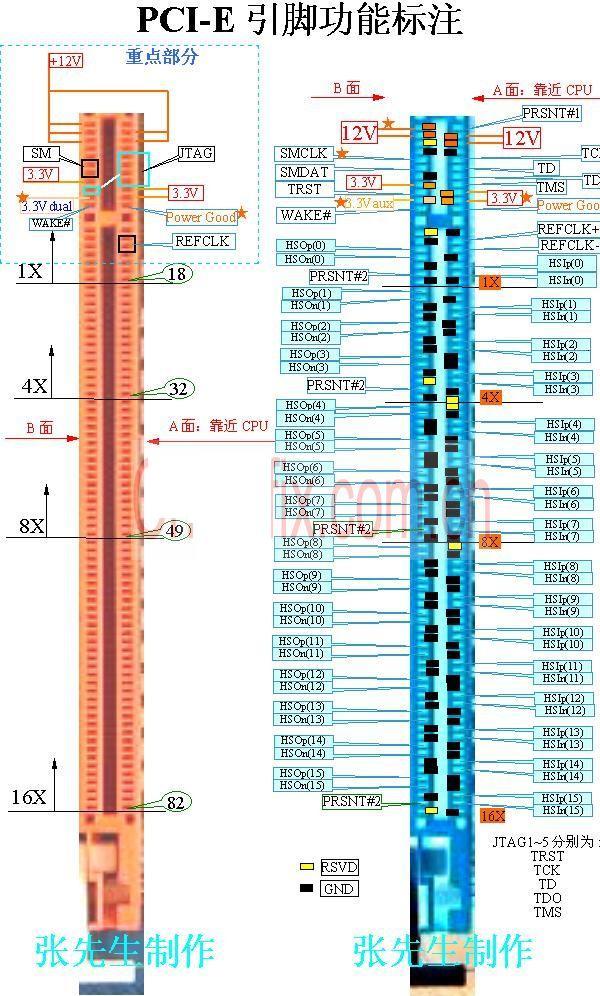

PCI Express總線技術(shù)是取代PCI的第三代I/O技術(shù)。PCIExpress總線是為計(jì)算機(jī)和通訊平臺(tái)定義的一種高性能、通用I/O互聯(lián)總線。至今已經(jīng)發(fā)布了3個(gè)正式版本:PCI Express 1.0、PCIExpress 2.0、PCI Express 3.0。單向單通道帶寬分別為:250MB/s, 500MB/s, 1GB/s。PCI Express體系結(jié)構(gòu)的設(shè)計(jì)非常先進(jìn),采用了類似網(wǎng)絡(luò)體系結(jié)構(gòu)中OSI分層體系結(jié)構(gòu)設(shè)計(jì)方案,如圖2.1所示。按照協(xié)議規(guī)范,PCI Express總線的層次結(jié)構(gòu)分為物理層(Physical Layer)、數(shù)據(jù)鏈路層(Data Link Layer)和事物層(Transaction Layer)體系結(jié)構(gòu)。

在性能方面,相比PCI總線,PCI Express總線具有以下特點(diǎn):

(1)在數(shù)據(jù)傳輸模式上,PCI Express 采用差分串行傳輸方式,一條PCI Express通道(稱為PCI Express X1)由2對差分信號(hào)線來實(shí)現(xiàn)數(shù)據(jù)的發(fā)送和接收。

(2)PCI Express具有高速串行通信接口所特有的時(shí)鐘恢復(fù)核心,將時(shí)鐘融合到傳輸?shù)臄?shù)據(jù)中,這樣既減去了時(shí)鐘管腳,又能大大提高傳輸速度,突破了并行傳輸帶寬的瓶頸。

(3)PCI Express是采用點(diǎn)到點(diǎn)的互連方法,每個(gè)設(shè)備都由獨(dú)立的鏈路連接,獨(dú)享帶寬,大大提高傳輸效率。

(4)具有很好的靈活性,一個(gè)PCI Express物理連接可以根據(jù)實(shí)際需要配置成X1,X2,X4,X8,X16 及X32鏈路模式。因此傳輸?shù)乃俣纫簿拖鄳?yīng)的成倍增長。

(5)PCI Express傳輸?shù)臄?shù)據(jù)以協(xié)議定義的數(shù)據(jù)包(packet)的形式進(jìn)行傳輸,保障了數(shù)據(jù)傳輸?shù)耐暾院涂煽啃浴?/p>

(6)PCI Express協(xié)議加入了數(shù)據(jù)重傳機(jī)制,提高了數(shù)據(jù)傳輸?shù)目煽啃浴?/p>

正是由于PCI Express的這些技術(shù)特點(diǎn),使得其越來越廣泛的應(yīng)用在計(jì)算機(jī)系統(tǒng)架構(gòu)及海量數(shù)據(jù)傳輸接口領(lǐng)域,特別是在加入了高速DMA控制器傳輸方式下,PCI Express帶寬及傳輸效率大大提高,因此在高速系統(tǒng)領(lǐng)域具有廣闊的前景。

FPGA系統(tǒng)設(shè)計(jì)方案

傳統(tǒng)FPGA設(shè)計(jì)方案

傳統(tǒng)FPGA并不具備LVDS信號(hào)驅(qū)動(dòng)能力。一般以PEX8311橋接芯片實(shí)現(xiàn)PCIe物理層接口,再配合CPLD實(shí)現(xiàn)用戶邏輯設(shè)計(jì)。PEX8311提供2個(gè)端口,一個(gè)為兼容PCIExpress1.0標(biāo)準(zhǔn)的PCIe接口,另一個(gè)為LocalBus總線接口,用于與CPLD相連。LocalBus總線工作于66MHz時(shí)鐘,32-bit總線寬度,可以提供266MB/s帶寬。同時(shí),PEX8311還提供了2組DMA通道。使用PEX8311可以方便地從PCI平滑過渡到PCIe,從而降低開發(fā)成本,因此被廣泛使用。

然而,PEX8311并不能有效發(fā)揮出PCIe高帶寬優(yōu)勢,也缺乏可配置性和靈活性,難以提高系統(tǒng)整體性能。

基于PCIe硬核接口設(shè)計(jì)

Xilinx新推出Virtex-6系列的FPGA,集成了PCIeIP硬核模塊。該模塊兼容PCIExpress2.0標(biāo)準(zhǔn)分層協(xié)議(為物理層、數(shù)據(jù)鏈路層和事物層,又稱傳輸層),提供了系統(tǒng)接口(SYS)、外部傳輸接口(PCIEXP)、配置接口(CFG)、事物接口(TRN)和物理鏈路接口(PL)。其Virtex-6GTX可配置高速串行傳輸器為PCIe信號(hào)可靠傳輸提供了保障。文中便是針對該硬核的事物層提出片上系統(tǒng)的PCIe設(shè)計(jì)方案。

PCI-Express接口及應(yīng)用層設(shè)計(jì)

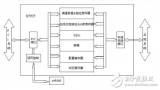

一個(gè)基本的高速數(shù)據(jù)采集系統(tǒng),由微處理器(CPU)、FPGA和外部存儲(chǔ)器等組成。CPU與FPGA通過PCIe總線進(jìn)行數(shù)據(jù)傳輸,F(xiàn)PGA通過DMA方式對外部存儲(chǔ)器進(jìn)行數(shù)據(jù)讀寫操作。文中給出基于PCIex1傳輸方式的接口設(shè)計(jì)方案。

PCIe接口及事物層設(shè)計(jì)

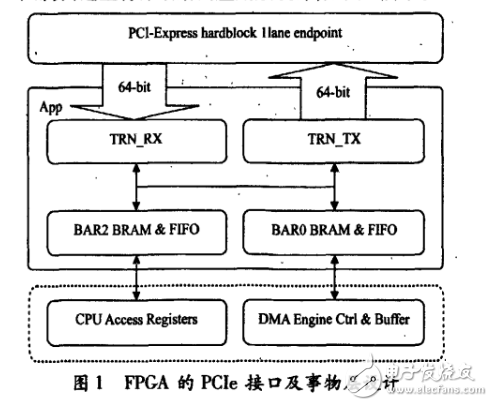

較之使用PEX8311橋接芯片的系統(tǒng)設(shè)計(jì),采用基于Xilinx的IP核的設(shè)計(jì)方案,用戶可以根據(jù)自己的需求靈活設(shè)計(jì)面向事物層接口電路,并方便加入特殊功能,如與內(nèi)部總線連接、實(shí)現(xiàn)DMA傳輸?shù)取T撛O(shè)計(jì)充分利用FPGA集成度高、可配置性強(qiáng)等特點(diǎn)來發(fā)揮PCIe接口性能。FPGA的PCIe接口設(shè)計(jì)包括XilinxPCIe端點(diǎn)硬核和面向事物層的應(yīng)用邏輯設(shè)計(jì)2個(gè)部分,這里將詳細(xì)給出應(yīng)用層設(shè)計(jì),如圖1所示。

XilinxPCIe硬核支持64-bit數(shù)據(jù)通路,分別用于發(fā)送和接收數(shù)據(jù)。該硬核提供6個(gè)32-bit基地址寄存器BAR0~BAR5(BassAddressRegister,簡稱BAR),可以根據(jù)用戶設(shè)計(jì)需求進(jìn)行配置。在本設(shè)計(jì)中使用BAR0和BAR1組成一組64-bit地址空間,用于存儲(chǔ)外部CPU訪問FPGA內(nèi)部寄存器地址。使用BAR2和BAR3組成另一組64-bit地址空間,用于存儲(chǔ)DMAEngine控制器和緩存器地址。通過判斷trn_rbar_hit_n[6:0]來區(qū)分BAR0和BAR2,其主要代碼如下:

? ?

‘TRN _RX_M EM _RD64_DW 1DW 2: begin

? ?

req_bar0_o 《 = ~trn_rbar_hit_n_q [ 0 ] ; req_bar2_o 《 = ~trn_rbar_hit_n_q [ 2 ] ;

? ?

end

以外部CPU讀FPGA內(nèi)部寄存器為例,F(xiàn)PGA將收到的PCIe總線上數(shù)據(jù)幀經(jīng)由硬核的事物層,以64-bit帶寬送出,應(yīng)用層通過TRN_RX接收狀態(tài)機(jī)來判斷請求訪問的地址空間,然后將請求數(shù)據(jù)緩寫入一個(gè)雙端口的req_fifo;用戶邏輯通過讀取req_fifo,將有效的寄存器數(shù)據(jù)寫入另一個(gè)雙端口data_fifo中,最后通過TRN_TX發(fā)送狀態(tài)機(jī)發(fā)送給硬核事物層。

基于PCIe的DMAEngine設(shè)計(jì)

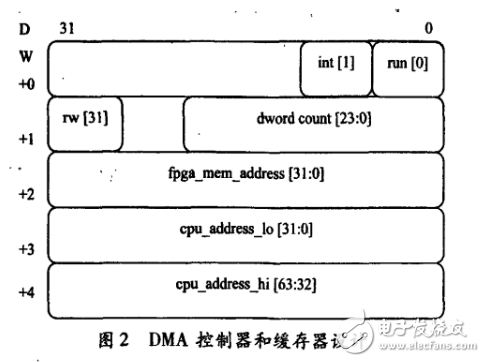

通過DMA訪問外部存儲(chǔ)器的最大優(yōu)勢在于CPU在配置完DMAEngine后可以繼續(xù)其他指令操作,DMAEngine會(huì)通過請求PCIe總線中斷的方式,來完成數(shù)據(jù)傳輸。本設(shè)計(jì)將PCIeBAR0地址空間存儲(chǔ)DMAEngine控制和緩存器地址,其定義如圖2所示。

DWORD0[0],run,寫1開啟DMA;

DWORD0[1],int,寫1開啟DMA中斷方式;

DWORD1[31]rw,寫1讀fpga外部存儲(chǔ)器;

DWORD1[23:0]dwordcount,DMA操作數(shù)據(jù)個(gè)數(shù),以dword為單位;

DWORD2[31:0]fpga_mem_address,fpga外部存儲(chǔ)器地址;

DWORD3[31:0]cpu_address_lo,cpu低32位地址;

DWORD4[31:0]cpu_address_h,icpu高32位地址。

修改PCIe數(shù)據(jù)幀類型(tlp_type《=trn_rd[62:56]),加入DMA數(shù)據(jù)幀,使其有別于對BAR的讀寫操作,部分代碼如下:

`efineTRN_RX_DMA_TLP_TYPE 7.b10_01010;/*DMA

數(shù)據(jù)類型*/

d`efineTRN_RX_DMA_DATA1 10.b01_0000_0000;/*

DMA操作狀態(tài)*/

,,

case(state)

R`ST:begin

,,

case(tlp_type)

,,

T`RN_RX_DMA_TLP_TYPE:begin

,,

state《=T`RN_RX_DMA_DATA1;

end

,,

T`RN_RX_DMA_DATA1:begin ,,

end,,

endcase

以同樣的方式在TRN_TX狀態(tài)機(jī)中加入DMA請求,其代碼如下:

d`efineTRN_TX_DMA_REQ 10.b01_0000_0000;

,,

case(state)

R`ST:begin

if(dma_tlp_ready)begin/*DMAEngine準(zhǔn)備好讀操

作數(shù)據(jù)幀*/

state《=T`RN_TX_DMA_REQ;

dma_tlp_rd_en《=1.b1; /*DMA緩存讀使能

*/

end

elseif(,,)

,,

end

,,

T`RN_TX_DMA_REQ:begin

,,

if(~tlp_dma_data_eof)/*

數(shù)據(jù)幀結(jié)束標(biāo)志位*/

state《=T`RN_TX_DONE;

els

state《=T`RN_TX_DMA_REQ;

end

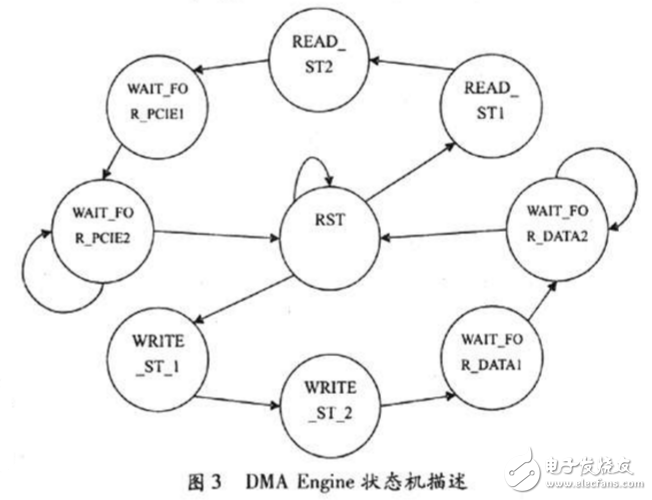

FPGA的DMAEngine狀態(tài)轉(zhuǎn)移圖如圖3所示,分DMA讀操作和寫操作2部分。DMAEngine處于RST狀態(tài)時(shí),通過讀取DMA信息標(biāo)識(shí)符來判斷當(dāng)前是否處于空閑狀態(tài),并從FPGA內(nèi)部RAM中讀取DMA控制信息(讀或?qū)懀⑦M(jìn)入相應(yīng)狀態(tài)READ_ST或WRITE_ST。以CPU寫FPGA外部存儲(chǔ)器為例,CPU通過PCIe總線寫B(tài)AR0地址數(shù)據(jù)來配置并開啟DMAEngine。FPGA將發(fā)出對CPU的DMA讀請求,然后等待CPU發(fā)送DMA數(shù)據(jù)。此時(shí)DMAEngine處于WAIT_FOR_DATA狀態(tài),等待來自PCIe接口的DMA數(shù)據(jù)包。同樣,CPU讀FPGA外部存儲(chǔ)器時(shí),F(xiàn)PGA將發(fā)出對CPU的DMA寫請求,并當(dāng)DMA完成讀操作后,等待PCIe接口發(fā)送DMA數(shù)據(jù)包,并由中斷標(biāo)志位判斷是否開啟PCIe中斷。

仿真及測試結(jié)果

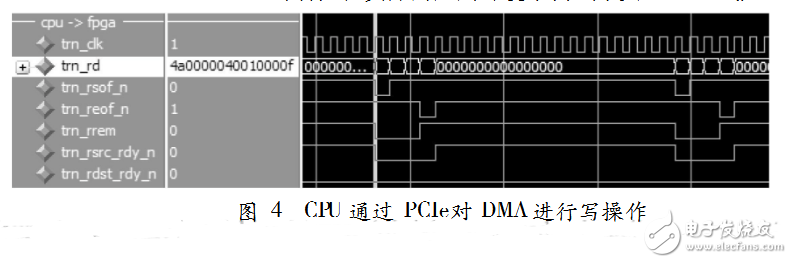

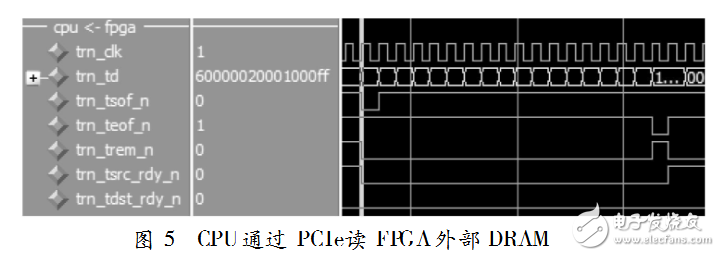

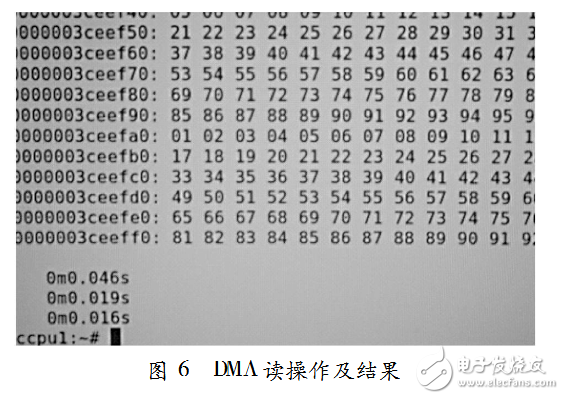

為了測試該DMAEngine設(shè)計(jì),對FPGA外部64-bitDDR2DRAM進(jìn)行32個(gè)dwords(128bytes)讀與寫操作,得到的仿真波形如圖4和圖5所示。圖4是對DMA進(jìn)行寫操作的PCIe事物層接口波形。圖5是對DMA進(jìn)行讀操作的PCIe事物層接口波形。該設(shè)計(jì)方案在questasmi6.3f下驗(yàn)證通過。可以估算出一次PCIex1寫操作為1720Mb/s,讀為1684Mb/s。同樣,在實(shí)際的應(yīng)用環(huán)境中測試本文DMAEngine設(shè)計(jì),也獲得比較好的結(jié)果。圖6就是系統(tǒng)以本文DMA方式進(jìn)行4096bytes讀外部存儲(chǔ)器的結(jié)果。

FPGA較ASIC的強(qiáng)大之處,在于靈活性和可配置性。文中憑借XilinxPCIe硬核,很好地實(shí)現(xiàn)了PCIex1總線接口,并在此基礎(chǔ)上加入高速DMAEngine設(shè)計(jì),可以有效地提高系統(tǒng)數(shù)據(jù)存儲(chǔ)效率。

該設(shè)計(jì)方案通過簡單修改也同樣適用于32-bit帶寬傳輸系統(tǒng)設(shè)計(jì)。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論