DMA(Direct Memory Access)控制器是一種在系統內部轉移數據的獨特外設,可以將其視為一種能夠通過一組專用總線將內部和外部存儲器與每個具有DMA能力的外設連接起來的控制器。它之所以屬于外設,是因為它是在處理器的編程控制下來 執行傳輸的。

DMA控制器特點:

8個獨立的通道,4個可用于PL—PS間數據管理,每個通道有1024Byte的MFIFO;

使用CPU_2x 時鐘搬運數據,CPU_2x = (CPU frq/6)*2;

執行自定義內存區域內的DMA指令運行DMA;

AHB控制寄存器支持安全和非安全模式;

每個通道內置4字Cache;

可以訪問SoC的以下映射物理地址:

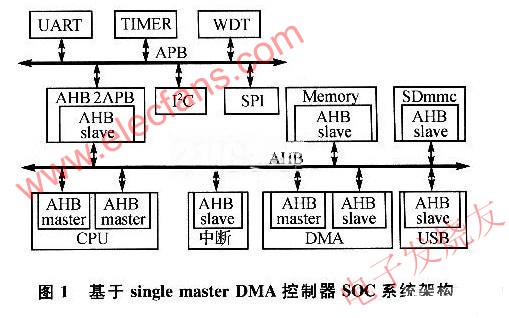

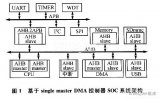

DDR、OCM、PL、Linear QSPI Read、SMC和M_AXI_GP設備,訪問設備的互聯結構如圖1所示。

圖一

從圖1可以看出DMA控制器可以訪問連接到Central Interconnect上的所有設備,并提供了四個通道的外設管理接口可用于控制PL的數據搬運。

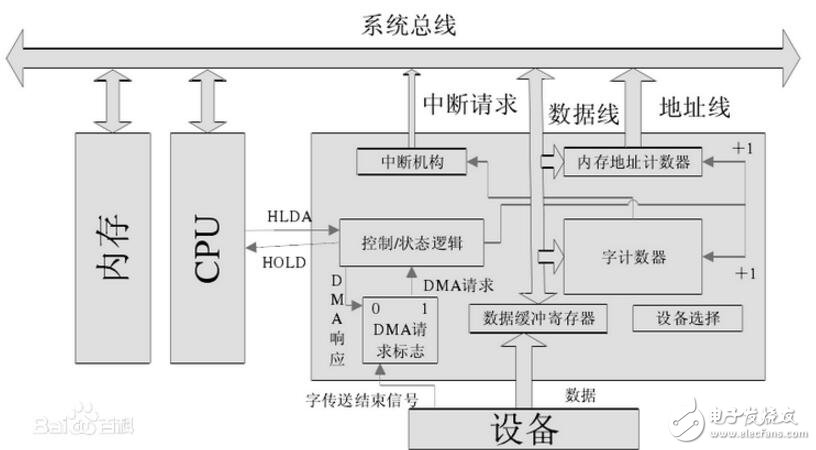

dma控制器組成:

一個DMA控制器,實際上是采用DMA方式的外圍設備與系統總線之間的接口電路,這個接口電路是在中斷接口的基礎上再加DMA機構組成。習慣上將DMA方式的接口電路稱為DMA控制器。

(1)內存地址計數器:用于存放內存中要交換的數據的地址。在 DMA傳送前,須通過程序將數據在內存中的起始位置(首地址)送到內存地址計數器。而當 DMA 傳送時,每交換一次數據,將地址計數器加“1”,從而以增量方式給出內存中要交換的一批數據的地址。

(2)字計數器:用于記錄傳送數據塊的長度(多少字數)。其內容也是在數據傳送之前由程序預置,交換的字數通常以補碼形式表示。在DMA傳送時,每傳送一個字,字計數器就加“1”。當計數器溢出即最高位產生進位時,表示這批數據傳送完畢,于是引起DMA控制器向CPU發出中斷信號。

(3)數據緩沖寄存器:用于暫存每次傳送的數據(一個字)。當輸入時,由設備(如磁盤)送往數據緩沖寄存器,再由緩沖寄存器通過數據總線送到內存。反之,輸出時,由內存通過數據總線送到數據緩沖寄存器,然后再送到設備。

(4)DMA請求”標志:每當設備準備好一個數據字后給出一個控制信號,使“DMA

請求”標志置“1”。該標志置位后向“控制/狀態”邏輯發出DMA請求,后者又向CPU發出總線使用權的請求(HOLD),CPU響應此請求后發回響應信號HLDA,“控制/狀態”邏輯接收此信號后發出DMA響應信號,使“DMA 請求”標志復位,為交換下一個字做好準備。

(5)控制/狀態”邏輯:由控制和時序電路以及狀態標志等組成,用于修改內存地址計數器和字計數器,指定傳送類型(輸入或輸出),并對“DMA請求”信號和CPU響應信號進行協調和同步。

(6)中斷機構:當字計數器溢出時,意味著一組數據交換完畢,由溢出信號觸發中斷機構,向CPU提出中斷報告。

DMA控制器接口函數

主要作用是配置DMA控制器并啟動相應傳輸

s3c2440中關于公共DMA控制器的函數提供有:

s3c2410_dma_config()

s3c2410_dma_ctrl()

s3c2410_dma_enqueue()

s3c2410_dma_devconfig()

s3c2410_dma_set_buffdone_fn()

s3c2410_dma_request()

s3c2410_dma_free()

一般使用的順序如下:

request =》set_buffdone_fn=》 devconfig =》 config =》 enqueue =》 ctrl =》 free

1、int s3c2410_dma_request(unsigned int channel, struct s3c2410_dma_client *client, void *dev)

2、static inline void s3c2410_dma_buffdone(struct s3c2410_dma_chan *chan, struct s3c2410_dma_buf *buf, enum s3c2410_dma_buffresult result)

設置相應的dma通道完成一次dma傳輸后的回調函數

3、int s3c2410_dma_devconfig(int channel, enum s3c2410_dmasrc source, unsigned long devaddr)

source: S3C2410_DMASRC_HW: source is hardware

S3C2410_DMASRC_MEM: source is memory

devaddr: physical addr of source

4、int s3c2410_dma_config(unsigned int channel, int xferunit)

根據xferunit設置通道的控制寄存器DCONx

xferunit為每次傳輸的數據大小:0:byte 1:half word 2:word

5、dma_alloc_coherent

DMA要求使用non-cached, 物理地址連續的內存。

將對應的內核虛擬地址轉化為物理地址,供給后面的s3c2410_dma_enqueue函數使用。

6、int s3c2410_dma_enqueue(unsigned int channel, void *id, dma_addr_t data, int size)

7、int s3c2410_dma_ctrl(unsigned int channel, enum s3c2410_chan_op op)

8、int s3c2410_dma_free(unsigned int channel, struct s3c2410_dma_client *client)

DMA控制器接口函數使用實例

s3c2440 DMA datasheet

s3c2440 DMA控制器支持4種情況的DMA傳輸:

a. source and destination are in the system bus

b. source in the system bus while destination in the peripheral bus

c. source in the peripheral bus while destination in the system bus

d. source and destination are in the peripheral bus

但是在arch/arm/plat-s3c24xx/dma.c的函數s3c2410_dma_devconfig中卻只實現了b和c兩種情況。

s3c2440有4個DMA channel,每個channel都有DISC/DISCC/DIDST/DIDSTC寄存器,DISC和DIST可以填入不同source類型(具體參考S3c2440 Datasheet Table 8-1),除此之外還能填入內存的物理地址作為source或destination。

和傳輸相關的3個參數:

TSZ:DCON[28],0:unit模式:一次transfer1個data size,burst模式:一次transfer4個data size

DSZ:DCON[21:20],0:data size is BYTE,1:data size is Half WORLD,0:data size is WORLD

TC:DCON[19:0],transfer count

傳輸的數據量=TC * (DSZ * 8) * TSZ

request source: DCON[23]

0:S/W request mode, DMA is triggered by setting SW_TRIG bit of DMASKTRIG control register

1:DMA source selected by bit[26:24] triggers the DMA operation

service mode:DCON[27]

0:single service mode,一次DMA請求完成一次原子操作,等待下一次請求

1:whole service mode,一次DMA請求完成一批原子操作,當TC=0表示完成一次whole service

電子發燒友App

電子發燒友App

評論