隨著微電子技術(shù)、通信技術(shù)、控制技術(shù)和半導(dǎo)體技術(shù)的飛速發(fā)展以及工業(yè)、醫(yī)療衛(wèi)生、國(guó)防等部門對(duì)智能控制要求的不斷提高,嵌入式微處理器被越來(lái)越廣泛地應(yīng)用。為了適應(yīng)各方面的需求,嵌入式微處理器在運(yùn)算速度、可擴(kuò)充能力、系統(tǒng)可靠性、功耗和集成度等方面得到了突飛猛進(jìn)的發(fā)展。嵌入式微處理器體系結(jié)構(gòu)經(jīng)歷了一個(gè)從CISC(Complex In-struction Set Computer)到RISC(Reduced Instruction SetComputer),從4位、8位、16位到32位甚至64位,尋址空間從64kB到16MB甚至更大,處理速度從0.1MIPS到2000 MIPS的過程。

ATmega161是一款基于AVR(Advanced RISC)的低功耗CMOS8位單片機(jī),它以其強(qiáng)大的功能和較高的性價(jià)比得到了不少嵌入式系統(tǒng)開發(fā)者的青睞。其主要特點(diǎn)表現(xiàn)在以下幾方面:

(1)ATmega161增強(qiáng)型RISC結(jié)構(gòu)方面

●內(nèi)含2周期乘法器;

●具有32個(gè)8位通用(工作)寄存器;

●工作在8MHz時(shí),具有8MIPS的性能;

●具有130條指令,大多數(shù)為單周期指令;

(2)數(shù)據(jù)和程序存儲(chǔ)器方面

●內(nèi)含16k非易失在系統(tǒng)可編程FLASH;

●具有1k的內(nèi)部SRAM;

●帶有512字節(jié)非易失在系統(tǒng)編程EEPROM;

●能進(jìn)行可編程程序加密。

(3)外圍特點(diǎn)

●帶有兩個(gè)可編程全雙工UART;

●帶有主/從SPI串行接口;

●具有自身振蕩器的實(shí)時(shí)時(shí)鐘RTC;

●具有2個(gè)8位定時(shí)器/計(jì)數(shù)器;

●帶有1個(gè)可預(yù)分頻的具有比較、捕捉和雙8/9/10位PWM功能的16位定時(shí)器/計(jì)數(shù)器;

●具有可編程的內(nèi)部看門狗定時(shí)器;

●片內(nèi)的模擬比較器可用作A/D轉(zhuǎn)換;

●帶有35個(gè)可編程I/O口。

(4)增強(qiáng)的MCU特點(diǎn)

●可進(jìn)行上電復(fù)位和可編程低壓檢測(cè);

●具有21級(jí)內(nèi)外部中斷源;

●有空閑、節(jié)電及掉電三種節(jié)電模式。

(5)其它特性

●采用40腳PDIP,44腳PLCC及QFP封裝;

●工作電壓為4.0~5.5V。

嵌入式測(cè)控網(wǎng)絡(luò)的設(shè)計(jì)

傳統(tǒng)的測(cè)控網(wǎng)絡(luò)由于連接有很多常規(guī)模擬儀表和執(zhí)行機(jī)構(gòu)以及其它現(xiàn)場(chǎng)設(shè)備而具有很多缺點(diǎn),如一對(duì)一結(jié)構(gòu)連線龐雜,工程周期長(zhǎng),安裝費(fèi)用高,維護(hù)不便;模擬信號(hào)傳輸精度低,易受干擾;操作員在控制室既不能對(duì)其進(jìn)行參數(shù)調(diào)整,也不能對(duì)其進(jìn)行故障診斷,因而會(huì)導(dǎo)致操作的“失控”。

所示是筆者設(shè)計(jì)的以ATmega161為核心的嵌入式測(cè)控網(wǎng)絡(luò)系統(tǒng)示意圖。圖中的嵌入式控制器通過兩級(jí)RS-485總線既可和上位機(jī)通信,又可和傳感器以及執(zhí)行機(jī)構(gòu)等現(xiàn)場(chǎng)設(shè)備進(jìn)行通信。操作人員可直接通過鍵盤、鼠標(biāo)來(lái)完成對(duì)執(zhí)行機(jī)構(gòu)的遠(yuǎn)程控制,從而實(shí)現(xiàn)實(shí)時(shí)監(jiān)控;同時(shí),總線似的數(shù)字信號(hào)通信可以克服常規(guī)模擬信號(hào)傳輸?shù)脑S多缺點(diǎn),并具有接線簡(jiǎn)單、維護(hù)方便、精度高、抗干擾能力強(qiáng)等優(yōu)點(diǎn)。

硬件設(shè)計(jì)

可以用兩個(gè)UART通用串行口組成兩級(jí)RS-485網(wǎng)。一般的微處理器并不具備兩個(gè)UART,通常可擴(kuò)展一片串行接口芯片(如8251、8250或者 EXAR公司的ST16C2552等)構(gòu)成兩個(gè)UART,但這樣會(huì)使電路變得復(fù)雜、PCB成本增大且系統(tǒng)的抗干擾能力下降。而ATmega161正好具有兩個(gè)可編程UART,所以無(wú)需擴(kuò)展,這種方法不但可以使電路簡(jiǎn)化并使PCB體積縮小,而且還可使抗干擾能力增強(qiáng),同時(shí)也具有較高的性價(jià)比。

通信部分的硬件原理圖如圖2所示。圖中,將兩個(gè)UART的RXD、TXD分別接到兩片MAX485上,以使其轉(zhuǎn)換成RS-485電平,再以數(shù)據(jù)總線的形式連接到上位機(jī)和數(shù)字化的儀器儀表以及其它現(xiàn)場(chǎng)設(shè)備上,從而構(gòu)成兩級(jí)測(cè)控網(wǎng)絡(luò)。

MAX485是一種專用的RS-485/RS-422接口芯片,它具有功耗低、體積小、操作簡(jiǎn)單方便等優(yōu)點(diǎn)。每片MAX485最多能帶32個(gè)收發(fā)器,如果要增加每條總線上收發(fā)器的個(gè)數(shù),可以換成MAX487、MAX1487(可帶128個(gè)收發(fā)器)等芯片。

軟件設(shè)計(jì)

4.1通信協(xié)議

通信協(xié)議采用ISO的OSI七層模型中的物理層、鏈路層和應(yīng)用層。其中物理層為RS-485,它以雙絞線為傳輸總線,其最大通信距離可達(dá)1200米,最大從機(jī)個(gè)數(shù)為32臺(tái)(使用MAX485),數(shù)據(jù)傳送速率為2400b/s,數(shù)據(jù)傳輸格式為:1位起始位、8位數(shù)據(jù)位和1位停止位,該格式無(wú)奇偶校驗(yàn)位,通信錯(cuò)誤檢測(cè)采用累加和校驗(yàn)。

數(shù)據(jù)鏈路層可參考ISO的“高級(jí)數(shù)據(jù)鏈路層協(xié)議”(HDLC)的有關(guān)規(guī)定,并選用適合于主從網(wǎng)絡(luò)的HDLC的正常響應(yīng)操作模式(NRM),即從站只有在其受到主站的請(qǐng)求時(shí)才能發(fā)送信息。上位機(jī)采用輪詢的方式對(duì)嵌入式控制器進(jìn)行訪問,而控制器又對(duì)數(shù)字化傳感器及現(xiàn)場(chǎng)設(shè)備以輪詢的方式進(jìn)行訪問。其操作過程如圖3所示。

嵌入式控制器在整個(gè)通信過程中具有雙重身份,即在與上位機(jī)通信過程中,上位機(jī)是主站,控制器為從站;而在與傳感器及現(xiàn)場(chǎng)設(shè)備的通信過程中,控制器是主站,傳感器和現(xiàn)場(chǎng)設(shè)備為從站。

幀的格式定義為:幀開始符、源地址、目的地址、控制字、信息、累加和校驗(yàn)(BCC)以及幀結(jié)束符。

在實(shí)際的通信過程中,往往會(huì)出現(xiàn)數(shù)據(jù)丟失和數(shù)據(jù)傳輸錯(cuò)誤等通信故障。為了防止數(shù)據(jù)丟失,系統(tǒng)采用了超時(shí)處理的方法。這樣,主站發(fā)送查詢命令后,如果在預(yù)定的時(shí)間內(nèi)沒有收到從站的響應(yīng)信號(hào),可再次發(fā)送一幀查詢命令,以等待對(duì)方響應(yīng)。如果連續(xù)三次發(fā)送后,主站仍然沒有收到正確的響應(yīng),系統(tǒng)將退出并報(bào)警,同時(shí)開始輪詢下一從站。

針對(duì)數(shù)據(jù)出錯(cuò)情況,每幀都增加了累加和校驗(yàn)來(lái)對(duì)源地址、目的地址、控制字和信息段進(jìn)行邏輯和運(yùn)算,并將運(yùn)算結(jié)果作為幀結(jié)束前的一個(gè)字符傳送到接收方,而接收方在接收完該幀信息后也將接收到的源地址、目的地址、控制字和信息段作邏輯和運(yùn)算,如果運(yùn)算結(jié)果和收到的運(yùn)算結(jié)果不一致,則廢棄該幀數(shù)據(jù)。如果接收到通信協(xié)議規(guī)定之外的控制字、源地址或目的地址,系統(tǒng)也將廢棄該幀數(shù)據(jù)。

4.2 ATmega161的雙UART寄存器設(shè)置

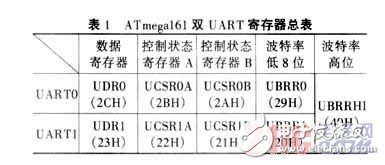

如前所述,ATmega161帶有兩個(gè)全雙工的可編程通用異步收發(fā)器UART。用戶可通過設(shè)置表1中的9個(gè)寄存器來(lái)對(duì)兩個(gè)UART進(jìn)行編程,表內(nèi)括號(hào)中的十六進(jìn)制數(shù)為相應(yīng)的寄存器地址。

以UART0為例,UDR0是兩個(gè)物理分離的數(shù)據(jù)寄存器,它們具有相同的I/O地址,但在讀/寫時(shí),它們將分別訪問不同的寄存器。在兩個(gè)狀態(tài)控制寄存器中,UCSR0A的格式為:

其中,RXC0為接收完成標(biāo)志,TXC0為發(fā)送完成標(biāo)志,UDRE0為數(shù)據(jù)寄存器空標(biāo)志,F(xiàn)E0為幀出錯(cuò)標(biāo)志,OR0為超越出錯(cuò)標(biāo)志,U2X0為雙倍傳輸速度標(biāo)志,MPCM0為多處理器通信標(biāo)志位。另一個(gè)狀態(tài)控制寄存器UCSR0B的格式為:

該格式中的RXCIE0為接收完成中斷觸發(fā)位,TXCIE0為發(fā)送中斷觸發(fā)位,UDRIE0為數(shù)據(jù)寄存器空中斷觸發(fā)位,RXEN0為接收允許,TXEN0為發(fā)送允許,CHR90為九位數(shù)據(jù)標(biāo)志位,RXB80為收到的數(shù)據(jù)第8位,TXB80為發(fā)送的數(shù)據(jù)第8位。

UBRRHI的低四位和UBRR0分別為波特率寄存器的高位和低位。波特率寄存器的計(jì)算公式為:

式中,F(xiàn)ck為晶振頻率,BAUD為波特率,UBRR為寄存器中應(yīng)取的值。

UART1的設(shè)置編程與UARTO基本相同。

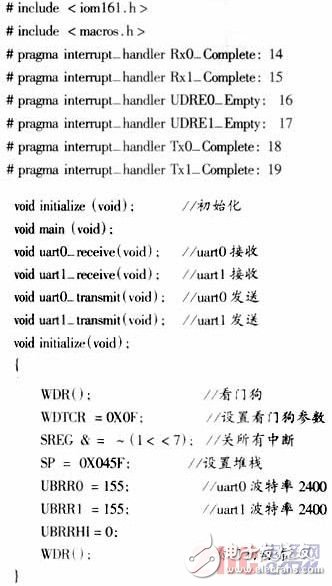

4.3部分源代碼

可以使用匯編語(yǔ)言或ANSIC語(yǔ)言編寫源代碼(編譯軟件均可從INTERNET上免費(fèi)下載),編譯生成HEX目標(biāo)文件后,可以通過高速下載線經(jīng)由SPI接口將該目標(biāo)文件下載到ATmega161的FLASH存儲(chǔ)器中。

下面是C語(yǔ)言源代碼的一部分:

結(jié)束語(yǔ)

事實(shí)證明,用ATmega161構(gòu)成的嵌入式控制器在構(gòu)成兩級(jí)測(cè)控網(wǎng)絡(luò)時(shí)具有明顯的性價(jià)比優(yōu)勢(shì),在現(xiàn)場(chǎng)總線(如LONWORKS、CAN等)仍然還比較昂貴的情況下,可以作為DCS向FCS的過渡產(chǎn)品。因?yàn)樵摼W(wǎng)絡(luò)具有數(shù)字化的特點(diǎn),加上RS-485標(biāo)準(zhǔn)在國(guó)內(nèi)已經(jīng)非常流行,所以具有良好的擴(kuò)展性和通用性,完全可以滿足現(xiàn)場(chǎng)控制和遠(yuǎn)程監(jiān)控的要求,可廣泛應(yīng)用于各類測(cè)控系統(tǒng)中。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論