由于市場對MCU功能的要求總是不斷變化和升級,MCU應用的領域也不斷擴展,因此往往需要對最初的設計進行修改。Flash MCU與以往OTP/MASK MCU相比,最大的優點就在于可進行高達上萬次的擦寫操作,順應了MCU功能不斷修改的需求;另一方面,Flash MCU市場價格也在不斷下降。實際上,Flash MCU工作時Flash的延時、讀寫時充等特性是非常,程序存儲在MCU外部仿真板上的SRAM中,由額外的硬件邏輯來模擬Flash的這些特性是費時低效的;同時將Flash和MCU內嵌的其他類型存儲器如SRAM、ROM等區分開來也是十分重要的。如果在程序的調試階段就可以反映出這特性,有且于實現程序從仿真器到商用MCU芯片的無縫轉移。

1 關于Flash MCU

Flash MCU的構成如圖1所示,主要由CPU核、Flash IP及其控制模塊、SRAM IP及基控制模塊、WatchDog、PMU(Power Manage Unit,功耗管理單元)、I/O端口以及ISP在線編程接口等組成。不同功能的Flash MCU還包含一些各自獨特的應用模塊單元,如用于尋呼的Flash MCU所包含的解碼模塊。對于用來構成在線仿真器的Flash MCU還可能包括仿真接口單元。本文在討論Flash MCU的在線仿真時,指的都是包含仿真接口的Flash MCU。

Flash存儲器幾乎擁有現今追求個性化的用戶所需要的所有優點:掉電數據不丟失、快速的數據存取時間、電可擦除、容量大、在線(系統)可編程、價格低廉以及足夠多的擦寫次數的高可靠性等,已成為新一代嵌入式應用的首選存儲器。與Flash MCU相比,MASK(掩膜)MCU盡管在大指生產時仍具備一定價格優勢,但其升級不便的缺點,隨著今后Flash成本的進步降低和MCU功能需求的逐漸增多,將表現得更為顯著。

2 基于外部SRAM的MCU在線仿真器

SRAM不需要刷新電路即能保存它內部存儲的數據。而DRAM(Dynamic Random Access Memory)每隔一段時間,要刷新充電一次,否則內部的數據即會消失,因此SRAM具有較高的性能,但是SRAM也有它的缺點,即它的集成度較低,相同容量的DRAM內存可以設計為較小的體積,但是SRAM卻需要很大的體積,且功耗較大。所以在主板上SRAM存儲器要占用一部分面積。

一種是置于CPU與主存間的高速緩存,它有兩種規格:一種是固定在主板上的高速緩存(Cache Memory );另一種是插在卡槽上的COAST(Cache ON A Stick)擴充用的高速緩存,另外在CMOS芯片1468l8的電路里,它的內部也有較小容量的128字節SRAM,存儲我們所設置的配置數據。還有為了加速CPU內部數據的傳送,自80486CPU起,在CPU的內部也設計有高速緩存,故在Pentium CPU就有所謂的L1 Cache(一級高速緩存)和L2Cache(二級高速緩存)的名詞,一般L1 Cache是內建在CPU的內部,L2 Cache是設計在CPU的外部,但是Pentium Pro把L1和L2 Cache同時設計在CPU的內部,故Pentium Pro的體積較大。Pentium II又把L2 Cache移至CPU內核之外的黑盒子里。

MCU仿真器的一種常見做法是,將用戶的待調試程序(以下簡稱用戶程序)存儲在MCU外部仿真板的SRAM(以下簡稱外部SRAM)中,在bond-out MCU的外部結構仿真監控硬件(以下簡稱外部仿真邏輯),當用戶程序在仿真器中調試完成后,編程到商用MCU芯片中,應用到用戶系統。在商用MCU中,這些仿真接口信號不會出現在芯片封裝的管腳上。

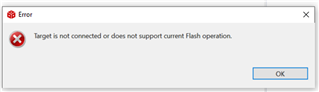

在Flash MCU沒有被廣泛應用之前,仿真器設計公司通常將用戶程序和監控程序都存儲在外部SRAM中,這種做法基本上可以反映SRAM MCU真實的運行情況,對用戶程序的調度效果影響不大。但是對于Flash MCU而言,則存在一定的問題。畢競SRAM和Flash在工藝和讀寫時序上相去甚遠,CPU運行存儲在SRAM和Flash中的程序,情況是完全不同的。有可能出現程序存儲的仿真器的外部SRAM中運行良好,但是編程到商用MCU中工作起來卻不正常。隨著Flash MCU在 MCU市場中的比重越來越大,這一問題顯得越來越突出,有必要加以重視。

本文介紹的Flash MCU仿真器的設計方法,幾乎不增加MCU的仿真接口信號和芯片設計的復雜程度,就可以接近程序在商用MCU中的運行情況,實現用戶程序從仿真器到商用MCU的良好轉移。

3 基于MCU內部Flash的在線仿真器的一種設計方法

圖2是Flash MCU仿真器系統構成示意圖,其中的虛線接口信號是MCU的仿真接口,通常包括仿真使能信號,bond-out MCU中的CPU的地址、數據、讀/寫和取指等信號,以及少數幾個用于仿真的控制信號。仿真接口是Flash MCU與外部仿真邏輯之間的橋梁,使得外部仿真邏輯能夠監控MCU的內部狀態。

3.1 仿真器的工作原理

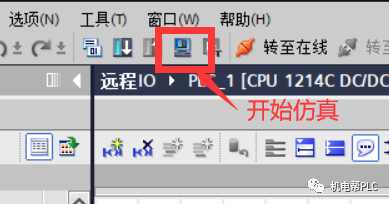

仿真器內部的P口等硬件資源和51系列單片機基本是完全兼容的。仿真主控程序被存儲在仿真器芯片特殊的指定空間內,有一段特殊的地址段用來存儲仿真主控程序,仿真主控程序就象一臺電腦的操作系統一樣控制仿真器的正確運轉。仿真器和電腦上的上位機軟件(即KEIL)是通過串口相連的,通過仿真器芯片的RXD和TXD負責接收電腦主機發來的控制數據,TXD負責給電腦主機發送反饋信息。控制指令由KEIL發出,由仿真器內部的仿真主控程序負責執行接收到的數據,并且進行正確的處理。進而驅動相應的硬件工作,這其中也包括把接收到的BIN或者其它格式的程序存放到仿真器芯片內部用來存儲可執行程序的存儲單元(這個過程和把程序燒寫到51芯片里面是類似的,只是仿真器的擦寫是以覆蓋形式來做的),這樣就實現了類似編程器反復燒寫來試驗的功能!不同的是通過仿真主控程序可以做到讓這些目標程序做特定的運行,比如單步、指定斷點、指定地址等,并且通過KEIL可時時觀察到單片機內部各個存儲單元的狀態。仿真器和電腦主機聯機后就象是兩個精密的齒輪相互咬合的關系,一量強行中斷這種聯系(比如強行給仿真器手動復位或都撥支聯機線等),電腦就會提示聯機出現問題,這也體現了硬件仿真的特性,即“所見即所得”。這些都是編程器無法做到的。這些給調試、修改、以及生成最終程序創造了比較有力的保證,從而實現較高的效率。

仿真器工作時,CPU的取指空間需要在內外存儲器之間反復切換。CPU地址空間劃分示意圖如圖3所示。總體上,仿真器的工作受圖4所示的狀態機控制。該狀態機共有四個狀態:

?用戶程序運行態(簡稱用戶態)

仿真器復位后,處在運行用戶程序的狀態。在該狀態下,CPU運行存儲在內部Flash中的用戶程序;外部仿真邏輯實時監測仿真接口,等待程序中斷事件的發生,進入下一狀態-跳轉態。

用戶程序通過MCU的ISP(在線編程接口)編程到內部Flash中,由Flash MCU的專用編程器完成。在設計bond-out MCU時,應該考慮與非bond-out MCU在編程時管腳的一致性。

外部SRAM用來存儲監控程序和監時數據。

?跳轉態

一旦程序中斷事件發生,需要切換CPU的取指空間,跳轉到監控程序窗口。

由于在程序中何處中斷是不可預知的,因此不可能在用戶程序中預先安插好用于空間切換的跳轉指令。所以需要一個專門的狀態來插入跳轉指令碼和跳轉的目的地址,即監控程序的入口地址,強制CPU運行監控程序。監控程序窗口是劃分CPU地址空間時,為仿真功能預留的地址空間,空間大小視所需的監控程序的大小而定,監控程序的大小在一定程序上取決于仿真功能的強弱。

CPU從仿真接口讀跳轉指令碼和跳轉地址。MCU外部仿真邏輯同時使能程序空間切換信號,屏蔽MCU的所外部中斷,停止MCU中CPU外圍模塊的時鐘,也就相當于屏蔽了MCU的所有內部中斷。當程序空間的切換完成后,仿真器進入監控態,運行存儲在外部SRAM中的監程序。

?監控態

在監控狀態下,CPU運行存儲在外部SRAM中的監控程序;繼續禁止MCU的所有外部中斷,停止MCU中CPU外圍硬件模塊的時鐘。

監控程序的任務是獲取MCU當前的狀態,接受軟件的調試命令,控制MCU的下一步運行。監控程序可以寫得很簡單,僅僅獲取CPU特殊寄存器和外圍硬件寄存器的值,實現監視功能。如MOTOROLA的HC6808就可以通過在監控程序開始處加入以下程序段得到這些寄存器的值。對于CPU指令集不支持讀取全部特殊寄存器的MCU,可以通過在MCU內部增加測試邏輯得到。PC值即為程序中斷處CPU的取指地址。

PSHA ;將ACC的值壓入堆棧

TPA ;將CCR的值傳送給ACC

STA $2FEB ;將CCR的值存入存儲器,地址為$2FEB

PULA ;將ACC彈出堆棧

STA $2FEA ;將ACC有值存入存儲器,地址為$2FEA

STHX $5F ;將IDX(H:X)的值存入存儲器,地址為$005F

TSX ;將SP的值傳送給IDX(H:X)

STHX $5D ;將SP的值存放存儲器,地址為$005D

當不再繼續調試,給出開始運行的命令,監控程序結束對運行命令的等待,并且將CPU特殊寄存器的值恢復。繼續運行監控程序,直到最后一條指令即跳轉指令進行返回態。

?返回態

CPU執行監控程序的最后一條指令-跳轉指令。外部仿真邏輯在指令碼后緊接著插入本次中斷事件的中斷點地址(進入監控程序之前的用戶程序指令地址),CPU的取指空間需要跳回到用戶程序空間。取消對外部中斷的屏蔽,恢復CPU外圍模塊的工作時鐘,監控程序完成使命,回到用戶態,繼續運行內部Flash中的用戶程序。

3.2 內部仿真邏輯

為了構造合適的MCU的仿真接口,必須在MCU設計時,在MCU內部增加一個仿真接口模塊,稱為內部仿真接口模塊。負責對仿真接口所需的CPU端口信號進行處理(如出于減少bond-out信號線的考慮,將地址和數據總線復用),并產生外部仿真邏輯所需的控制信號如地址鎖存信號,接收來自外部仿真邏輯的控制信號如程序文憑間切換使能信號等。

3.3 外部仿真邏輯

外部仿真邏輯如圖2左部所示,負責接收計算機通過并口發送的仿真命令,監視MCU的仿真接口,控制仿真器的工作狀態。外部仿真邏輯由外部仿真接口模塊、斷點判斷模塊、軌跡紀錄模塊、并口接口模塊和外部SRAM讀寫控制模塊等部分組成。各個模塊的作用簡單介紹如下:

?外部仿真接口模塊

該模塊是外部仿真邏輯中仿真狀態機所在的核心模塊。功能包括:接收業自MCU的地址、數據、讀/寫、取指、地址鎖存等信號;根據并口接口模塊給出的來自軟件的仿真命令,并接收來自斷點判斷模塊的斷點標志信號;產生送給MCU的程序空間切換使能信號;運行監控程序時,給出讀寫外部SRAM所需信號,并接收讀出的數據,將其送給MCU。

?斷點判斷模塊

根據外部仿真接口模塊送來的CPU地址,讀取斷點標志存儲器中的相應值。如果讀出的標志為有效值,表示當前地址為斷地址。接收來自并口接口模塊的設置和清除斷點命令,將斷點存儲器的相應位置1或置0。允許設置任意數目的硬件斷點。

?軌跡紀錄模塊

將外部仿真接口模塊送來的CPU取指地址,存儲在軌跡紀錄的存儲器中。軌跡紀錄的存儲器采用的FIFO的方式,所能紀錄的軌跡長度是有限的,存滿刷新。軟件讀取該存儲器,可以得到CPU的運行軌跡。

?并口接口模塊

并口接口(并行接口),簡稱并口,也就是LPT接口,是采用并行通信協議的擴展接口。并口的數據傳輸率比串口快8倍,標準并口的數據傳輸率為1Mbps。并口采用的是25針D形接頭。所謂“并行”,是指8位數據同時通過并行線進行傳送,這樣數據傳送速度大大提高,但并行傳送的線路長度受到限制,因為長度增加,干擾就會增加,數據也就容易出錯。目前,并行接口主要作為打印機端口等。

提供仿真器和計算機并口之間的通信接口,可以針對不同的并口模式設計,以滿足不同模式的通信時序要求。

?外部SRAM讀寫控制模塊

仿真過程中,仿真器的不同部分需要分時讀寫外部SRAM,包括:并口接口模塊下裝程序到外部SRAM;MCU在監控態從外部SRAM中讀取程序指令,存儲臨時數據等。

對于Flash MCU而言,這種將用戶的待調試程序存儲在MCU內部的Flash中,將監控程序存儲在MCU外部的SRAM中,并在MCU外部構造仿真邏輯,通過對采用bond-out技術的MCU的bond-out管腳進行監控,來實現在線仿真的做法,在芯片設計時不需要做太多的工作,而且可以反映程序真實的運行效果。而相對于用硬件平臺如FPGA仿真,則價格低廉許多,是一種種權衡折衷的方法。作者提取了一個簡單的Flash MCU模型,用這種方法完成了仿真器的邏輯設計,用Synopsys DC綜合,用Quartus布線Altera APEX 20K200 FPGA中,用ModelSim5.4進行了后仿真,完成了仿真驗證。結果證明這樣的做法是可行的。

電子發燒友App

電子發燒友App

評論