1.引言

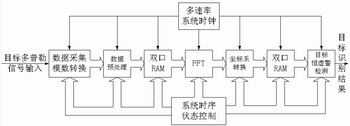

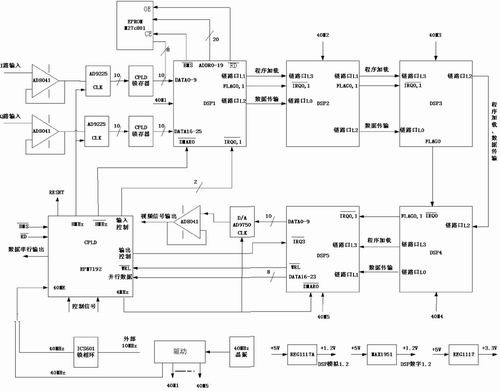

本文針對紅外圖像處理系統的實時性要求,提出了基于DSP+FPGA+ASIC的圖像處理架構。

隨著紅外焦

2010-07-22 15:18:50 796

796 什么是DSP圖像處理系統?DSP圖像處理系統中信號完整性的問題是什么?有哪些解決方案?

2021-06-01 06:40:35

FPGA在高性能數字信號處理領域越來越受關注,如無線基站。在這些應用中, FPGAs通常被用來和DSP處理器并行工作。有更多的選擇當然是好的,但這也意味著系統設計師需要一個確切的FPGAs及高端DSP信號處理器性能參數圖。不幸的是,常用的參數圖在這種情況下都是不可靠的。

2019-09-25 08:17:27

FPGA在高性能數字信號處理領域越來越受關注,如無線基站。在這些應用中, FPGAs通常被用來和DSP處理器并行工作。有更多的選擇當然是好的,但這也意味著系統設計師需要一個確切的FPGAs及高端DSP信號處理器性能參數圖。不幸的是,常用的參數圖在這種情況下都是不可靠的。

2019-08-23 06:40:44

FPGA和DSP明幫暗戰,爭奪20億美元高性能信號處理市場

2012-08-20 10:51:16

來說,濾除噪聲、擴展對比度、銳化以及色彩增強等處理能顯著提升視覺效果。這里設計一個基于FPGA的實時視頻圖像處理系統,包含增強對比度擴展和色飽和度兩種處理方法,相比于DSP和ASIC方案來說,FPGA在性能和靈活性方面具有絕對優勢,應用FPGA設計視頻通信系統更普遍。

2019-08-22 08:22:29

低功耗、高性能便攜式DSP應用的簡明方法。實際上,目前的便攜式系統設計人員可以采用自動化的設計工具來完成系統設計和FPGA實施。采用與系統框圖類似的圖形化方法,軟件可自動將模塊轉換成相應的FPGA

2011-02-17 11:21:37

FPGA內部實現一個完整系統功能。本文采用Altera公司提供的SoPC Builder工具將Nios II CPU軟核嵌入到Cyclone II系列FPGA內部以控制高性能DDS器件AD9858,并采用

2020-11-24 06:39:52

近年來變頻控制因其節能、靜音及低顫動而得到廣泛的關注和應用,基于ARM/DSP 的高性能驅動方案為中大功率三相電機提供了高性能、多控制方式的解決方案,其主要應用于對電機控制的性能、實時性方面要求比較

2019-07-09 08:24:02

Express總線架構的高性能信號處理平臺,該平臺采用一片TI的DSP(TMS320C6455)處理器與一片Altera的FPGA(EP4CGX150)處理器,DSP最高支持1.2G主頻,與FPGA協同工作能提供

2016-03-03 11:01:37

Express總線架構的高性能信號處理平臺,該平臺采用一片TI的DSP(TMS320C6455)處理器與一片Altera的FPGA(EP4CGX150)處理器,DSP最高支持1.2G主頻,與FPGA協同工作能提供

2016-03-10 15:00:34

Express總線架構的高性能信號處理平臺,該平臺采用一片TI的DSP(TMS320C6455)處理器與一片Altera的FPGA(EP4CGX150)處理器,DSP最高支持1.2G主頻,與FPGA協同工作能提供

2016-03-17 13:46:08

Express總線架構的高性能信號處理平臺,該平臺采用一片TI的DSP(TMS320C6455)處理器與一片Altera的FPGA(EP4CGX150)處理器,DSP最高支持1.2G主頻,與FPGA協同工作能提供

2016-03-24 10:57:33

Express總線架構的高性能信號處理平臺,該平臺采用一片TI的DSP(TMS320C6455)處理器與一片Altera的FPGA(EP4CGX150)處理器,DSP最高支持1.2G主頻,與FPGA協同工作能提供

2016-03-31 11:08:53

Express總線架構的高性能信號處理平臺,該平臺采用一片TI的DSP(TMS320C6455)處理器與一片Altera的FPGA(EP4CGX150)處理器,DSP最高支持1.2G主頻,與FPGA協同工作能提供

2016-04-08 11:03:55

Express總線架構的高性能信號處理平臺,該平臺采用一片TI的DSP(TMS320C6455)處理器與一片Altera的FPGA(EP4CGX150)處理器,DSP最高支持1.2G主頻,與FPGA協同工作能提供

2016-04-15 13:20:57

Express總線架構的高性能信號處理平臺,該平臺采用一片TI的DSP(TMS320C6455)處理器與一片Altera的FPGA(EP4CGX150)處理器,DSP最高支持1.2G主頻,與FPGA協同工作能提供

2016-04-26 10:58:59

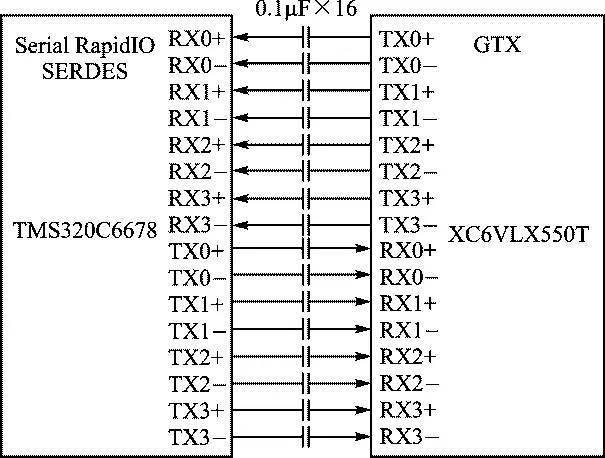

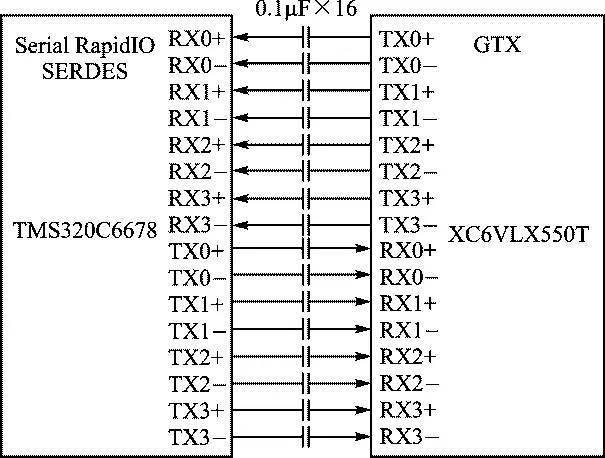

架構的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-03-02 13:52:47

架構的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-03-09 10:12:15

架構的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-03-16 11:00:00

架構的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-03-30 11:12:53

架構的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-04-07 10:40:35

架構的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-04-14 11:09:20

架構的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-04-25 11:21:12

架構的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA XC7K325T

2016-03-23 11:03:18

當前信號處理領域內陣列信號處理技術正在迅速發展,各種新的算法及新的處理技術不斷出現,要求信號處理系統具有快速適應各種新算法和新技術的能力,采用傳統的基于專用硬件的設計方法所開發出來的信號處理系統無法

2016-05-31 17:53:59

本系統采用基于FPGA與DSP協同工作進行視頻處理的方案,實現視頻采集、處理到傳輸的整個過程。實時視頻圖像處理中,低層的預處理算法處理的數據量大,對處理速度要求高,但算法相對比較簡單,適合于用

2019-07-01 07:38:06

對數據采集與處理系統提出了新的更高的要求,即高速度、高精度和高實時性。對數據采集與處理系統的設計,有以下3種方案可供選擇:(1)A/D+DSP方案在傳統的高速信號處理中,大多采用這種方案。將A/D、D

2019-07-05 06:41:27

在實際的外場試飛過程中是不可能實現的,這也是雷達信號模擬器對場外試飛的一大優勢。FPGA作為高性能數字信號處理系統中的關鍵部件,在雷達信號模擬和雷達信號采集等方面有著巨大的開發潛能,采用這些技術對雷達

2019-07-10 07:30:35

是人們在應用該芯片時必須解決的關鍵問題。本文提出了一種簡單易行的測試方法,并在基于ADSP21062的雷達信號處理系統調試中獲得了成功,驗證了該方法的可行性。

2019-07-19 08:16:35

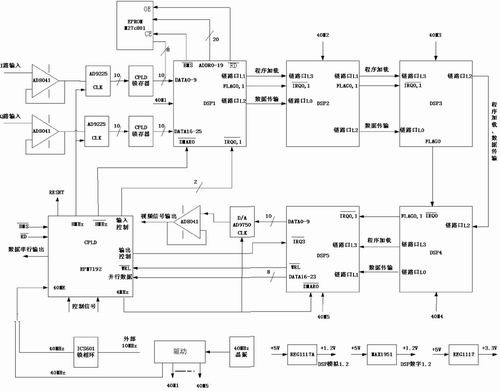

為解決高速數字圖像處理系統和實時性相沖突的要求,設計了以多DSP(數字信號處理器TMS320C6416)和現場可編程門陣列(FPGA)相結合的實時圖像處理系統。重點介紹了該系統的硬件資源選擇、基本組

2021-04-28 06:14:48

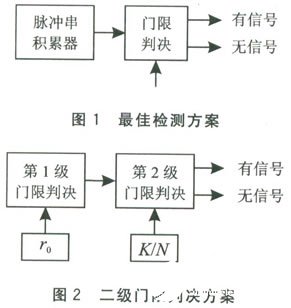

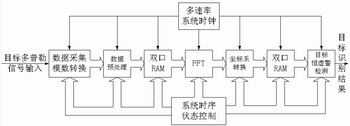

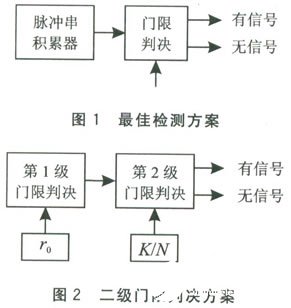

引信的核心部件,是方位識別功能和目標檢測功能的主要實現單元。其結構和性能對引信的整體性能有著至關重要的影響。隨著FPGA、DSP技術的發展,數字信號處理技術在引信中的應用大幅增強了引信信號的處理能力

2020-04-20 07:24:20

在實際的外場試飛過程中是不可能實現的,這也是雷達信號模擬器對場外試飛的一大優勢。FPGA作為高性能數字信號處理系統中的關鍵部件,在雷達信號模擬和雷達信號采集等方面有著巨大的開發潛能,采用這些技術對雷達

2019-07-15 06:48:33

利用DSP和FPGA芯片對采樣后的信號幅度和輪廓進行判定,以實現低信噪比條件下雷達信號的識別,從而還原出有效信號。系統原理框圖如圖1所示。2 系統的硬件設計2.1 高速A/D設計 大部分雷達信號為射頻

2018-08-15 09:43:14

管理。這樣充分利用DSP對數字信號高速處理的優勢,提高信號處理系統的實時性和穩定性。本文以TMS320VC5402 DSP為例,給予說明。1 系統的硬件設計1.1 PCI接口芯片

2018-12-17 11:29:06

和可編程邏輯器件XC2S300E為核心的圖象處理系統的硬件實現方案以及通過DSP對FPGA芯片的動態配置來實現軟件控制的設計思路。 關鍵詞:可編程邏輯器件;數宇信號處理器;數字圖象處理;動態配置dsp 可編程邏輯器件 數宇信號處理器 數字圖象處理 動態配置

2012-12-19 11:05:08

基于DSP的通用語音信號處理系統的設計

2020-05-28 09:15:53

。 整個系統以FPGA作為核心控制單元并完成視頻信號的中值濾波工作;以DSP作為整個系統的核心處理單元對采集的視頻圖像信息進行JPEG壓縮;在視頻傳輸單元設計了以PDIUSBD12芯片為基礎的USB總線,負責視頻信號的傳輸。

2019-06-28 08:10:26

三維圖像信息處理一直是圖像視頻處理領域的熱點和難點,目前國內外成熟的三維信息處理系統不多,已有的系統主要依賴高性能通用PC完成圖像采集、預處理、重建、構型等囊括底層和高層的處理工作。三維圖像處理

2019-06-24 06:11:03

圖像數據處理的工作原理是什么?基于FPGA+DSP的圖像處理系統待如何去設計?

2021-06-02 06:54:28

。 整個系統以FPGA作為核心控制單元并完成視頻信號的中值濾波工作;以DSP作為整個系統的核心處理單元對采集的視頻圖像信息進行JPEG壓縮;在視頻傳輸單元設計了以PDIUSBD12芯片為基礎的USB總線,負責視頻信號的傳輸。

2019-06-19 06:12:05

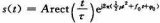

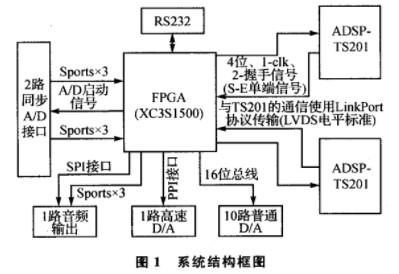

基于FPGA和DSP的光纖傳感信號實時處理系統。2. 系統組成與硬件流程圖圖1 系統結構框圖2.1 A/D前端處理電路及A/D采樣模塊探測器對光纖輸入的光脈沖序列進行光電轉換,通過濾波器實現波分解復用,再對信號

2021-07-05 11:23:33

本文介紹了一種雷達模目信號產生方法,該方法能夠通過FPGA和DSP實時產生具有多普勒頻移的多波束雷達目標回波,其意義在于可以為雷達信號處理分系統單獨調試提供數據來源,從而不必等待天線陣面的真實數據,這樣可以加快科研進度,也方便整機聯試時查找問題。

2011-07-13 09:09:26

要求,因此,需采用專用的數字信號處理器(DSP)來進行高速運算。盡管當前的數字信號處理器已達到較高水平, 但單片DSP芯片的處理能力還是不能滿足寬帶雷達的性能要求,需要引入并行處理技術,在本設計中使用4片

2019-05-21 05:00:19

模數轉換、FFT快速、準確的要求,并且具有高度集成、高可靠性和可編程等特點,減少了系統硬件開發周期,所以選用基于FPGA來實現雷達信號處理系統的設計。回映電子是一家基于Edge-AI技術的個護健康

2021-12-27 17:08:50

基于C55x DSP核芯片實現基帶信號處理系統的設計

2020-12-21 06:19:01

FPGA在高性能數字信號處理領域越來越受關注,如無線基站。在這些應用中, FPGAs通常被用來和DSP處理器并行工作。有更多的選擇當然是好的,但這也意味著系統設計師需要一個確切的FPGAs及高端DSP信號處理器性能參數圖。不幸的是,常用的參數圖在這種情況下都是不可靠的。

2019-10-12 06:40:30

本文設計了一套基于DSP的陣列聲波信號采集與處理系統,此系統將作為正在研制的陣列聲波測井儀中的一部分,應用于油田勘探中。

2021-05-31 06:26:35

問:1.我要設計生物圖像處理系統,選用那種型號較好(高性能和低價格)?2.如果選定 TI DSP,需要什么開發工具?

2019-09-20 03:18:05

雷達數據處理系統是現代雷達的重要組成部分,實際應用中,一般采用微型計算機實現雷達數據處理功能.隨著DSP芯片的快速發展,應用了DSP芯片的雷達數據處理系統極大地提高雷達數據

2009-04-23 17:15:35 26

26 雷達數據處理系統是現代雷達的重要組成部分,實際應用中,一般采用微型計算機實現雷達數據處理功能.隨著DSP芯片的快速發展,應用了DSP芯片的雷達數據處理系統極大地提高雷達數據

2009-04-24 15:35:33 17

17 設計了一種基于FPGA 和DSP 的光纖信號實時處理系統,介紹了系統的硬件組成和工作原理。該系統采用FPGA 實現數據的高速采集和邏輯控制,用DSP 實現傳感信號的全數字解調,分析了載

2009-06-19 11:17:43 24

24 設計了一種基于DSP 和FPGA 的雷達信號分選電路,對密集的雷達信號進行分選識別。系統利用FPGA 采集信號的特征參數以及對參數進行預處理;采用了累積差值直方圖算法,根據信號脈

2009-07-16 10:52:25 26

26 本文介紹一種基于FPGA 和DSP 的高性能PCI 數據采集處理卡的電路原理設計和PCI接口軟件設計。該數據采集處理卡主要采用TI 公司的TMS320C6416 數字信號處理器和XILINX公司VIRTEX2 系列的

2009-08-24 10:55:32 34

34 基于DSP和DSP/BIOS的實時雷達信號采集與處理系統:介紹了一種在實時操作系統DSP和DSP/BIOS 平臺下的雷達信號實時采集" 處理與傳輸系統的設計和實現! 利用Tms320c6416DSP強大的數據處理

2010-01-16 16:59:46 25

25 摘 要: 本文在闡述某種近距雷達目標檢測原理和FPGA技術發展狀況的基礎上,著重討論用FPGA設計高性能的數字信號處理系統的方法,并給出一個應用實例。

2006-03-11 13:16:43 1698

1698

摘 要:本文是基于ADSP-TS101S的多芯片數字信號處理系統的實現方案。該系統應用于某雷達的信號處理機。文中首先介紹了多片TigerSHARC DSP芯片構成的信號處理系統組成;其次估計系統的運算量,所需計算時間;最后具體說明了CPLD產生復位信號及并-串轉換功能實現的方法。

2006-03-11 13:17:45 856

856

FPGA構建高性能DSP

在數據通信和圖像處理這樣的應用中,需要強大的處理能力。當最快的數字信號處理器(DSP)仍無法達到速度要求時,唯一的選擇是

2009-12-08 14:20:38 2143

2143

基于雙DSP的實時圖像處理系統

介紹了基于雙DSP的實時圖像處理系統。該系統通過兩片TMS320C6201作為系統計算中心,通過可重構成的FPGA計算系統獲得系

2009-12-08 14:25:35 1009

1009

1 引言在大型的通信信號處理系統和雷達信號處理系統中,隨著器件的規模不斷擴大,對電源的性能和功率及其外圍濾

2010-12-13 17:22:11 1311

1311

本文介紹了一種模目信號設計方法,利用FPGA產生時序及控制,DSP實時計算所需要的回波,從而實現對雷達目標回波的模擬,這樣可以在沒有陣面數據的情況下,使信號處理分系統調試能

2011-07-05 09:46:27 1109

1109

在雷達系統的 數字信號處理 中,其主要特點是數據流量大、運算量大和處理的實時性,單片高性能的DSP芯片也不能滿足處理要求,必須采用多DSP板作為數字信號處理平臺。 開發復雜的

2011-08-26 14:38:39 42

42 在以DSP為核心的視頻處理系統中,視頻采集的方法通常可以分為兩大類:自動的視頻采集和基于DSP的視頻采集。前者通常采用CPLD/FPGA控制視頻解碼芯片,通過FIFO或者雙口RAM向DSP傳送數據

2011-09-14 17:05:31 2302

2302

文中提出一種通用信號處理系統,該系統不僅將兩種處理器的優點集于一身,并且具有很強的通用性,可以應用于不同的雷達系統。最后分別列舉了該系統在連續波雷達和脈沖雷達中的一種

2011-12-15 17:17:03 64

64 基于FPGA的雷達信號處理系統設計的論文

2015-10-30 10:38:12 6

6 地面脈沖多普勒雷達信號處理系統方案,下來看看

2016-12-26 17:19:11 6

6 基于FPGA+DSP實時圖像采集處理系統設計

2017-01-03 11:41:35 9

9 基于雙DSP和雙FPGA的高速圖像處理系統設計_吳雷

2017-03-16 09:28:51 2

2 基于DSP_FPGA的LFMCW雷達測距信號處理系統設計_陳林軍

2017-03-19 19:07:17 4

4 基于FPGA的通用傳感器信號處理系統設計_李輝

2017-03-19 19:07:17 3

3 基于FPGA和DSP的高速圖像處理系統

2017-10-19 13:43:31 19

19 基于DSP的數字信號采集處理系統設計

2017-10-19 15:10:22 25

25 基于DSP和FPGA的模塊化實時圖像處理系統設計

2017-10-23 14:09:42 9

9 要求,因此,需采用專用的數字信號處理器(DSP)來進行高速運算。盡管當前的數字信號處理器已達到較高水平, 但單片DSP芯片的處理能力還是不能滿足寬帶雷達的性能要求,需要引入并行處理技術,在本設計中使用4片DSP芯片組成并行處理

2017-10-31 09:58:04 0

0 為解決高速數字圖像處理系統和實時性相沖突的要求,設計了以多DSP(數字信號處理器TMS320C6416)和現場可編程門陣列(FPGA)相結合的實時圖像處理系統。重點介紹了該系統的硬件資源選擇、基本組

2017-11-18 12:34:02 4034

4034

近年來,雷達在軍用和民用領域都獲得了巨大的發展。雷達信號處理系統是雷達的關鍵模塊,對雷達定位精度起著決定性作用。FPGA 以其眾多的優點,在雷達信號處理系統中被廣泛使用。本文探究FPGA 在雷達信號

2017-11-22 07:25:02 4250

4250

FPGA+DSP的數字硬件系統正好結合了兩者的優點,兼顧了速度和靈活性。本文以導引頭信號處理系統為例說明FPGA+DSP系統中FPGA的關鍵技術。

2019-01-08 08:36:00 2448

2448

本系統以FPGA作為高性能實時信號處理系統的數據采集和控制中心,2片DSP為數據處理中心,主要包括4個功能模塊——數據采集模塊、FPGA數據控制模塊、DSP處理模塊和通信模塊,系統結構框圖如圖1所示。

2019-04-23 08:29:00 3426

3426

高速中頻采樣信號處理平臺在實際應用中有很大的前景,提出采用FPGA+DSP的處理結構,結合高性能A/D和D/A處理芯片,設計了一個通用處理平臺,并對其主要性能進行了測試。

2018-10-18 16:36:48 4637

4637

與Avnet Electronics Marketing共同開發的帶有高速模擬的Kintex-7 FPGA DSP套件是用于開發高性能信號處理應用的DSP域目標平臺。

2018-11-22 06:29:09 3614

3614 基于FPGA的嵌入式信號處理系統設計方案

2021-06-02 11:04:33 0

0 基于FPGA的嵌入式信號處理系統設計方案

2021-06-02 11:04:33 0

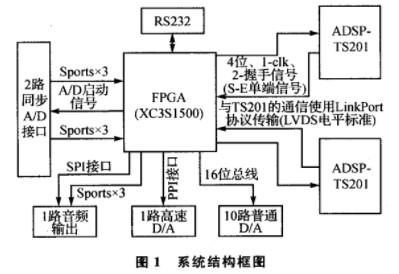

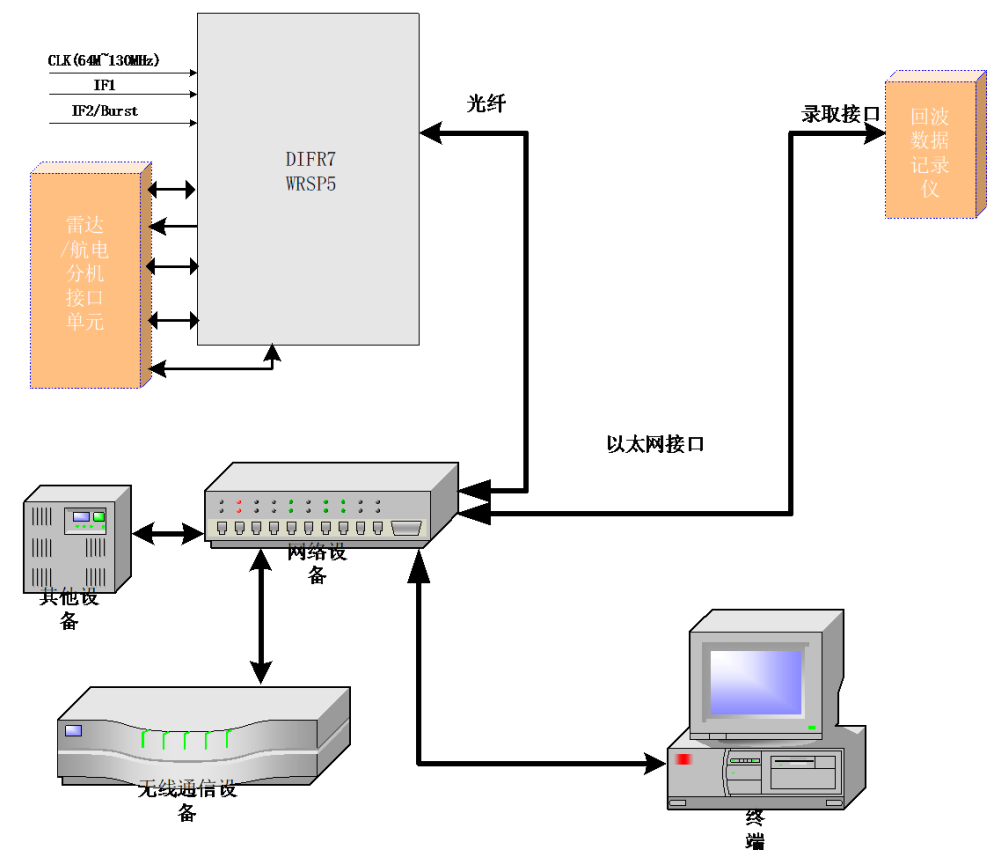

0 毫米波雷達信號處理系統(WRSP)是杭州淞柏科技公司研制的全功能高端雷達信號處理器,該處理器采用了脫機運行、網絡接口,采用 DIFR硬件平臺,為機載、艦載船載、車載等各種平臺雷達。在設計上采用高集成方案,高速DSP+FPGA 完成雷達信號處理模式,可支持各種不同方式的脈沖壓縮和補盲。

2021-11-24 15:26:28 969

969

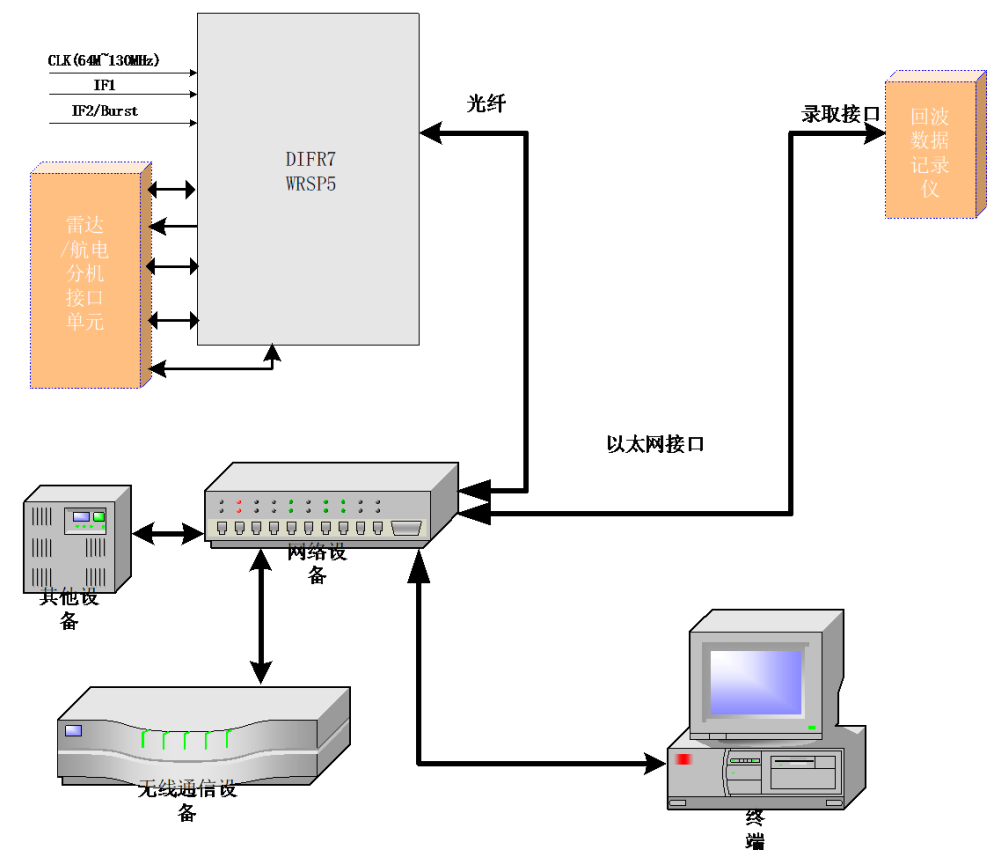

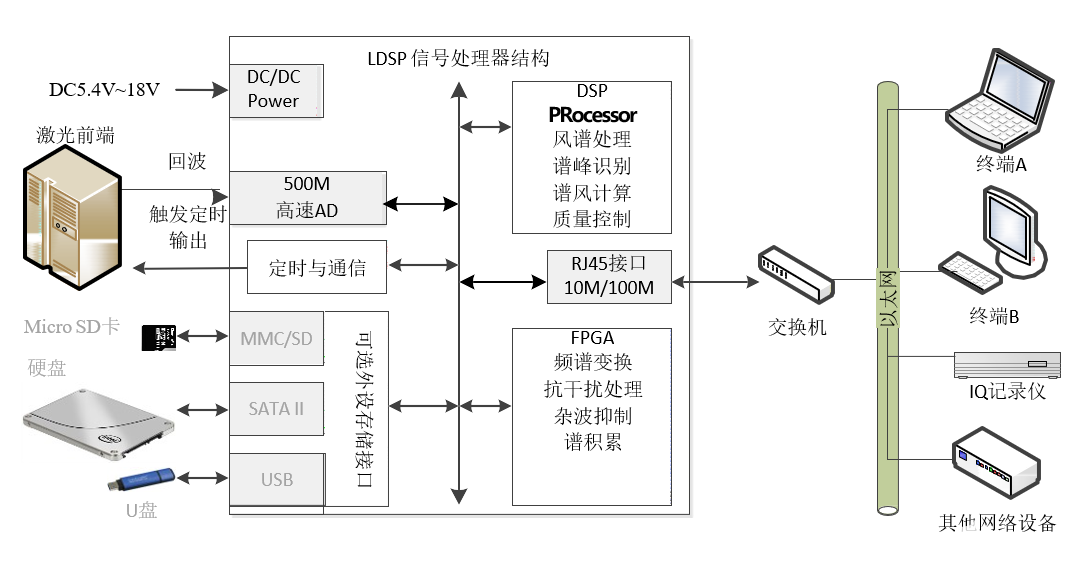

激光雷達信號處理系統(LDSP )是專為激光雷達研發的高性能、高集成、低功耗數字信號處理器。該信號處理器采用高速高精度 ADC、大規模 FPGA及高速 DSP等處理芯片,處理功能強大、速度高、功耗

2021-11-24 15:24:20 2142

2142

基于FPGA+DSP彈載SAR信號處理系統設計

2021-12-27 18:58:51 21

21 AD9223是一種采用高速CMOS處理和新穎的4級流水線結構的高性能、低噪聲、單電源、12位模/數變換器。適用于航海、通信、雷達、醫療等領域的數據采集系統。

2022-03-30 11:15:40 2547

2547

隨著高性能信號處理系統對運算速度、通信速率等要求的不斷提高,單獨的處理器(如FPGA或DSP)無法滿足高速實時信號處理的需求。

2023-02-27 16:27:55 4762

4762

電子發燒友App

電子發燒友App

評論