一、LPC32x0通用描述

恩智浦公司的90nm工藝ARM926EJ-S核(包括矢量浮點(diǎn)聯(lián)合處理器),以及大量的標(biāo)準(zhǔn)片上外圍.CPU頻率最高達(dá)到266Mhz。

ARM926EJ-S核采用了哈佛結(jié)構(gòu),5級流水線還有一個(gè)集成存儲(chǔ)管理單元MMU。MMU支持現(xiàn)代操作系統(tǒng)需要的虛擬存儲(chǔ)技術(shù)。

LPC32X0包括了256KB的片上靜態(tài)RAM,NAND FLASH接口,以太網(wǎng)MAC,LCD控制器(支持STN,TFT),還有一個(gè)擴(kuò)展的總線接口,支持SDR和DDR SDRAM。另外還有一個(gè)USB2.0接口,7個(gè)UART,2個(gè)I2C總線接口,2個(gè)SPI/SSP接口,2個(gè)I2S接口,2個(gè)單輸出PWM,一個(gè)電機(jī)控制PWM,6個(gè)通用定時(shí)器(具有輸入捕獲和比較輸出功能),一個(gè)安全數(shù)字(SD)接口,一個(gè)10比特ADC(與觸摸屏公用)。

二、主要特點(diǎn)

1. ARM926EJS 處理器,CPU時(shí)鐘做高可達(dá)266MHZ

2.?向量浮點(diǎn)聯(lián)合處理器(VFP)

3. 32KB指令高速緩存,32KB數(shù)據(jù)緩存

4.?可選擇從不同的外圍設(shè)備啟動(dòng):NAND Flash, SPI memory,USB,UART,或者靜態(tài)存儲(chǔ)器。

5. 多層AHB系統(tǒng)為每個(gè)AHB主機(jī)提供單獨(dú)的總線,包括CPU的指令、數(shù)據(jù)總線,DMA控制器的兩個(gè)數(shù)據(jù)總線,USB控制器總線,LCD控制器總線,以太網(wǎng)MAC控制器總線。除非兩個(gè)主機(jī)試圖同時(shí)訪問同一個(gè)從設(shè)備,那么就不存在總裁延時(shí)。

6. 2個(gè)NAND FLASH控制器:一個(gè)用于單級NAND FLASH設(shè)備,一個(gè)用于多級NAND FLASH 設(shè)備。

7. 主機(jī)中斷控制器(MIC)以及兩個(gè)從設(shè)備中斷控制器(SIC),支持74個(gè)中斷源。

8. 8通道通用DMA(GPDMA)控制器,用于SD卡接口,高速UART,I2S接口,SPI接口,以及存儲(chǔ)器之間的傳輸。

9.串行接口:

a)10/100 以太網(wǎng) MAC,帶有專用的DMA控制器。

b)USB接口,支持8個(gè)設(shè)備,主機(jī),OTG(專用的PLL用于產(chǎn)生要求的48MHZ USB 時(shí)鐘)

c)7個(gè)高速UART,都支持64B的FIFO

d)2個(gè)SPI,2個(gè)SSP,2個(gè)I2C,2個(gè)I2S。

10. 其他外圍

a)LCD控制器,帶有專用的DMA,支持1024X768顯示分辨率

b)保密數(shù)字存儲(chǔ)卡接口(SD)

c)GPIO

d)10比特,400KHZ,ADC.

e)實(shí)時(shí)時(shí)鐘(RTC),獨(dú)立的供電引腳以及32KHZ振蕩器。

f)32比特,通用高速定時(shí)器。

11. 標(biāo)準(zhǔn)ARM測試/調(diào)試接口

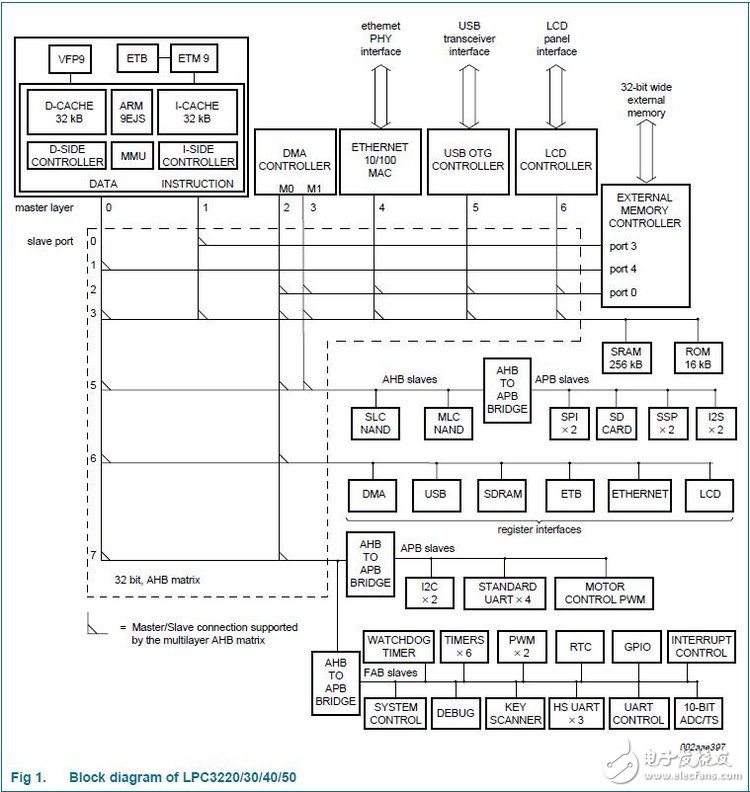

三、結(jié)構(gòu)圖

四、功能概述

1. VFP

VFP提供單精度、雙精度的加減乘除以及乘加運(yùn)算。

2. Emulation & debugging

LPC32X0支持通過專用的JTAG串行接口進(jìn)行在線調(diào)試和評估,一個(gè)嵌入式的跟蹤緩沖器可以跟蹤程序的執(zhí)行過程。

3.?? 嵌入式ICE

標(biāo)準(zhǔn)的ARM EmbeddedICE 邏輯支持在片調(diào)試。目標(biāo)系統(tǒng)的調(diào)試要求一個(gè)主機(jī)運(yùn)行在調(diào)試軟件并且要求一個(gè)嵌入式ICE 協(xié)議轉(zhuǎn)換器。嵌入式ICE 協(xié)議轉(zhuǎn)換器將遠(yuǎn)端調(diào)試協(xié)議命令轉(zhuǎn)換成訪問ARM核的JTAG數(shù)據(jù)。

4. ARM核有一個(gè)調(diào)試通道(DCC), Debug Communication Channel。主機(jī)Debugger通過?DCC和運(yùn)行程序進(jìn)行通信,而不打斷程序的運(yùn)行或讓程序進(jìn)入調(diào)試狀態(tài)。

5.

6. AHB 陣列

AHB用于內(nèi)部塊間的通信。AHB是ARM定義的高速總線,是ARM總線結(jié)構(gòu)的一部分。AHB是高帶寬低延時(shí)總線,支持多主機(jī)仲裁和總線授權(quán)/請求機(jī)制。

多層AHB為7個(gè)AHB主機(jī)分別配備了單獨(dú)的AHB總線:

.CPU 數(shù)據(jù)總線

.CPU命令總線

.通用DMA主機(jī)0

.通用DMA主機(jī)1

.以太網(wǎng)控制器

.USB控制器

.LCD控制器

7.APB 是外圍設(shè)備與AHB之間的橋梁

8. FAB :是連接某些特別的外圍的橋,一個(gè)AHB時(shí)鐘進(jìn)行讀操作,2個(gè)AHB時(shí)鐘用于寫操作。

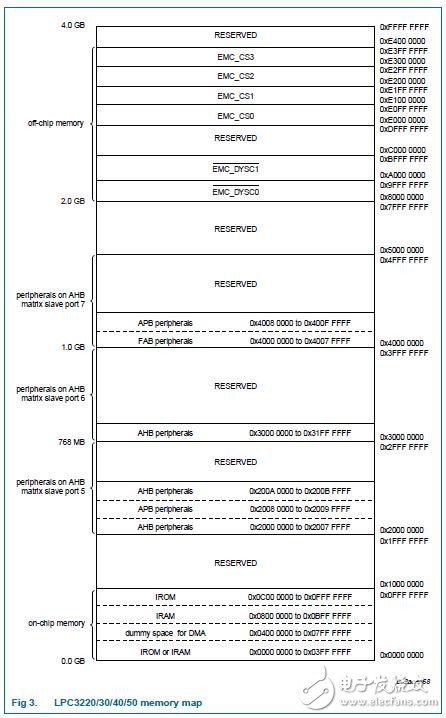

9.物理地址分配

10、 片上ROM

16KB的ROM包含上電引導(dǎo)程序,決定從以下四個(gè)接口中引導(dǎo)進(jìn)程序: UART5,SSP0(SPI模式),EMC的CS0或者NAND FLASH.

上電完成以后,程序總是從ROM開始執(zhí)行。bootstrap軟件首先讀取SERVICE輸入(GPI_1),如果SERVEICE為低,那么從UART5下載程序到IRAM并且開始執(zhí)行下載的代碼。如果SERVICE為高,那么Bootstrap跳到常規(guī)引導(dǎo)。首先檢查SPI存儲(chǔ)器,看是否存在引導(dǎo)信息,如果存在SPI存儲(chǔ)器,并且有引導(dǎo)信息,那么下載里邊的代碼并開始執(zhí)行。如果SPI不存在或者不存在引導(dǎo)信息,那么開始檢查EMC 的CS0空間,最后檢查NAND Flash空間。

11. 動(dòng)態(tài)Memory空間:?

DYCS0: 0X8000 0000~0X9FFF FFFF

DYCS1: 0XA000 0000~0XBFFF FFFF

靜態(tài)Memory空間:

CS0: 0XE000 0000~0XE0FF FFFF

CS1: 0XE100 0000~0XE1FF FFFF

CS2: 0XE200 0000~0XE2FF FFFF

CS3: 0XE300 0000~0XE3FF FFFF

12. AHB主機(jī)外圍

LPC32x0實(shí)現(xiàn)4個(gè)AHB主機(jī)外圍,包括GPDMA,MAC,USB以及LCD控制器。

13. GPDMA控制器

GPDMA實(shí)現(xiàn)外圍到存儲(chǔ)器、存儲(chǔ)器到外圍、外圍到外圍、存儲(chǔ)器到存儲(chǔ)器的數(shù)據(jù)傳輸。

14. 系統(tǒng)功能

.....To be continued.

電子發(fā)燒友App

電子發(fā)燒友App

評論