1 引 言

AES加密算法的一種優化的FPGA實現方法

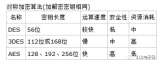

隨著密碼分析水平,芯片處理能力和計算技術的不斷進步,des的安全強度已經難以適應新的安全需要,其實現速度、代碼大小和跨平臺性均難以繼續滿足應用需求。因此,nist(美國國家標準與技術研究所)籌劃aes(高級數據加密標準)算法,旨在取代des,以保護21世紀敏感政府信息的新型加密標準。rijndael算法以其簡潔、高效、安全和原則性的設計被接納為aes,并于2001年11月26日正式公布在fips(federal information processingstandards)出版的fips-pub 197中。作為des的繼承者,aes自從被接納為標準之日起就已經被工業界、銀行業和行政部門作為事實上的密碼標準。

隨著網絡傳輸速度提升為gigabits數量級,業界對算法的執行速度的要求也越來越高,基于軟件的密碼算法便顯得性能不足,需要采用硬件加密的方式,他采用一些特殊的優化技術(如流水線和查找表等),可極大地提高數據的流量并減少密鑰的生成時間。另外,用硬件實現加密算法及與之相關的密鑰生成過程,并且封裝到芯片中,因為他們不易被外部攻擊者讀取或更改,會有較高的物理安全性。因此,基于硬件的密碼算法就受到業界的普遍關注。以fpga為代表的可重構硬件以其自身所固有的特點既具有硬件的安全性和高速性又有軟件的靈活性和易維護性,已經成為分組密碼算法硬件實現的熱點研究方向。

本文介紹aes加密算法的一種fpga實現的方法以及對其加密速度的優化處理技巧。

2 aes加密算法簡介

aes是一種迭代分組密碼,采用的是代替/置換網絡(spn)。他將明文分組長度固定為128 b,而且僅支持128,196或256 b的密鑰長度,本文僅對密鑰長度為128 b的情況進行討論。

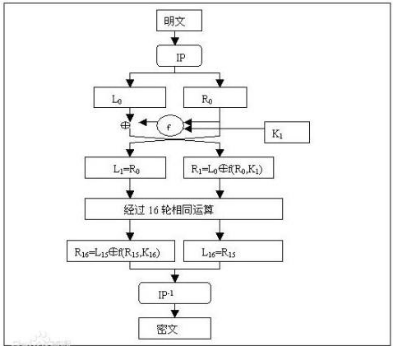

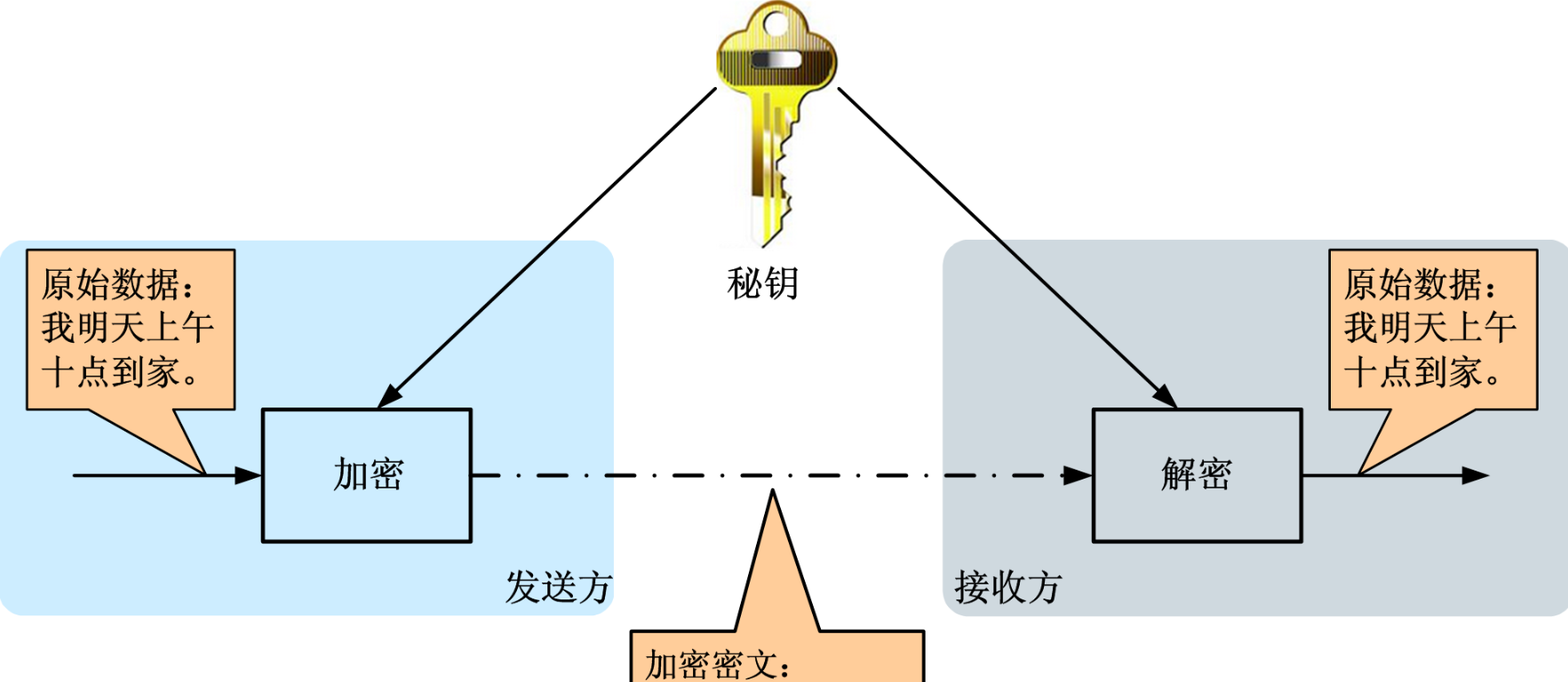

aes加密算法的實現包括密鑰擴展過程和加密過程。加密過程又包括一個作為初始輪的初始密鑰加法(addroundkey),接著進行9次輪變換(round),最后再使用一個輪變換(finalround),如圖1所示。

每一次round均由subbytes,shiftrows,mixcolumns和addroundkey共4個步驟構成,finalround包含除mixcolumns這一步外的其他3個步驟,round結構如圖2所示。

輪變換及其每一步均作用在中間結果上,將該中間結果稱為狀態,可以形象地表示為一個4*4 治療大三陽去哪家治好b的矩陣。

3 aes加密算法的優化

3.1 字節代換(subbytes)

步驟subbytes是rijndael密碼中惟一的非線形變換。他是一個磚匠置換,該置換包含一個作用在狀態字節上的s-盒,用srd表示,他是由字節在gf(28)域中求其乘法逆并外加一個仿射變換(仿射變換的作用是復雜化s-盒的代數表達式)實現,假設該步的輸入為a,輸出為b,即b=srd(a)。由于該步驟是一種非線形面向字節的變換,是將一個8位二進制數據轉換為另一個不同的8位二進制數據,這里要求一一對應,并且替換結果不能超出8位,可以通過構造可逆的s-盒來實現。

根據字節代換的要求和特點,具體實現時,可以將s-盒用一個16*16 b的置換表來表示,通過查表即可實現該步變換,避免了復雜的乘法運算。

3.2 行移變換(shiftrows)

shiftrows是線形變換,他和列混合運算相互影響,在多輪變換后,使密碼信息達到充分的混亂,提高非線形度。

行變換是在狀態的每個行間進行的,是狀態中的行按照不同的偏移量進行循環左移運算,在明文分組長度為128 b,密鑰長度為128 b時,shiftrows對狀態的每行作用如下列表達式所示:

顯而易見,可以通過對每個字節的移位簡單實現該步變換。

3.3 列混合變換(mixcolumns)

mixcolumns是線形變換,是以狀態的列為單位進行的操作。假設該步的一列的輸入為a,輸出為b,mixcolumns對狀態的每列作用如下列表達式:

上述矩陣乘法為gf(28)有限域中的乘法運算,并且有一個因子為常數。由于gf(28)有限域中的每一個元素都能夠寫成02的不同冪次的和(例如:15=01○+022 ○+024),因此,乘以任何常數的乘法都可以通過反復的乘以02和異或運算來實現。可將矩陣乘法中的常數因子分解為02的不同冪次和,矩陣乘法轉換為與02的乘法和異或運算。將gf(28)域中的每一個元素與02的乘積存儲在一張16*16 b查找表中,記作xtime(?)(例如:02*a=xtime(a))。所以,該步驟可以通過查表和異或運算實現,表達式如下(假設該步的一列的輸入為a,輸出為b):

3.4 密鑰加法(addroundkey)

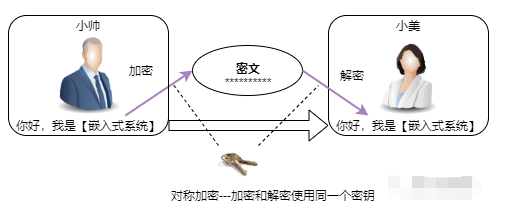

addroundkey是將輪密鑰中的各個字節與狀態中的各個字節逐位異或,實現密碼和密鑰的混合。輪密鑰是由初始密鑰通過密鑰擴展得到的。

3.5 密鑰擴展(expandedkey)

以明文分組長度為128 b,密鑰長度為128 b為例,expandedkey將初始密碼密鑰(初始密鑰可以形象的排列成一個4*4 b的矩陣)作為初始密鑰加法的密鑰,以后的各輪輪密鑰是經過下列表達式的密鑰擴展函數得到的(k[i][j]表示初始密鑰狀態的第i行第j列,w[i][j]表示擴展后密鑰狀態的第i行第j列,nk表示密鑰分組的列數,nr表示輪數,nb表示明文分組的列數,這里nk=4,nr=10,nb=4):

當nk6時:

其中,srd(?)是s-盒的置換表,rc(j/nk)是一個輪常量,用于消除對稱,可以通過查輪常量的表來得到。

密鑰的選取:第i輪的輪密鑰就是由矩陣w中第nb*i列到nb*(i+1)-1列給出。

3.6 流水線結構

流水線結構是實現流程中加入寄存器和相應的邏輯電路,將整個過程劃分為前后相連的多級實體,每一級只完成數據處理的一個步驟,一個時鐘周期完成一級數據處理,然后在下一個時鐘到來時將處理后的數據傳遞給下一級;第一組數據進入流水線后,經過一個時鐘周期傳遞到第二級,同時第二組數據進入笫一級,數據隊列依次前進。使一個時鐘內有多個數據塊同時在各級中處理。雖然每組數據都要經過整個流水線后才能得到最后的計算結果,但是作為整個流水線,每個時鐘周期都能計算出一組結果,所以平均計算一組數據幾乎只需要一個時鐘周期的時間,大大提高了數據處理速度,保證了整個系統以較高的頻率工作。

流水線技術通過同時處理多個數據塊的方法提高吞吐量,其代價是硬件資源的增加。流水線結構只能用于非反饋加密模式。

4 實現及仿真

粗線代表數據線,細線代表控制線。控制信號從輸入接口進入,數據和密鑰通過數據總線進入,根據控制模塊來進行數據傳輸,更換密鑰和加密運算。

從第3節的分析可以看出,aes算法可以通過對srd表,xtime表和rc表的查詢和通過組合邏輯實現的移位和異或運算來實現。這些實現方法代替了繁瑣的乘法運算,提高了加密速度。

采用了流水線結構來同時處理多個數據塊,提高吞吐量。

使用輪函數完全展開的開環結構,將輪函數劃分成4級流水線,輪函數中的每一個步驟都是一級,并在級與級之間加入寄存器暫存中間狀態的數據以消除競爭,從而實現了輪函教內部的完全流水,如圖4所示。

其中,控制信號sel1,sel2.sel3干sel4分別是每一級(每一步數據)處理是否完成的標志。

在輪函數的外部,將每一輪函數都作為外部流水中的一級,從而實現了算法內部外部的完全流水結構,如圖5所示。

其中,控制信號sel0~sel10分別是每一輪數據處理是否完成的標志。

由于采用流水線結構只能用于非反饋加密模式,所以aes算法的實現使用的是電碼本模式(ecb)的工作方式。

密鑰擴展這一步放在所有加密步驟之前進行。再先輸入初始密鑰,然后通過對srd表和rc表的查詢和通過組合邏輯實現的移位和異或運算完成密鑰的擴展,并將結果存儲在一個176 b的寄存器中。在密鑰擴展完成后再進行以后的數據加密,在進行每一輪的密鑰法時,將直接在該寄存器中選擇輪密鑰。

針對afs算法和fpga的特點,對每一步的處理都采用以字節為單位的對寄存器進行操作的方式。往quartusii5.0中,用vhdl硬件描述語言實現了該算法,經過仿真,結果如下:

5 擴展及應用

迎過fpga來實現aes的解密算法(在此僅討論分組長度為128 b,密鑰長度為128 b時的情況),同樣可以用查找表和簡單的組合邏輯來實現。考慮到使用等價解密算法沒有多少好處,所以選用直接解密算法,依舊可以采用輪函數內部外部完全流水的流水線技術來提高解密速度。

注意:

(1)解密算法中的逆字節代換這一步驟可通過查逆srd表實現。

(2)解密算法中的逆行移變換這一步驟可直接將狀態的每一行循環右移實現,如下列表達式所示:

也可以將狀態的第二行和第四行互換后進行加密算法中的行移變換,然后再將變換后的狀態的第二行和第四行互換來實現解密算法中的逆行移變換這一步驟。這樣就利用了加密算法中的行移變換的模塊(此方法僅適用于分組長度為128 b的情況)。

(3)解密算法中的逆列混合變換這一步驟中,由玻尿酸隆鼻均價于矩陣乘法的系數為09,0e,0b,0d,如下列表達式所示(假設該步的一列的輸入為a,輸出為b):

可以通過一個預處理步驟和一個列混合變換步驟來實現,頇處理步驟如下列表達式所示(a是一列):

這樣就利用了加密算法中的列混合變換的模塊。

在同時支持加解密的模塊中,密鑰擴展和密鑰加法的部分可以同時用于這兩種模式,密鑰擴展部分只須輸入對應的肌密的初始密鑰后做和加密同樣的密鑰擴展,然后按照解密所需要使用的輪密鑰的順序重新排列,存入寄存器等待使用即可,這樣可以節約資源。

由此,可以將aes的加解密算法統一起來,在一個FPGA模塊中實現。通過avr或arm等處理器的控制來選擇fpga是執行加密過程還是解密過程以及是否更換新的初始密鑰,形成完整的加解密模塊,可作為單獨的密碼機使用或通過各種接口與計算機,工控機等其他主控設備連接完成對數據的加解密。

aes加解密算法可以應用于虛擬專用網、sonet、遠程訪問服務器、高速atm、以太路由器、移動通信、衛星通信、電子金融業務等領域,為其提供安全、可靠、快速的解決方案。

STM32/STM8

意法半導體/ST/STM

電子發燒友App

電子發燒友App

評論