本文主要詳解PCI總線與PXI總線有什么區(qū)別,首先介紹了PCI 總線結(jié)構(gòu)圖、特點(diǎn)及PCI總線性能,其次闡述了PXI總線的特性,最后介紹了PCI總線與PXI總線的區(qū)別。

2018-05-24 09:15:23 13958

13958

和初始化板卡. b. 使能 PCI 中斷之后, 用戶即可調(diào)用 PCI驅(qū)動(dòng)程序里的讀寫等函數(shù)寫一段簡(jiǎn)單的讀寫測(cè)試程序。 (2) 中斷服務(wù)程序: 這個(gè)函數(shù)接收到中斷后交給中斷服務(wù)線程來(lái)處理, 用戶一般不需要

2020-09-06 12:43:10

接口芯片主要有AMCC公司的AMCCS59xx系列和PLX公司的PCI90xx系列。在PLX系列產(chǎn)品中,PCI9052是一款常用的PCI總線目標(biāo)接口芯片,該芯片最大的特色是帶有一個(gè)ISA接口,通過(guò)它可

2018-12-17 11:23:00

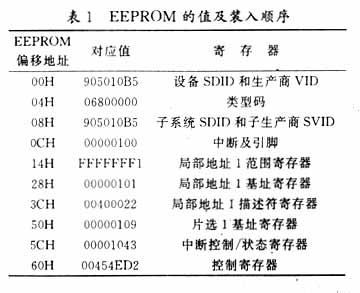

。可以從兩個(gè)局部總線中斷輸入生成一個(gè)PCI中斷。(3)總線驅(qū)動(dòng)。PCI9050直接生成所有的控制、地址和數(shù)據(jù)信號(hào),用于驅(qū)動(dòng)PCI總線,不需要額外驅(qū)動(dòng)電路。 (4)串行EEPROM接口。PCI9050有一

2018-11-29 14:52:52

PCI總線接口的開發(fā)提供了一種簡(jiǎn)潔的方法,設(shè)計(jì)者只需設(shè)計(jì)出本地總線接口控制電路,即可實(shí)現(xiàn)與PCI總線的高速數(shù)據(jù)傳輸。圖3是應(yīng)用PCI9054作為接口芯片,開發(fā)PCI總線擴(kuò)展卡的總體硬件框架圖 下面簡(jiǎn)單

2018-12-05 10:12:42

框架圖,最后給出一個(gè)簡(jiǎn)單的實(shí)例。關(guān)鍵詞:PCI總線;局部總線;PCI9054一、 引言PCI 總線是英特爾公司推出的一種高性能局部總線,其數(shù)據(jù)總線為32 位,且可擴(kuò)展成64 位,最大數(shù)據(jù)傳輸速率為

2008-10-09 11:23:38

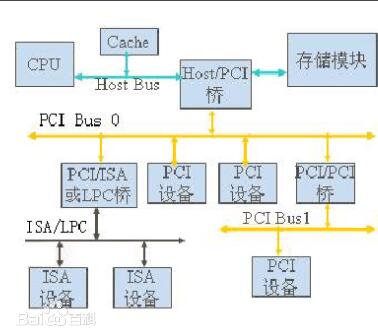

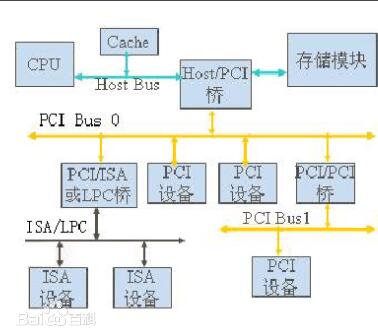

的需要。 (2)多總線共存 采用PCI總線可在一個(gè)系統(tǒng)中讓多種總線共存,容納不同速度的設(shè)備一起工作。通過(guò)HOST-PCI橋接組件芯片,使CPU總線和PCI總線橋接;通過(guò)PCI-ISA/EISA橋接

2012-04-06 14:37:24

PCI總線特點(diǎn)是什么?PCI接口開發(fā)現(xiàn)狀如何?如何去設(shè)計(jì)PCI接口?

2021-04-29 07:09:04

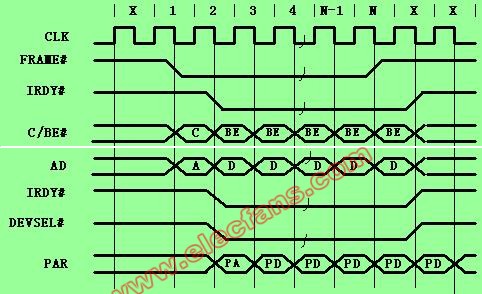

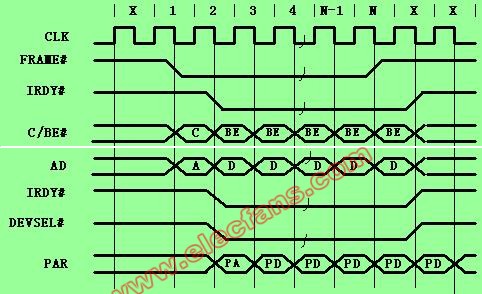

不同于ISA總線,PCI總線的地址總線與數(shù)據(jù)總線是分時(shí)復(fù)用的。這樣做的好處是,一方面可以節(jié)省接插件的管腳數(shù),另一方面便于實(shí)現(xiàn)突發(fā)數(shù)據(jù)傳輸。在做數(shù)據(jù)傳輸時(shí),由一個(gè)PCI設(shè)備做發(fā)起者(主控

2019-10-16 09:02:10

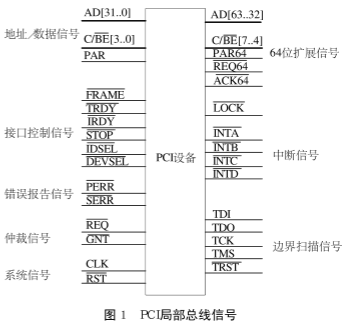

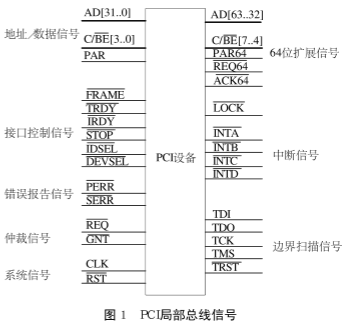

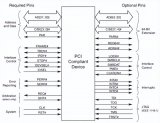

PCI總線的信號(hào)定義PCI總線是一條共享總線,在一條PCI總線上可以掛接多個(gè)PCI設(shè)備。這些PCI設(shè)備通過(guò)一系列信號(hào)與PCI總線相連,這些信號(hào)由地址/數(shù)據(jù)信號(hào)、控制信號(hào)、仲裁信號(hào)、中斷信號(hào)...

2022-02-16 06:48:12

個(gè)人電腦中使用最為廣泛的接口,幾乎所有的主板產(chǎn)品上都帶有這種插槽。PCI插槽也是主板帶有最多數(shù)量的插槽類型,在目前流行的臺(tái)式機(jī)主板上,ATX結(jié)構(gòu)的主板一般帶有5~6個(gè)PCI插槽,而小一點(diǎn)的MATX主板也都帶有2~3個(gè)PCI插槽,可見其應(yīng)用的廣泛性。...

2021-11-24 07:20:59

最近在研究總線擴(kuò)展IO口,查了很多資料都查不到實(shí)現(xiàn)的原理,都是各種介紹PCI協(xié)議或者引腳的,我想了很久說(shuō)下我的猜測(cè)希望有知道的人幫我指點(diǎn)一下,對(duì)于32位的的PCI總線,總線里面AD0到AD31分成4

2017-01-17 18:43:47

些擴(kuò)展,僅就單片機(jī)與PCI設(shè)備間的通信來(lái)說(shuō),意義不大。PCI總線是高性能局部總線,工作頻率0~33MHz,可同時(shí)支持多組外圍設(shè)備。在這里,我們只關(guān)心單片機(jī)與一個(gè)PCI設(shè)備間通信的情況,而且是以單片機(jī)

2019-04-24 07:00:09

PCI總線是一種不依附于某個(gè)具體處理器的局部總線。從結(jié)構(gòu)上看,PCI是在CPU和原來(lái)的系統(tǒng)總線之間插入的一級(jí)總線,具體由一個(gè)橋接電路實(shí)現(xiàn)對(duì)這一層的管理,并實(shí)現(xiàn)上下之間的接口以協(xié)調(diào)數(shù)據(jù)的傳送。管理器提供了

2008-12-09 13:46:13

滿足高速實(shí)時(shí)傳輸?shù)男枨蟆_x擇了Altera公司的PCI編譯器軟件包來(lái)實(shí)現(xiàn)PCI接口控制電路。該軟件包為PCI接口提供了一個(gè)完整的解決辦法,包含了PCI控制電路的所有功能。用戶可以通過(guò)修改參數(shù)生成所需

2012-11-28 15:38:05

PCI9052是美國(guó)PLX科技有限公司推出的一款PCI總線從屬接口芯片(但不具有DMA功能)。它可以提供高性能的從目標(biāo)PCI接口板卡與PCI總線的連接,支持寬范圍速率的本地總線,最高可達(dá)132 MB

2021-04-15 07:02:21

DMA的原理是什么?DMA中斷的配置流程是如何去實(shí)現(xiàn)的?

2021-12-08 06:37:42

廣泛采用的是32-bit、33MHz的PCI 總線,64bit的PCI插槽更多是應(yīng)用于服務(wù)器產(chǎn)品。從結(jié)構(gòu)上看,PCI是在CPU和原來(lái)的系統(tǒng)總線之間插入的一級(jí)總線,具體由一個(gè)橋接電路實(shí)現(xiàn)對(duì)這一層的管理

2009-05-03 22:15:14

和驅(qū)動(dòng)程序可以在各種不同的平臺(tái)上運(yùn)行[1]。 實(shí)現(xiàn)PCI總線協(xié)議一般有兩種方法,一是用FPGA設(shè)計(jì)實(shí)現(xiàn),但PCI協(xié)議比較復(fù)雜,因此難度較大;二是采用PCI總線控制芯片,如AMCC公司的S5933、PLX

2019-09-24 22:18:02

, 因此如何來(lái)實(shí)現(xiàn)該監(jiān)控系統(tǒng)中大量數(shù)據(jù)的高效、快速、準(zhǔn)確地采集和傳輸成為設(shè)計(jì)該監(jiān)控系統(tǒng)所面臨的一個(gè)主要難題。而本文所研究的基于PCI 總線的高速數(shù)據(jù)通信卡的設(shè)計(jì)正是解決上述難題的關(guān)鍵技術(shù)之一。PCI

2010-09-22 08:51:09

編制設(shè)備驅(qū)動(dòng)程序才能實(shí)現(xiàn)對(duì)PCI總線設(shè)備的完全訪問(wèn)。 應(yīng)用程序?qū)υO(shè)備I/O進(jìn)行Win32調(diào)用,這個(gè)調(diào)用由I/O系統(tǒng)服務(wù)接收。I/O管理器從這個(gè)請(qǐng)求構(gòu)造一個(gè)合適的I/O請(qǐng)求包(IRP)。在最簡(jiǎn)單

2009-04-20 10:51:10

道、奇偶校驗(yàn)和重試模塊組成。PCI從設(shè)備接口實(shí)現(xiàn)的功能是將一個(gè)不符合PCI總線協(xié)議的設(shè)備橋接到PCI總線上,為計(jì)算機(jī)PCI總線和用戶應(yīng)用之間傳輸數(shù)據(jù)提供一個(gè)數(shù)據(jù)通道。該從設(shè)備接口為用戶提供了一個(gè)簡(jiǎn)單

2019-05-29 05:00:02

PCI9052PCI9052是一款面向低端應(yīng)用的高性能、工作在目標(biāo)(從)模式的PCI接口芯片,支持PCI 2.1總線規(guī)范。該芯片的局部總線可以通過(guò)編程設(shè)置為8/16/32位的(非)復(fù)用總線,且局部總線時(shí)鐘與PCI總線時(shí)鐘

2018-12-17 11:29:06

250 MB/s。對(duì)于需要與主機(jī)進(jìn)行大容量傳輸?shù)南到y(tǒng)來(lái)說(shuō),該總線標(biāo)準(zhǔn)的優(yōu)勢(shì)是非常明顯的。由于PCIE總線硬件設(shè)計(jì)簡(jiǎn)單,吞吐量大,軟件向下兼容,只要找到合適的總線接口芯片,很容易將現(xiàn)有的PCI總線設(shè)備

2019-05-21 05:00:02

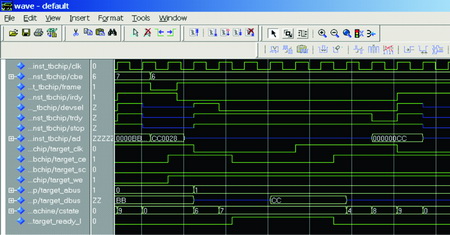

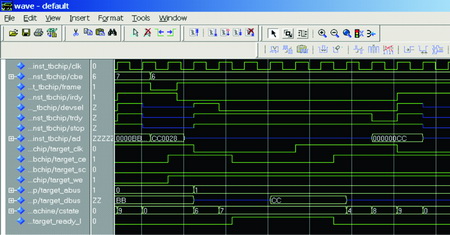

本文的應(yīng)用背景為某一工業(yè)測(cè)控系統(tǒng),該系統(tǒng)采用FPGA實(shí)現(xiàn)測(cè)量數(shù)據(jù)的采集和控制信號(hào)的輸出,通過(guò)定制PCI接口IP實(shí)現(xiàn)一個(gè)32位目標(biāo)設(shè)備的PCI總線接口轉(zhuǎn)換。PCI核選用AlteraPCI編譯器所包括

2018-12-04 10:35:21

PCI局部總線不僅是目前最新的計(jì)算機(jī)總線,而且是一種兼容性最強(qiáng)、功能最全的計(jì)算機(jī)總線。它可同時(shí)支持多組外圍設(shè)備,而且不受制于處理器,為CPU及高速外圍設(shè)備提供高性能、高吞吐量、低延遲的數(shù)據(jù)通路。圖形

2019-04-17 07:00:06

如何實(shí)現(xiàn)單片機(jī)與PCI總線接口的并行通信?

2021-04-29 07:14:26

PCI總線是什么?有什么特點(diǎn)?如何利用FPGA去設(shè)計(jì)PCI總線的接口電路?設(shè)計(jì)PCI總線接口時(shí)應(yīng)注意哪些問(wèn)題?

2021-05-31 06:37:24

什么是PCI總線?它有什么特點(diǎn)?如何利用FPGA設(shè)計(jì)PCI總線的接口電路?設(shè)計(jì)PCI總線接口時(shí)應(yīng)注意哪些問(wèn)題?

2021-04-29 06:10:31

如何利用雙端口RAM去實(shí)現(xiàn)PCI總線接口?

2021-05-06 06:30:53

如何去采用PCI9030芯片實(shí)現(xiàn)從ISA總線到PCI總線的轉(zhuǎn)接卡的設(shè)計(jì)?有哪些方法?其過(guò)程是怎樣的?

2021-07-01 08:00:36

本文提出了一種新的包括PCI9054單周期讀、寫和存儲(chǔ)器映射傳輸?shù)脑O(shè)計(jì),并討論了通用PCI總線高速數(shù)據(jù)采集卡的實(shí)現(xiàn)方案。

2021-06-08 06:28:30

怎么實(shí)現(xiàn)基于IP內(nèi)核的PCI總線接口設(shè)計(jì)?

2021-05-27 06:34:05

PCI總線特點(diǎn)及開發(fā)現(xiàn)狀PCI接口配置空間的實(shí)現(xiàn)求一款在PCI總線上利用FPGA技術(shù)設(shè)計(jì)PCI總線接口的設(shè)計(jì)方案

2021-04-15 06:17:20

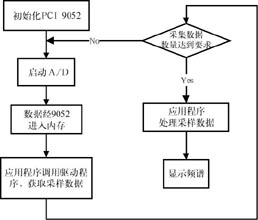

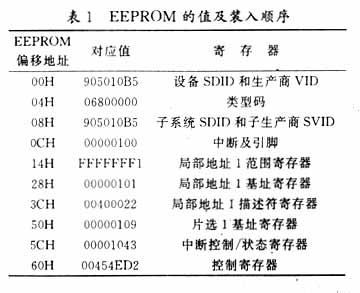

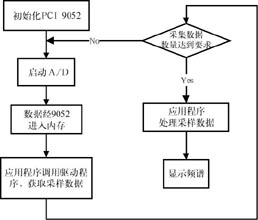

本文介紹了一種基于PCI總線的高速噪聲檢測(cè)系統(tǒng),介紹了采用PCI 9052作為PCI總線接口芯片的數(shù)據(jù)采集部分的設(shè)計(jì)原理,并說(shuō)明了數(shù)據(jù)采集卡的高速采樣和速率可變的實(shí)現(xiàn)原理,給出了底層硬件同上層軟件的連接實(shí)現(xiàn)。

2021-04-09 06:21:14

PCI總線的中斷機(jī)制PCI總線使用INTA#、INTB#、INTC#和INTD#信號(hào)向處理器發(fā)出中斷請(qǐng)求。這些中斷請(qǐng)求信號(hào)為低電平有效,并與處理器的中斷控制器連接。在PCI體系結(jié)構(gòu)中,這些...

2022-02-16 06:31:43

,通過(guò)XILINX 的FPGA 實(shí)現(xiàn)PLX9054 與1553 總線協(xié)議的 通信。當(dāng)計(jì)算機(jī)啟動(dòng)時(shí),9054 需要串行EEPROM 為其提供一些必要的配置信息以實(shí)現(xiàn)對(duì)PCI 配置寄存器和本地寄存器的設(shè)置

2019-05-21 05:00:22

PCI9030是什么?PCI9030主要有哪些特點(diǎn)?設(shè)計(jì)PCI總線接口有哪些步驟流程?

2021-04-15 06:57:46

;計(jì)算機(jī)對(duì)結(jié)果數(shù)據(jù)進(jìn)行分析處理、按一定的標(biāo)準(zhǔn)進(jìn)行判別,將測(cè)試結(jié)果進(jìn)行顯示、控制分選機(jī)對(duì)被測(cè)器件進(jìn)行分選。1 PCI總線及其接口的實(shí)現(xiàn)自動(dòng)化集成電路測(cè)試系統(tǒng)(ATE)的結(jié)構(gòu)圖如圖1所示。本設(shè)計(jì)的接口總線選用

2019-05-30 05:00:02

信息,并給每一設(shè)備分配系統(tǒng)資源,如中斷、I/O空間、存儲(chǔ)器空間等。在PCI系統(tǒng)結(jié)構(gòu)中,為每個(gè)PCI都提供了256個(gè)字節(jié)(至少是前64個(gè)字節(jié))的配置空間,這256個(gè)字節(jié)的配置空間中前64個(gè)字節(jié)稱為頭區(qū)域

2019-04-29 07:00:09

電路都由它們來(lái)實(shí)現(xiàn)。HS3282是由兩個(gè)接收器和一個(gè)發(fā)送器組成,接收器和發(fā)送器分別獨(dú)立工作。兩個(gè)獨(dú)立的接收器直接與ARINC429總線相連,當(dāng)接收到一個(gè)數(shù)據(jù)字后產(chǎn)生相應(yīng)的讀請(qǐng)求信號(hào),等待外部命令對(duì)數(shù)

2019-04-26 07:00:08

PCI總線漸漸地取代了ISA總線。它有許多優(yōu)點(diǎn),比如即插即用(Plug and Play)、中斷共享等。在這里我們對(duì)PCI總線做一個(gè)深入的介紹。 從數(shù)據(jù)寬度上看,PCI總線有32bit、64bi

2008-06-16 14:24:07 147

147 介紹 PCI 總線的特點(diǎn),對(duì)現(xiàn)有的 PCI 總線的接口設(shè)計(jì)方法進(jìn)行分析;介紹 PCI 接口芯片CY7C09449PV的結(jié)構(gòu)及其與數(shù)字信號(hào)處理器TMS320C32之間接口電路的設(shè)計(jì),提出一種基于PCI和 C32的數(shù)據(jù)

2009-04-08 09:53:42 26

26 基于PCI總線的高速數(shù)據(jù)采集卡系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn):本文介紹一種基于PCI總線的高速數(shù)據(jù)采集卡系統(tǒng)的設(shè)計(jì)方法,討論了設(shè)計(jì)高速數(shù)據(jù)采集系統(tǒng)的關(guān)鍵技術(shù),給出了系統(tǒng)整體設(shè)計(jì)方案和P

2009-06-22 19:04:54 44

44 基于FPGA的PCI總線接口設(shè)計(jì)::PCI是一種高性能的局部總線規(guī)范,可實(shí)現(xiàn)各種功能標(biāo)準(zhǔn)的PCI總線卡。本文簡(jiǎn)要介紹了PCI總線的特點(diǎn)、信號(hào)與命令,提出了一種利用高速FPGA實(shí)現(xiàn)PCI總線接

2009-06-25 08:17:18 48

48 PCI中斷機(jī)制分析:PCI 總線有四條中斷線,所有PCI 設(shè)備共同使用這四條線向系統(tǒng)申請(qǐng)中斷,中斷請(qǐng)求經(jīng)可編程中斷路由器路由到可編程中斷控制器的某條中斷請(qǐng)求輸入腳IRQi ,再由中斷控

2009-06-28 19:21:43 26

26 PCI 總線接口控制器的設(shè)計(jì)是基于PCI總線的應(yīng)用設(shè)計(jì)的關(guān)鍵所在。本文在介紹PCI9054接口控制器的基礎(chǔ)上,給出了一種通用的高速數(shù)據(jù)采集接口的設(shè)計(jì),并提出了一種新的包括PCI9054單

2009-07-30 15:33:13 18

18 本文在結(jié)合嵌入式實(shí)時(shí)操作系統(tǒng)VxWorks 和PCI總線的特點(diǎn)的基礎(chǔ)上,介紹了PCI總線驅(qū)動(dòng)設(shè)計(jì)的過(guò)程,并從充分應(yīng)用VxWorks 卓越的實(shí)時(shí)性和PCI總線靈活的擴(kuò)展性的角度出發(fā),給出了有一定

2009-08-10 09:02:36 24

24 本文簡(jiǎn)要介紹了PCI 總線的仲裁機(jī)制, 完成了PCI 總線仲裁器核心的設(shè)計(jì)、實(shí)現(xiàn)。通過(guò)ModelSim 進(jìn)行了軟件仿真,最后在XILINX 公司的FPGA 上加以了驗(yàn)證。

2009-09-03 08:18:29 27

27 本文在PCI2.2 總線規(guī)范的基礎(chǔ)上,給出了一種PCI 總線目標(biāo)控制器的設(shè)計(jì)方案。重點(diǎn)從控制邏輯和數(shù)據(jù)通路的建立上闡述了目標(biāo)控制器的設(shè)計(jì):用狀態(tài)機(jī)實(shí)現(xiàn)總線訪問(wèn)操作的復(fù)雜時(shí)

2009-12-12 16:58:25 33

33 本文重點(diǎn)分析了PCI 總線設(shè)備控制器的設(shè)計(jì)方案。以PCI 總線協(xié)議的分析和理解為基礎(chǔ),對(duì)PCI 總線設(shè)備控制器進(jìn)行了功能分析和結(jié)構(gòu)劃分,對(duì)PCI 總線從設(shè)備控制器的設(shè)計(jì)思路和各個(gè)

2010-01-13 16:57:37 49

49 PCI總線協(xié)議的FPGA實(shí)現(xiàn)及驅(qū)動(dòng)設(shè)計(jì)

摘要! 采用FPGA技術(shù)! 在公司的flex6000系列芯片上實(shí)現(xiàn)了從設(shè)備模式pci總線的簡(jiǎn)化協(xié)議!并給出了WIndowsx 系統(tǒng)下的虛擬設(shè)備驅(qū)動(dòng)程序

2010-03-12 14:30:27 36

36 摘 要: 本文采用Altera的CPLD實(shí)現(xiàn)了PCI總線至UTOPIA接口的邏輯轉(zhuǎn)換控制,為低成本實(shí)現(xiàn)ATM終端奠定了基礎(chǔ)。

2006-03-11 13:16:50 864

864

PCI總線原理

PCI總線的特點(diǎn):數(shù)據(jù)總線32位,可擴(kuò)充到64位。可進(jìn)行突發(fā)(burst)式傳輸。總線操作與處

2008-12-09 11:30:05 13510

13510

基于PCI總線的GP-IB接口電路設(shè)計(jì)

摘要:?主要介紹作為從設(shè)備如何根據(jù)PCI總線協(xié)議設(shè)計(jì)PCI總線接口電路,從而實(shí)現(xiàn)基于PCI總線的GP-IB接口電路設(shè)計(jì),重點(diǎn)闡述PCI總

2008-12-26 15:14:36 1168

1168

PCI總線定義

PCI 是 Peripheral Component Interconnect 的縮寫。接口卡的外觀:PCI 標(biāo)準(zhǔn) 32位/64位 接口卡

2009-02-12 10:37:58 1455

1455

PCI9052總線接口芯片及其ISA模式應(yīng)用

PCI9052是PLX公司開發(fā)的服從PCI協(xié)議的從模式接口芯片,它能夠實(shí)現(xiàn)ISA總線到PCI總線的平滑轉(zhuǎn)換。主要闡述了PCI9052

2009-05-04 21:48:45 1562

1562

文章介紹了一種基于PCI總線的高速噪聲檢測(cè)系統(tǒng),介紹了采用PCI 9052作為PCI總線接口芯片的數(shù)據(jù)采集部分的設(shè)計(jì)原理,并說(shuō)明了數(shù)據(jù)采集卡的高速采樣和速率可變的實(shí)現(xiàn)原理,給出了底層

2009-06-16 07:59:44 659

659

摘 要 :PCI是一種高性能的局部總線規(guī)范,可實(shí)現(xiàn)各種功能標(biāo)準(zhǔn)的PCI總線卡。本文簡(jiǎn)要介紹了PCI總線的特點(diǎn)、信號(hào)與命令,提出了一種利用高速FPGA實(shí)現(xiàn)PCI總線接口的

2009-06-20 13:13:28 936

936

摘 要: 以自行研制開發(fā)的PCI高速總線背板為背景,系統(tǒng)地論述了PCI總線的仲裁機(jī)制、總線的缺省占用、仲裁信號(hào)協(xié)定及優(yōu)先級(jí)仲裁算法,給出了采用EPLD實(shí)現(xiàn)仲裁器功能的編程設(shè)計(jì)

2009-06-20 13:32:20 961

961

基于PCI總線的CAN卡的設(shè)計(jì)與實(shí)現(xiàn)

現(xiàn)場(chǎng)總線CAN(Controller Area Network控制器局域網(wǎng)絡(luò))以其高性能、高可靠性及獨(dú)特的設(shè)計(jì),越來(lái)越受到人們的重視和青睞,

2009-10-25 10:54:58 816

816

PCI Express總線

其實(shí),PCI Express是一個(gè)計(jì)算機(jī)系統(tǒng)總線的名稱,不過(guò)大家聽得最多的還是“接口”這個(gè)詞,也沒錯(cuò),PCI Express的確是下一

2010-01-22 11:21:51 627

627 PCI總線目標(biāo)接口芯片PCI9052及其應(yīng)用

摘要:PCI9052是PLX公司繼PCI9050之后新推出的一種低成本的PCI總線目標(biāo)接口芯片,它傳輸速率高,數(shù)據(jù)吞吐量大,

2010-03-03 19:21:58 2492

2492

PCI總線的熱插拔技術(shù)及實(shí)現(xiàn)

摘要:具有熱插拔PCI槽現(xiàn)已成為許多需要長(zhǎng)時(shí)間不間斷工作和能夠在線維修的計(jì)算機(jī)系統(tǒng)的必備功能。文中介紹了

2010-03-03 19:27:08 1871

1871

PCI9054是PLX公司推出的一種PCI主模式橋芯片。本文主要介紹了它的特性、功能及應(yīng)用,說(shuō)明了以PCI9054作為接口芯片,開發(fā)PCI總線擴(kuò)展卡的硬件框架圖,最后給出一個(gè)簡(jiǎn)單的實(shí)例。

2011-05-14 18:10:44 95

95 本文介紹的DSP與PCI總線的接 接方案靈活簡(jiǎn)單,減小了布板的復(fù)雜度,簡(jiǎn)化了PCI總線要求的時(shí)序,縮短了開發(fā)周期。采用該方案設(shè)計(jì)的數(shù)據(jù)處理系統(tǒng)工作穩(wěn)定,已應(yīng)用在低頻信號(hào)檢測(cè)領(lǐng)域

2011-08-19 16:11:06 1660

1660

本文在詳細(xì)闡述處理板的整體結(jié)構(gòu)和DSP與PCI9656的接口電路設(shè)計(jì)原理的基礎(chǔ)上,提出一種ADSPTS201基于橋芯片PCI9656實(shí)現(xiàn)與CPCI總線通信的雷達(dá)信號(hào)處理板的設(shè)計(jì)方案,實(shí)現(xiàn)RocketIO到DSP數(shù)據(jù)的

2011-09-08 13:56:47 1970

1970

出了一種PCI總線從設(shè)備的CPLD實(shí)現(xiàn)方法。該方法遵從PCI規(guī)范2.2版,實(shí)現(xiàn)了資源自動(dòng)配置并且支持?jǐn)?shù)據(jù)突發(fā)傳輸。試驗(yàn)證明該方法的有效性,其突發(fā)傳輸速率可達(dá)20 MBs -1 。

2011-11-30 17:06:11 60

60 目前PCI是處于主流的計(jì)算機(jī)總線。以往的CAN卡一般都是基于ISA總線的,由于ISA總線傳輸速率低,CAN卡必須增加中繼控制功能,才能夠適應(yīng)CAN的高速傳輸,導(dǎo)致造價(jià)高、體積大、傳輸速率

2012-06-01 10:57:43 2053

2053

PCI總線的應(yīng)用資料

2017-10-31 09:10:56 9

9 PCIExpress總線是新一代的I/O局部總線標(biāo)準(zhǔn),是取代PCI總線的革命性總線架構(gòu)。PCI總線曾經(jīng)是PC體系結(jié)構(gòu)發(fā)展史上的一個(gè)里程碑,但是隨著技術(shù)的不斷發(fā)展,新涌現(xiàn)出的一些外部設(shè)備對(duì)傳輸速度和帶寬有更高的要求,PCI設(shè)計(jì)之初并沒有考慮這些因素,因此并不能完全滿足這些外部設(shè)備的需求。

2018-04-11 16:00:00 6913

6913

在一些嵌入式處理器系統(tǒng)中,這個(gè)問(wèn)題較易解決。因?yàn)榍度胧教幚砥飨到y(tǒng)很清楚在當(dāng)前系統(tǒng)中存在多少個(gè)PCI設(shè)備,這些PCI設(shè)備使用了哪些中斷資源。在多數(shù)嵌入式處理器系統(tǒng)中,PCI設(shè)備的數(shù)量小于中斷控制器提供的外部中斷請(qǐng)求引腳數(shù),而且在嵌入式系統(tǒng)中,多數(shù)PCI設(shè)備僅使用INTA#信號(hào)提交中斷請(qǐng)求。

2018-04-11 09:12:35 6186

6186 PCI總線是一種樹型結(jié)構(gòu),并且獨(dú)立于CPU總線,可以和CPU總線并行操作。PCI總線上可以掛接PCI設(shè)備和PCI橋片,PCI總線上只允許有一個(gè)PCI主設(shè)備,其他的均為PCI 從設(shè)備,而且讀寫操作只能在主從設(shè)備之間進(jìn)行,從設(shè)備之間的數(shù)據(jù)交換需要通過(guò)主設(shè)備中轉(zhuǎn)。

2018-06-07 15:02:00 3581

3581

上面的例子主要是基于早期的單核CPU設(shè)計(jì)的,并沒有考慮到目前多核CPU的情況。因此,在后續(xù)的PCI Spec中,將PIC替換為IO APIC(Advanced Programmed Interrupt Controller)。

2018-08-24 09:58:11 9180

9180 從開始到現(xiàn)在,與PCI總線已經(jīng)相處很長(zhǎng)一段時(shí)間了,以前從來(lái)沒有認(rèn)真的去分析一下它的掃描過(guò)程,只知道這個(gè)流程是標(biāo)準(zhǔn)的規(guī)范的,今天趁自己的時(shí)間比較充足,那就在這里好好的總結(jié)一下,本人認(rèn)定決定以及肯定

2019-06-27 16:56:00 6

6 CH365 是一個(gè)連接PCI總線的通用接口芯片,支持I/O端口映射、存儲(chǔ)器映射、擴(kuò)展ROM 以及中斷。

2019-11-04 14:36:14 1940

1940

系統(tǒng)中ADC板卡,DSP板卡以及其他 功能模塊之間的數(shù)據(jù)傳輸和控制通道,ADC板卡采集到的數(shù)據(jù)通過(guò)PCI總線主控模式高速傳輸?shù)紻SP板卡中進(jìn)行數(shù)字信號(hào)處理,實(shí)現(xiàn)接收機(jī)功能。結(jié)果表明, 該系統(tǒng)具有結(jié)構(gòu)簡(jiǎn)單,精度高等優(yōu)點(diǎn),并充分體現(xiàn)軟件無(wú)線電的靈

2020-11-19 17:48:01 13

13 是實(shí)現(xiàn)電流盡可能小的系統(tǒng),功耗低。軟件透明,在和PCI設(shè)備之間通信時(shí),軟件驅(qū)動(dòng)之間使用相同的命令集和狀態(tài)定義。隨著嵌入式計(jì)算機(jī)的發(fā)展,PCI總線也越來(lái)越多地被引入到嵌入式系統(tǒng)中。本文介紹在“十五”預(yù)研項(xiàng)目中實(shí)現(xiàn)嵌入式PCI總線的一些經(jīng)驗(yàn)體會(huì),與大家切磋。

2021-03-26 10:31:30 3387

3387

PCI總線使用INTA#、INTB#、INTC#和INTD#信號(hào)向處理器發(fā)出中斷請(qǐng)求。

2021-06-21 16:10:13 1581

1581 PCI總線的信號(hào)定義 PCI總線是一條共享總線,在一條PCI總線上可以掛接多個(gè)PCI設(shè)備。這些PCI設(shè)備通過(guò)一系列信號(hào)與PCI總線相連,這些信號(hào)由地址/數(shù)據(jù)信號(hào)、控制信號(hào)、仲裁信號(hào)、中斷信號(hào)等多種

2021-07-18 09:55:32 1981

1981 PCI總線的存儲(chǔ)器讀寫總線事務(wù) 總線的基本任務(wù)是實(shí)現(xiàn)數(shù)據(jù)傳送,將一組數(shù)據(jù)從一個(gè)設(shè)備傳送到另一個(gè)設(shè)備,當(dāng)然總線也可以將一個(gè)設(shè)備的數(shù)據(jù)廣播到多個(gè)設(shè)備。在處理器系統(tǒng)中,這些數(shù)據(jù)傳送都要依賴一定的規(guī)則

2021-07-18 10:06:12 2274

2274 PCI總線的中斷機(jī)制 PCI總線使用INTA#、INTB#、INTC#和INTD#信號(hào)向處理器發(fā)出中斷請(qǐng)求。這些中斷請(qǐng)求信號(hào)為低電平有效,并與處理器的中斷控制器連接。在PCI體系結(jié)構(gòu)中,這些中斷信號(hào)

2021-07-18 10:10:40 2450

2450 MSI和MSI-X中斷機(jī)制 在PCI總線中,所有需要提交中斷請(qǐng)求的設(shè)備,必須能夠通過(guò)INTx引腳提交中斷請(qǐng)求,而MSI機(jī)制是一個(gè)可選機(jī)制。而在PCIe總線中,PCIe設(shè)備必須支持MSI或者M(jìn)SI-X

2021-08-10 17:54:51 5219

5219 PCI總線的信號(hào)定義PCI總線是一條共享總線,在一條PCI總線上可以掛接多個(gè)PCI設(shè)備。這些PCI設(shè)備通過(guò)一系列信號(hào)與PCI總線相連,這些信號(hào)由地址/數(shù)據(jù)信號(hào)、控制信號(hào)、仲裁信號(hào)、中斷信號(hào)...

2021-12-17 18:26:06 3

3 PCI總線協(xié)議非常復(fù)雜,目前實(shí)現(xiàn)PCI接口的有效方案分為兩種:即使用可編程邏輯器件和使用專用總線接口的器件,可編程邏輯器件實(shí)現(xiàn)PCI接口比較靈活,可以利用的器件比較多,現(xiàn)在有許多生產(chǎn)可編程邏輯器件的廠商(如Xilinx的Logicore和Alerra的AMPP)都提供經(jīng)過(guò)嚴(yán)格測(cè)試的PCI接口功能模塊

2023-08-01 14:37:19 553

553 怎樣把PCI總線速度鎖定? PCI總線速度鎖定是指限制PCI總線傳輸速度的方法。當(dāng)系統(tǒng)中出現(xiàn)某些硬件兼容性問(wèn)題或者不穩(wěn)定性問(wèn)題時(shí),鎖定PCI總線速度可能是一個(gè)有效的解決方案。在本文中,我們將詳細(xì)介紹

2023-09-02 15:12:39 1194

1194 在PCI總線中,所有需要提交中斷請(qǐng)求的設(shè)備,必須能通過(guò)INTx引腳提交中斷請(qǐng)求,MSI機(jī)制是一個(gè)可選機(jī)制。而PCIE總線中,PCIE設(shè)備必須支持MSI或MSI-X中斷請(qǐng)求機(jī)制,而可以不支持INTx中斷消息。

2024-01-12 14:54:36 480

480

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論