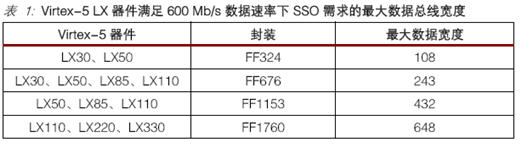

本白皮書討論各種存儲器接口控制器設計所面臨的挑戰和 Xilinx 的解決方案,同時也說明如何使用 Xilinx軟件工具和經過硬件驗證的參考設計來為您自己的應用(從低成本的 DDR SD

2010-08-18 10:50:37 3238

3238

:視頻處理器框圖FPGA獲取并緩存四個視頻源的數據流。這些FIFO緩沖器由DDR3存儲器控制器清空并保存在DDR3存儲器中。一旦一個完整的視頻數據包存儲完畢,視頻處理器會向DDR3存儲器控制器申請數據

2019-05-24 05:00:34

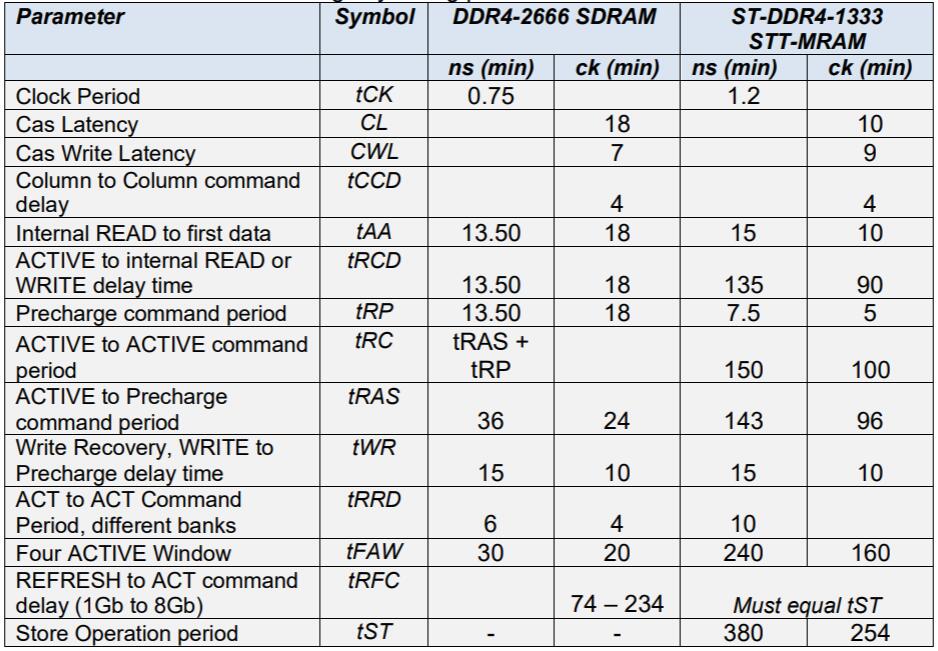

Everspin Technologies總部位于亞利桑那州錢德勒,主要是設計和制造MRAM、STT-MRAM的全球領導者,Everspin所生產的MRAM產品包括40nm,28nm及更高工藝在內

2020-08-31 13:59:46

請教大家,我打算使用這個方案,FPGA使用控制器硬核,外面掛兩個16位DDR,這兩個DDR的的差分時鐘、地址線、控制線等共用,只有數據線使用各自的。希望做到兩片同時訪問,一次把32位數據分成兩個16

2016-04-26 13:41:00

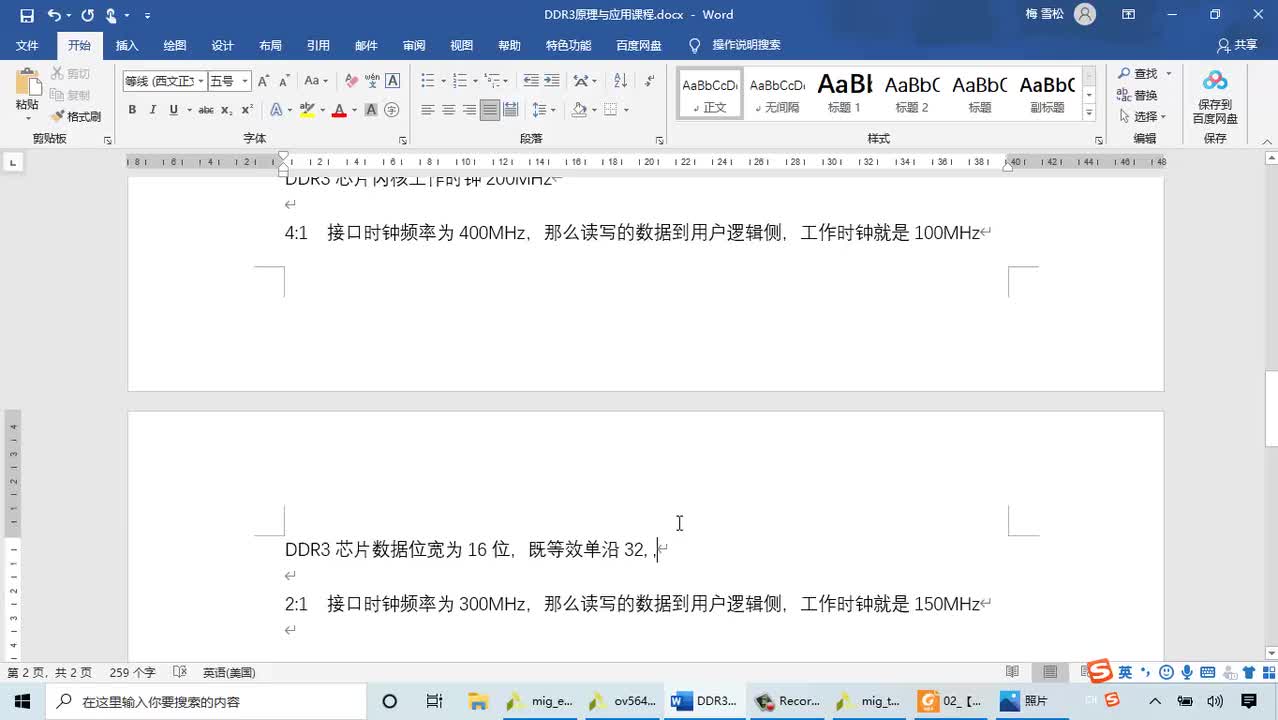

DDR3的理論帶寬怎么計算?用xilinx的控制器輸入時鐘200M。fpga與DDR的接口如下:

2016-02-17 18:17:40

XILINX 關于FPGA 對DDR SDRAM 的設計文檔

2012-08-17 09:20:26

Pinout文件,我們可以靈活選擇。圖2、FPGA Pinout下載鏈接圖3、Xilinx官網下載Pinout我們打開一個.TXT形式的Pinout,如圖4所示。可以看到,文件分為8列,包含所有設計原理圖

2021-05-28 09:23:25

Achieving High Performance DDR3 Data Rates in Virtex-7 and Kintex-7 FPGAs。Xilinx官方DDR3資料。

2016-05-27 16:39:58

的JEDEC標準DDR4接口的變體,它包含了對完整系統支持所需的獨特功能。本文將幫助工程師了解Xilinx FPGA控制器的Everspin STT-DDR4設計指南

2021-01-15 06:08:20

破解Lesson05 特權Xilinx FPGA SF-SP6入門指南 -- 文本編輯器notepad++安裝Lesson06 特權Xilinx FPGA SF-SP6入門指南 -- ISE中使

2015-07-22 11:49:20

你好任何人都可以指導我,Xilinx ISE中的DDR控制器是否有任何IP實現。如果沒有如何實現DDR控制器以上來自于谷歌翻譯以下為原文Hi can any one guide me

2019-02-27 12:13:51

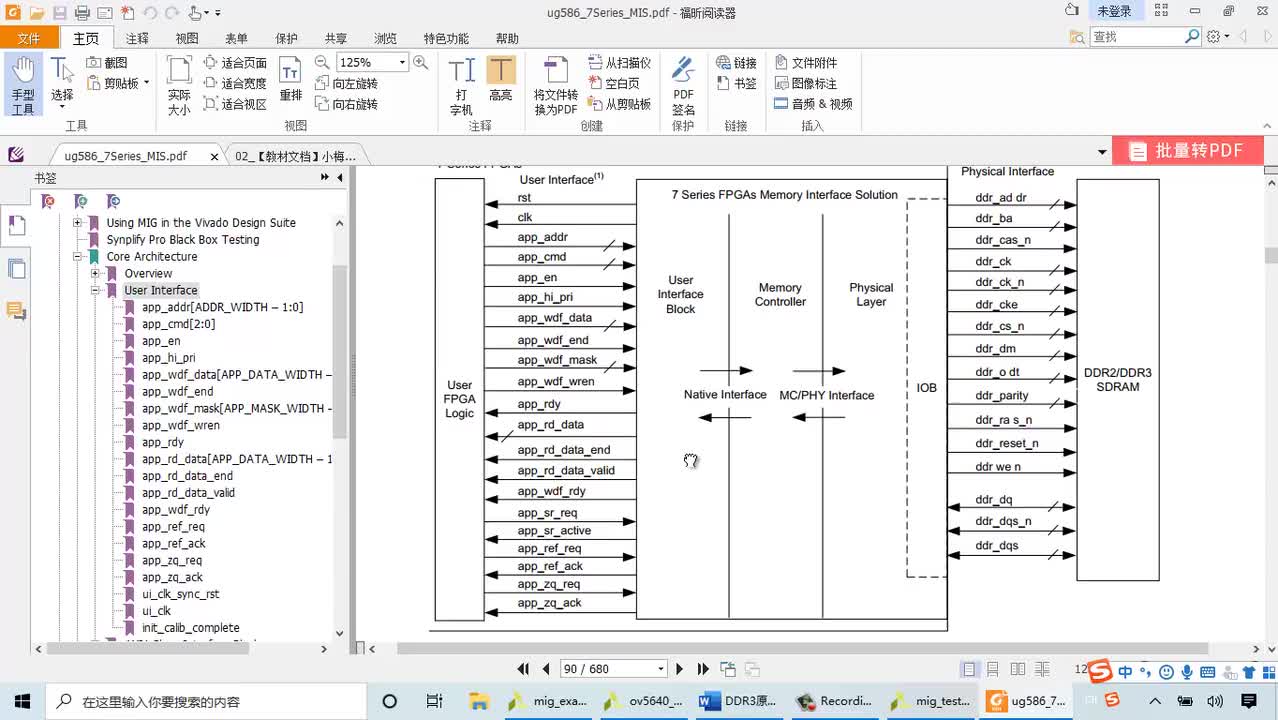

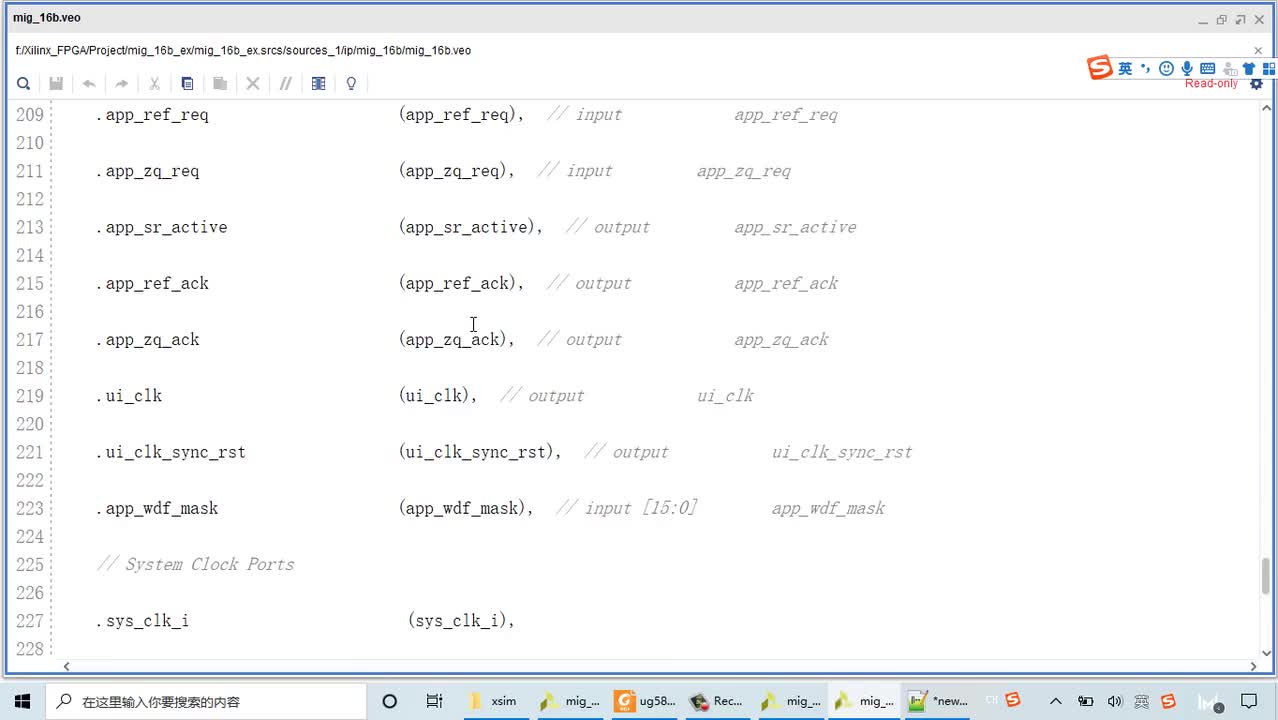

MIG IP控制器是Xilinx為用戶提供的一個用于DDR控制的IP核,方便用戶在即使不了解DDR的控制和讀寫時序的情況下,也能通過MIG IP控制器讀寫DDR存儲器。一、新建工程在Vivado環境

2019-12-19 14:36:01

xilinx公司的7系列FPGA應用指南

2012-08-14 12:17:40

實現特權同學的例程 特權FPGA VIP視頻圖像開發套件例程詳解2——DDR2控制器讀寫測試 時,進行IP核配置時,進入下一步配置參數時,變成黑屏重裝軟件也不行

2018-01-24 08:23:17

。2.5 LBS狀態機工作流程FPGA作為LBS的邏輯控制器,負責協調好與DDR_FIFO數據和PEX8311之間的時序關系。系統接收數據時,首先由驅動程序向PEX8311發 送復位信號,通過

2015-01-29 14:09:17

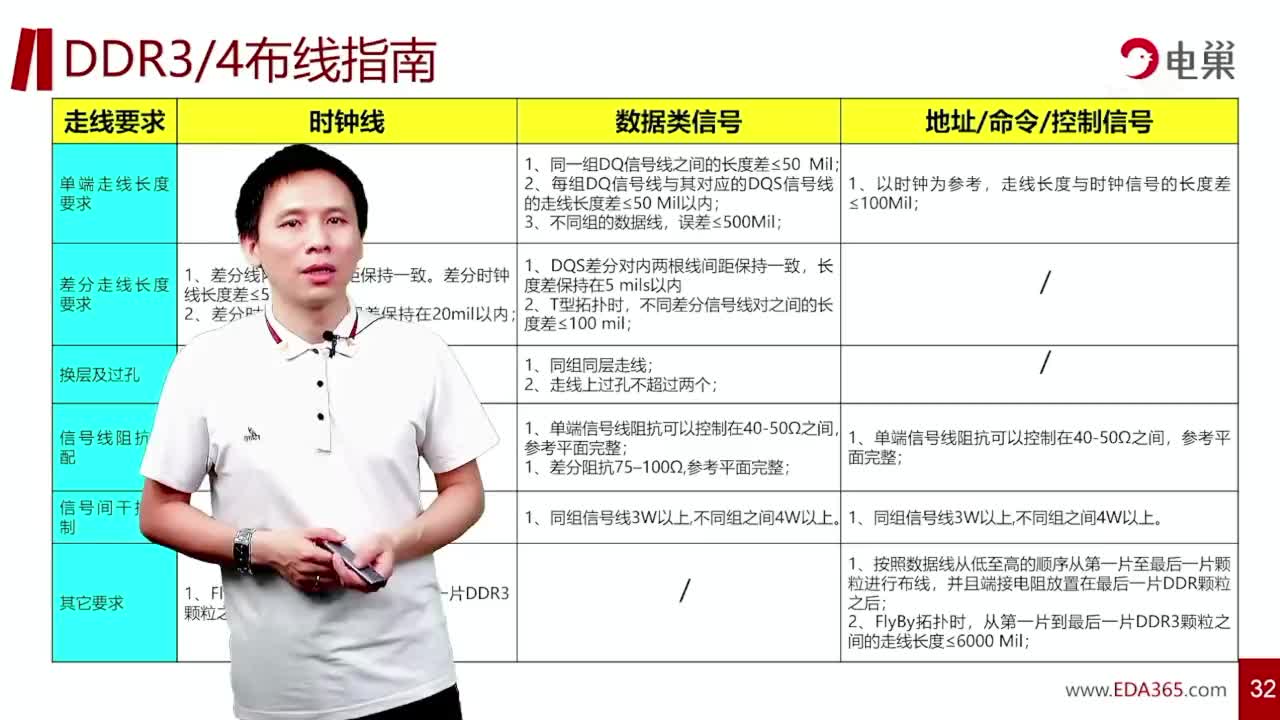

【PCB多層板設計挑戰賽】+FPGA控制器應用領域:基于FPGA的低速輔助駕駛控制器挑戰點:為了保證FPGA的高速接口(DDR4/MIPI/DP/USB)的SI并降低EMC,采用多層GND進行信號

2022-11-09 17:35:05

本文和設計代碼由FPGA愛好者小梅哥編寫,未經作者許可,本文僅允許網絡論壇復制轉載,且轉載時請標明原作者。Altera DDR2控制器使用IP的方式實現,一般很少自己寫控制器代碼。ddr

2020-02-25 18:33:00

`例說FPGA連載36:DDR控制器集成與讀寫測試之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 本實例對Altera提供

2016-10-08 17:05:55

`例說FPGA連載41:DDR控制器集成與讀寫測試之DDR2 IP核接口描述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 如圖

2016-10-27 16:36:58

SATA主機控制器SATA Host控制器SATA Host Controller基于FPGA的SATA主機控制器基于FPGA的SATA Host控制器本人在北京工作7年以上,非常

2015-11-11 15:06:39

我可以使用mig生成ddr控制器(xc6vlx130t)嗎?mig向導只支持ddr2和ddr3!

2020-06-12 07:32:48

如圖7所示。圖7 DDR3讀寫狀態機為確保設計的可行性及可靠性,對編寫的DDR3讀寫控制器進行板級驗證,硬件測試中選用Xilinx公司的Kintex-7 FPGA以及Micron公司的DDR

2018-08-02 09:34:58

基于Xilinx FPGA的DDR2 SDRAM存儲器接口

2012-08-20 18:55:15

DDR3存儲器控制器面臨的挑戰有哪些?如何用一個特定的FPGA系列LatticeECP3實現DDR3存儲器控制器。

2021-04-30 07:26:55

你好使用Xilinx的任何一個端口MIG DDR2 SDRAM控制器都是我遇到了問題我有vhdl頂級系統,其中我實例化ddr2控制器我的ddr2包裝器與testcase一起工作正常(由MIG提供

2019-08-19 10:47:06

嗨,我們從xilnx購買了ML555板。我們想驗證該板上的ddr2控制器。我們已經加載了CD中提供的ddr2控制器的位圖文件。我們沒有觀察到為閱讀文件中提到的比較邏輯有效的數據提供的任何LED切換。如用戶指南中所述,正確生成時鐘。讓我們知道這種行為的原因。問候--sampath

2019-08-19 09:35:52

你好如何在不使用DDR內存控制器的情況下設計FPGA BRAM(或任何其他內存模塊_SD,DDR以外的本地等)大容量存儲單元?當我通過示例設計“VC707_bist”替換DRAM控制器和BRAM

2019-04-04 15:10:55

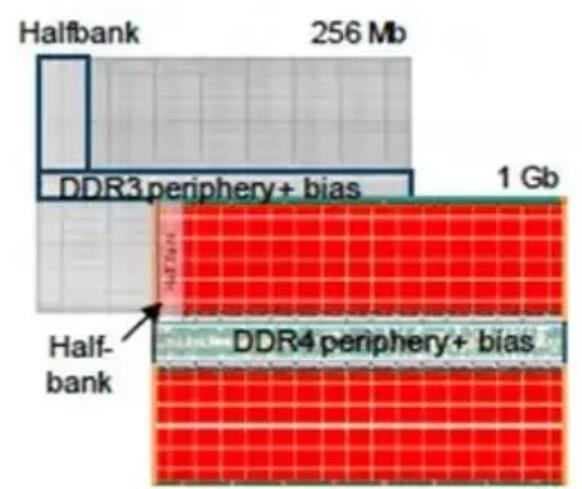

的工作時鐘頻率。然而,設計至DDR3的接口也變得更具挑戰性。在FPGA中實現高速、高效率的DDR3控制器是一項艱巨的任務。直到最近,只有少數高端(昂貴)的FPGA有支持與高速的DDR3存儲器可靠接口的塊

2019-08-09 07:42:01

Xilinx DDR 控制器。 DDR PHY 與電路板調試: Zynq UltraScale+ MPSoC VCU DDR 控制器采用 MIG PHY。 這意味著您可以使用標準 MIG 示例設計來驗證您

2021-01-07 16:02:09

如何調試 Zynq UltraScale+ MPSoC VCU DDR 控制器?

2021-01-22 06:29:21

大家好,我想設計自己的DDR控制器并在FPGA上驗證它。我將在verilog中實現我剛開始閱讀JESDC79C DDR規格..但我很困惑如何編寫那些初始化序列?請建議如何處理這個設計DDR控制器

2019-04-29 11:59:22

嗨,我即將使用Virtex-4QV設備(XQR4VFX140)開始一個新項目。雖然我對使用DDR2 / DDR3 SDRAM的Xilinx MIG有一些經驗,但我發現MIG IP不支持VIRTEX-4QV器件。那可能是另類?如何將DDR2 SDRAM與此FPGA連接?彌敦道

2020-04-02 06:08:46

目前有一個項目需要使用DDR3作為顯示緩存,VGA作為顯示器,FPGA作為主控器,來刷圖片到VGA上。VGA部分已經完成,唯獨這個DDR3以前沒有使用過,時序又比較復雜,所以短時間內難以完成,希望做過DDR3控制器的大神指點一二。急求!!!!

2015-11-16 09:18:59

DDR SDRAM在嵌入式系統中有哪些應用?DDR SDRAM的工作方式有哪幾種?怎樣去設計DDR SDRAM控制器?

2021-04-30 07:04:04

FPGA與DDR2存儲器接口DDR2控制器的設計原理是什么?DDR2控制器的應用有哪些?

2021-04-30 06:28:13

的內存控制器的設計與應用.pdf基于Spartan-3+FPGA的DDR2+SDRAM存儲器接口設計.pdf一種采用FPGA設計的SDRAM控制器.pdf用Xilinx+FPGA實現DDR+SDRAM控制器.pdf

2012-07-28 14:40:53

適用于Xilinx Virtex-7 FPGA開發板的32位DDR4 SDRAM

2020-12-30 07:39:14

你好我在Xilinx Spartan3E啟動板上為舊的基于Z80的計算機開始了我自己的項目。但我已經凍結了DDR內存控制器。我可以使用任何DDR參考設計嗎?我需要8位數據路徑,就緒/忙碌信號表示

2019-05-15 07:15:33

Virtex-4 FPGA應用指南

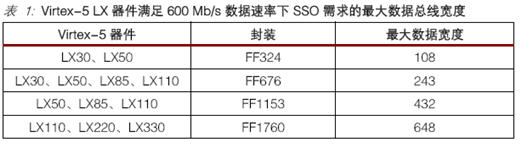

使用Virtex-4器件的DDR2控制器(267MHz及以上)

DDR2SDRAM器件提供了比DDRSDRAM指標所要求的更好的新功能,并允許DDR2器件以666Mb/s的數據

2010-05-13 14:14:26 39

39 用中檔FPGA實現高速DDR3存儲器控制器

引言

由于系統帶寬不斷的增加,因此針對更高的速度和性能,設計人員對存儲技術進行了優化。下一代雙數據速率(D

2010-01-27 11:25:19 879

879

本文是關于 xilinx公司的7系列FPGA應用指南。xilinx公司的7系列FPGA包括3個子系列,Artix-7、 Kintex-7和Virtex-7。本資料就是對這3各系列芯片的介紹。 下表是xilinx公司的7系列FPGA芯片容量對比表

2012-08-07 17:22:55 201

201 使用功能強大的FPGA來實現一種DDR2 SDRAM存儲器的用戶接口。該用戶接口是基于XILINX公司出產的DDR2 SDRAM的存儲控制器,由于該公司出產的這種存儲控制器具有很高的效率,使用也很廣泛,

2013-01-08 18:15:50 237

237 基于Xilinx的DDR2 SDRAM存儲控制器的用戶接口設計與仿真,本設計通過采用多路高速率數據讀寫操作仿真驗證,可知其完全可以滿足時序要求,由綜合結果可知其使用邏輯資源很少,運行速

2013-01-10 14:12:45 2990

2990 用FPGA設計DDR2控制器講解DDR2時序原理用戶接口設計幫助用戶快速掌握DDR2的控制技術新手上路的非常有幫助的資料。

2015-11-10 10:54:14 3

3 Xilinx FPGA工程例子源碼:DDR SDRAM控制器參考設計VHDL代碼

2016-06-07 11:44:14 19

19 Xilinx FPGA工程例子源碼:DDR SDRAM控制器verilog代碼

2016-06-07 14:13:43 38

38 Xilinx FPGA工程例子源碼:FPGA實現CAN總線控制器源碼

2016-06-07 14:13:43 87

87 Xilinx FPGA工程例子源碼:USB接口控制器參考設計VHDL代碼(Xilinx)

2016-06-07 14:54:57 21

21 Xilinx-ISE9.x-FPGA-CPLD設計指南合集

2022-03-22 18:03:09 76

76 Xilinx FPGA工程例子源碼:Xilinx DDR3最新VHDL代碼(通過調試)

2016-06-07 14:54:57 77

77 Xilinx FPGA工程例子源碼:Xilinx DDR2存儲器接口調試代碼

2016-06-07 14:54:57 27

27 Xilinx FPGA工程例子源碼:Xilinx 的用于設計SMBus控制器的源程序

2016-06-07 15:07:45 14

14 Xilinx FPGA工程例子源碼:基于XILINX的XC3系列FPGA的VGA控制器的VHDL源程序

2016-06-07 15:07:45 12

12 基于協議控制器的DDR3訪存控制器的設計及優化_陳勝剛

2017-01-07 19:00:39 15

15 DDR2SDRAM控制器IP功能測試與FPGA驗證_陳平

2017-01-07 21:45:57 3

3 ? 和 ?Xilinx Ehab Mohsen? 聊到了將 ?DDR4? 與 ?Xilinx UltraScale? FPGA? 相結合可實現的驚人性能優勢和功能。 立即觀看在線座談 ??

2017-02-09 06:18:33 470

470 控制器用戶接口設計方案。該控制器用戶接口已經在Xilinx 公司的VC707 開發板上通過了功能驗證,并成功的被應用到高速圖像數據采集系統中。

2017-11-17 14:14:02 3290

3290

提出一種便于用戶操作并能快速運用到產品的DDR2控制器IP核的FPGA實現,使用戶不需要了解DDR2的原理和操作方式的情況下,依然可以通過IP核控制DDR2。簡單介紹了DDR2的特點和操作

2017-11-22 07:20:50 4687

4687

使用中速Kintex-7 325T FPGA演示DDR3控制器和接口,運行速度高于1866 Mbps數據速率。

2018-11-30 06:21:00 5276

5276

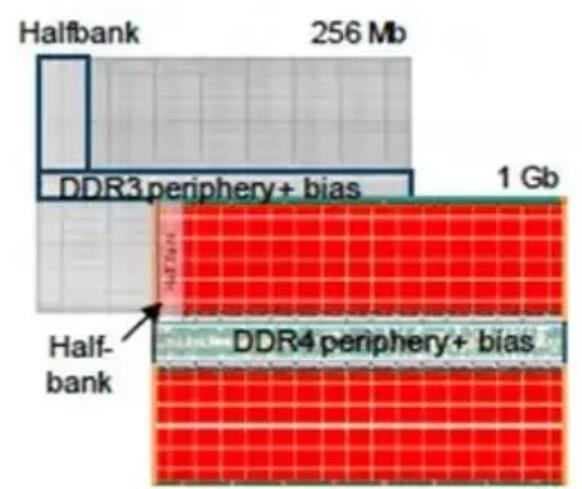

Everspin 近日宣布,其已開始試生產最新的 1Gb STT-MRAM(自旋轉移力矩磁阻)非易失性隨機存取器。

2019-06-27 08:59:43 9837

9837 GlobalFoundries、Everspin聯合宣布,雙方已經達成新的合作,將利用GF 12LP(12nm FinFET)工藝來制造新一代STT-MRAM(自旋轉移矩磁阻內存),包括獨立的MRAM芯片和嵌入式的eMRAM。

2020-03-16 08:42:26 497

497 MRAM和STT MRAM。STT MRAM需要控制器啟用或FPGA,該公司也一直在通過其伙伴關系發展其生態系統。 Everspin的幾個合作

2020-03-23 15:32:08 646

646 )STT-MRAM位單元的開發方面處于市場領先地位。 Toggle MRAM為許多行業提供服務,包括交通運輸,航空航天和醫療,物聯網及工業。Everspin與全球能源管理和自動化專家Schneider

2020-04-09 09:28:05 680

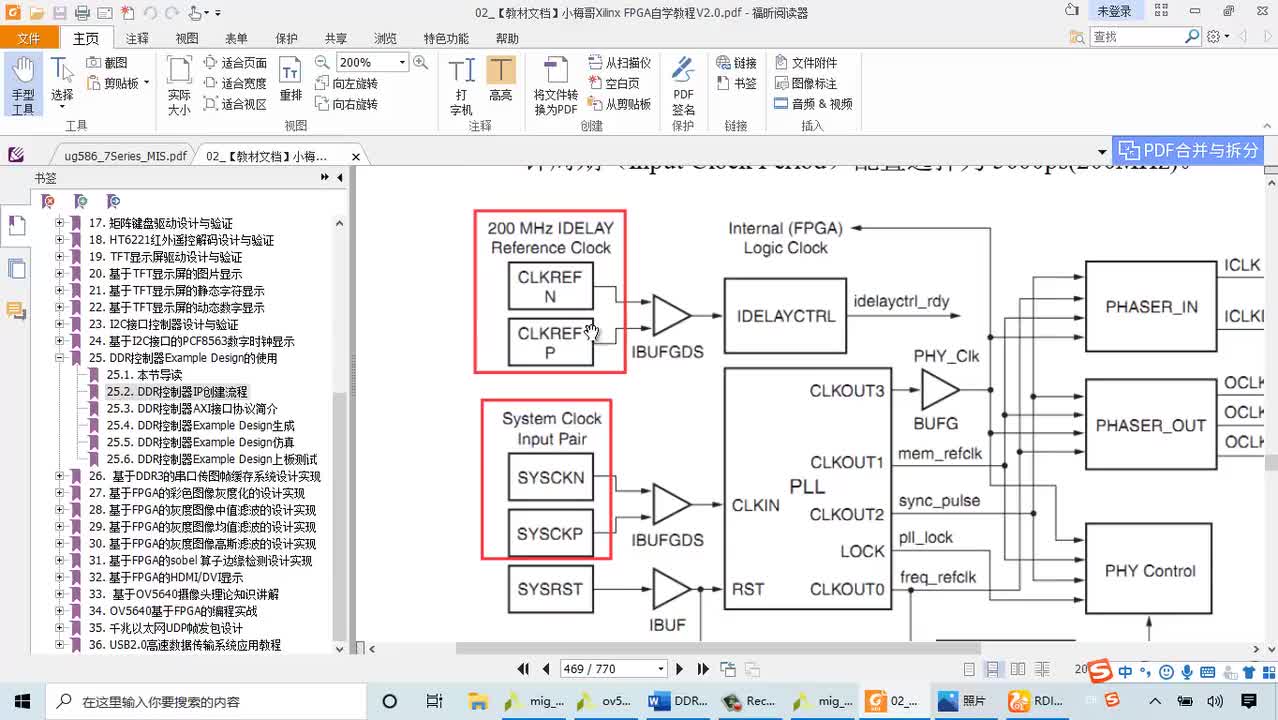

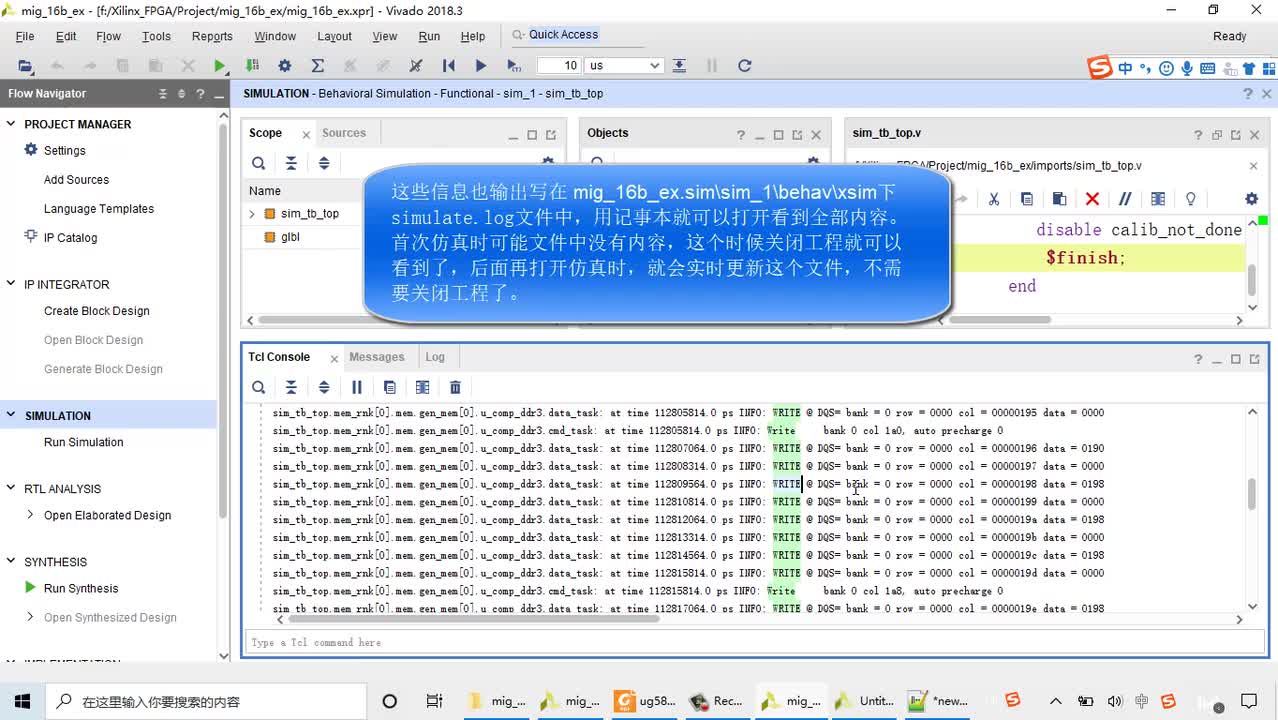

680 DDR對于做項目來說,是必不可少的。一般用于數據緩存和平滑帶寬。今天介紹下Xilinx DDR控制器MIG IP核的例化及仿真。 FPGA芯片:XC7K325T(KC705) 開發工具:Vivado

2020-11-26 15:02:11 7386

7386

UltraScale+ MPSoC VCU(H.264/H.265 視頻編解碼器)連用。

因此,調試將不同于 MIG 等傳統 Xilinx DDR 控制器。

DDR PHY 與電路板調試:

Zynq UltraScale...

2021-02-23 06:00:10 15

15 本應用指南描述了在 Virtex?-4 XC4VLX25 FF668 -10C 器件中實現的 DDR SDRAM 控制器。該實現運用了直接時鐘控制技術來實現數據采集,并采用自動校準電路來調整數據線上的延遲。

2021-03-26 14:42:41 4

4 Xilinx FPGA的監控器件補充部件指南

2021-04-27 19:28:56 5

5 基于FPGA的DDR3SDRAM控制器設計及實現簡介(arm嵌入式開發平臺PB)-該文檔為基于FPGA的DDR3SDRAM控制器設計及實現簡介資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-30 09:05:51 7

7 基于FPGA的DDR3SDRAM控制器設計及實現(嵌入式開發式入門)-該文檔為基于FPGA的DDR3SDRAM控制器設計及實現總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 13:07:09 35

35 ,以及對應的波形圖和 Verilog HDL 實現。我們調取的 DDR3 SDRAM 控制器給用戶端預留了接口,我們可以通過這些預留的接口總線實現對該 IP 核的控制,本章節將會講解如何根據 Xilinx 官方提供的技術參數來實現對 IP 核的寫控制。寫命令和寫數據總線介紹DDR3 SDRAM控制器I

2021-12-04 19:21:05 4

4 Everspin Technologies,Inc是設計制造MRAM和STT-MRAM的全球領導者其市場和應用領域涉及數據持久性和完整性,低延遲和安全性至關重要。E...

2022-01-25 19:29:14 3

3 Everspin是設計制造MRAM、STT-MRAM的翹楚,其市場和應用涉及數據持久性和完整性,低延遲和安全性至關重要。在磁存儲器設計,制造和交付...

2022-01-26 18:14:01 9

9 干貨來了,用DDR搬磚,只需要會用IP就好,Xilinx官方YYDS!

2022-02-21 18:15:32 6873

6873

everspin在磁存儲器設計,制造和交付給相關應用方面的知識和經驗在半導體行業中是獨一無二的。Everspin擁有超過600項有效專利和申請的知識產權組合,在平面內和垂直磁隧道結(MTJ)STT-MRAM位單元的開發方面處于市場領先地位。

2022-11-17 14:23:28 2461

2461

本文介紹一個FPGA開源項目:DDR3讀寫。該工程基于MIG控制器IP核對FPGA DDR3實現讀寫操作。

2023-09-01 16:23:19 743

743

電子發燒友網站提供《面向Xilinx FPGA和SoC的超快設計方法指南.pdf》資料免費下載

2023-09-14 10:02:31 1

1 電子發燒友網站提供《Xilinx FPGA和SoC的超高速設計方法指南.pdf》資料免費下載

2023-09-14 09:41:06 0

0 16層官方Xilinx Kintex UltraScale FPGA KCU105 4片DDR4分享下載

2021-10-11 14:24:57 63

63

電子發燒友App

電子發燒友App

評論