1、stm32存儲器映射概述

如果說時鐘是單片機的心臟,那么存儲器映射就像是單片機的神經網絡,傳輸大腦中樞(cpu)到各個外設的神經信號。由此可知,這塊的知識點在整個單片機知識體系架構里面,也是非常重要的。

可能有一部分人會覺得,現在我們都是基于標準庫、HALL庫,甚至LL庫來進行開發,所有的資源都是函數庫封裝好的,直接調用非常方便。對于這些底層的東西,我們沒有必要還像學習51單片機那樣,來研究它了。

然而我想說,事實并不是這樣的。對于一些比較簡單的項目,功能比較單一,代碼量不大項目,沒什么問題。甚至一些沒有用到特別復雜外設的工作量稍大的項目,也問題不大。一般常規的問題類似于我這篇文章所寫的內容 :【基礎知識】單片機編程注意事項及易錯點總結。大部分的bug都能夠得到解決。但是如果對于更大的項目,功能更復雜,外設更多。還需要注意代碼的模塊化,可移植性。這樣各個層級的文件會增加,全局變量、局部變量的使用都會大大增加。這個時候代碼的復雜度就會成倍增加。這個時候,往往就更需要我們知道單片機的內部是怎么工作的。

那么對于存儲器映射的學習,是我們了解單片機內部工作的開始。后面我們還會總結分析下stm32的啟動文件,map文件等等。這些知識點,也是技術能力邁向更高水平必須要學習理解的。也有人說,掌握了單片機的存儲器映射,就掌握了這款單片機40%的知識點,這塊知識點的重要性可見一斑

2、什么是存儲器映射

存儲器本身不具備地址,所以把芯片內核所預先設定好的地址分配給寄存器,就是存儲器映射。因為stm32的地址線是32位,也就是2的32次方,正好是對應4G的虛擬存儲空間。把內核廠商(也就是ARM公司)定義的這個虛擬空間與芯片廠商(這里是ST)芯片內部外設進行對應,也就是給存儲器分配地址,即存儲器映射。4個G的地址這么大,用不完沒關系,可以保留。

3、stm32f4存儲器映射分析

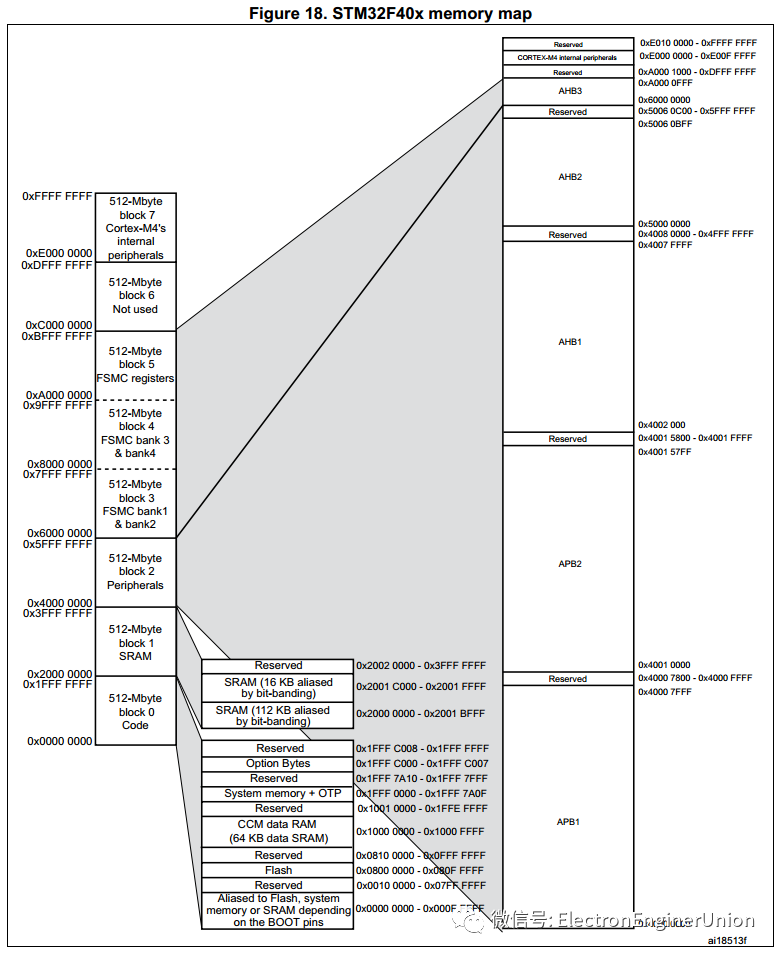

下圖是stm32f40x 的映射block diagram

cortex-M4內核如cortex-m3內核一樣,都是把4G空間分成block 0 ~ block7 共 8個塊,每塊大小為512M,并指出各個block是怎么分配的。下面我們就詳細闡述一下。

Block 0代碼區

Aliased to flash ,system memory or SRAM depending on the Boot pins

開始運行,BOOT1、BOOT0這兩個引腳的電平值選擇0X0000 0000--0X001F FFFF映射到不同的存儲器上,通過BOOT引腳選擇啟動模式。篇幅所限,關于BOOT1、BOOT0的引腳設置選擇不同的啟動方式,這里就不詳細展開了。

主Flash:用于保存數據的區域,每個芯片都有一個參數Flash空間大小,指的就是這部分。

CCM data RAM:Code區域是用I-Code和D-Code訪問,作用是為了加快數據處理速度。

system memory :STM32在出廠時,已經固化了一段程序在System memory(medium-density devices的地址為:0x1FFF_F000,大小為2KB)存儲器中。這段程序就是一個固定好的,并且沒法修改的Boot Loader

Options Bytes :可以按照用戶的需要進行配置(如配置看門狗為硬件實現還是軟件實現);

PS:存儲器的重映射

通常系統啟動都是從0地址處開始,但是為了支持不同的存儲介質,不同的存儲介質被分配了一個非0地址區域。這就是為什么要進行重映射。

因此重映射主要發生在兩種情況下,一是系統啟動的過程中;二是如果中途遇到需要在不同的存儲器之間進行切換的時候也需要進行重映射

我們一般的單片機自舉(啟動)單片機地址,都是從0開始運行的,STM32啟動需要重映射地址,F4xx的0X0000 0000~0x001F FFFF地址映射了到什么存儲器上,那么就從該存儲器上讀取指令。

Block 1

SRAM運行時臨時存放代碼的地方。不同類型的STM32單片機的SRAM大小是不一樣的,但是他們的起始地址都是0x2000 0000,終止地址都是0x2000 0000+其固定的容量大小。SRAM的理解比較簡單,其作用是用來存取各種動態的輸入輸出數據、中間計算結果以及與外部存儲器交換的數據和暫存數據,用于程序運行的堆棧開銷。設備斷電后,SRAM中存儲的數據就會丟失。

Block 2

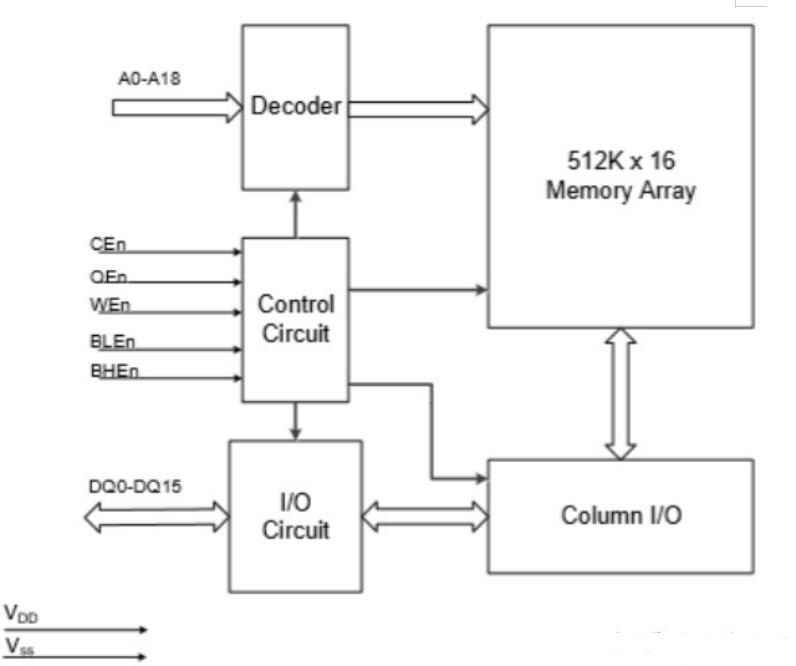

Block2 用于設計片內外設,根據總線速度的不同,Block2被分為了APB和AHB。在上圖所示的stm32f40x的映射框圖中可以看到,APB分為APB1和APB2,AHB分為AHB1和AHB2,AHB3(不在Block2的映射范圍)

ps:什么是寄存器映射

在存儲器Block2這塊區域,設計的是片上外設,它們以4個字節為一個單元,共32bit,那么每一個單元對應不同的功能,當我們控制這些單元時就可以驅動外設工作。我們可以找到每個單元的起始地址,然后通過C語言指針的操作方式來訪問這些單元,如果每次都是通過這種地址的方式來訪問,不僅不好記憶還容易出錯,這是我們可以根據每個單元的功能不同,以功能為名給這個存儲單元取一個別名,這個別名就是我們經常說的寄存器,這個給已經分配好地址的有特定功能的內存單元取別名的過程就叫寄存器映射。

舉例說明:

第一步:宏定義GPIO 口的基地址,AHB1PERIPH_BASE 依次累加 0x400的地址偏移量,就得到GPIOA~GPIOK的基地址。

#define GPIOA_BASE (AHB1PERIPH_BASE + 0x0000)

#define GPIOB_BASE (AHB1PERIPH_BASE + 0x0400)

#define GPIOC_BASE (AHB1PERIPH_BASE + 0x0800)

#define GPIOD_BASE (AHB1PERIPH_BASE + 0x0C00)

#define GPIOE_BASE (AHB1PERIPH_BASE + 0x1000)

#define GPIOF_BASE (AHB1PERIPH_BASE + 0x1400)

#define GPIOG_BASE (AHB1PERIPH_BASE + 0x1800)

#define GPIOH_BASE (AHB1PERIPH_BASE + 0x1C00)

#define GPIOI_BASE (AHB1PERIPH_BASE + 0x2000)

#define GPIOJ_BASE (AHB1PERIPH_BASE + 0x2400)

#define GPIOK_BASE (AHB1PERIPH_BASE + 0x2800)

第二步:把這個GPIO的基地址通過加上(GPIO_TypeDef *)這步騷操作,來把地址強轉成具有GPIO_TypeDef 性質的指針變量,并且用#define進行宏定義,實現取了個別名的效果。這就是寄存器的映射。

#define GPIOA ((GPIO_TypeDef *) GPIOA_BASE)

#define GPIOB ((GPIO_TypeDef *) GPIOB_BASE)

#define GPIOC ((GPIO_TypeDef *) GPIOC_BASE)

#define GPIOD ((GPIO_TypeDef *) GPIOD_BASE)

#define GPIOE ((GPIO_TypeDef *) GPIOE_BASE)

#define GPIOF ((GPIO_TypeDef *) GPIOF_BASE)

#define GPIOG ((GPIO_TypeDef *) GPIOG_BASE)

#define GPIOH ((GPIO_TypeDef *) GPIOH_BASE)

#define GPIOI ((GPIO_TypeDef *) GPIOI_BASE)

#define GPIOJ ((GPIO_TypeDef *) GPIOJ_BASE)

#define GPIOK ((GPIO_TypeDef *) GPIOK_BASE)

ps:GPIO_TypeDef結構體的聲明:

typedef struct

{

__IO uint32_t MODER; /*!< GPIO port mode register, Address offset: 0x00 */

__IO uint32_t OTYPER; /*!< GPIO port output type register, Address offset: 0x04 */

__IO uint32_t OSPEEDR; /*!< GPIO port output speed register, Address offset: 0x08 */

__IO uint32_t PUPDR; /*!< GPIO port pull-up/pull-down register, Address offset: 0x0C */

__IO uint32_t IDR; /*!< GPIO port input data register, Address offset: 0x10 */

__IO uint32_t ODR; /*!< GPIO port output data register, Address offset: 0x14 */

__IO uint16_t BSRRL; /*!< GPIO port bit set/reset low register, Address offset: 0x18 */

__IO uint16_t BSRRH; /*!< GPIO port bit set/reset high register, Address offset: 0x1A */

__IO uint32_t LCKR; /*!< GPIO port configuration lock register, Address offset: 0x1C */

__IO uint32_t AFR[2]; /*!< GPIO alternate function registers, Address offset: 0x20-0x24 */

} GPIO_TypeDef;

APB1總線外設地址

APB2總線外設地址

AHB1總線外設地址

AHB2總線外設地址

AHB3總線外設地址

Block3/Block4/Block5

FSMC Bank 的四個分區及控制寄存器

Block6

Reserved(保留)

Block7

internal peripherals,cortex-m4 內核內部外設地址。

4、代碼展示

然后看下存儲器的映射關系在代碼中是如何體現的,下圖是我項目中的stm32f4xx.h文件的部分代碼。存儲器的映射關系都在這個文件中。復制了部分代碼,供大家參考學習。感興趣的朋友可以對照自己的代碼和對應芯片規格書進行研究學習。

#define FLASH_BASE ((uint32_t)0x08000000) /*!< FLASH(up to 1 MB) base address in the alias region */

#define CCMDATARAM_BASE ((uint32_t)0x10000000) /*!< CCM(core coupled memory) data RAM(64 KB) base address in the alias region */

#define SRAM1_BASE ((uint32_t)0x20000000) /*!< SRAM1(112 KB) base address in the alias region */

#define SRAM2_BASE ((uint32_t)0x2001C000) /*!< SRAM2(16 KB) base address in the alias region */

#define SRAM3_BASE ((uint32_t)0x20020000) /*!< SRAM3(64 KB) base address in the alias region */

#define PERIPH_BASE ((uint32_t)0x40000000) /*!< Peripheral base address in the alias region */

#define BKPSRAM_BASE ((uint32_t)0x40024000) /*!< Backup SRAM(4 KB) base address in the alias region */

#if defined (STM32F40_41xxx)

#define FSMC_R_BASE ((uint32_t)0xA0000000) /*!< FSMC registers base address */

#endif /* STM32F40_41xxx */

#if defined (STM32F427_437xx) || defined (STM32F429_439xx)

#define FMC_R_BASE ((uint32_t)0xA0000000) /*!< FMC registers base address */

#endif /* STM32F427_437xx || STM32F429_439xx */

#define CCMDATARAM_BB_BASE ((uint32_t)0x12000000) /*!< CCM(core coupled memory) data RAM(64 KB) base address in the bit-band region */

#define SRAM1_BB_BASE ((uint32_t)0x22000000) /*!< SRAM1(112 KB) base address in the bit-band region */

#define SRAM2_BB_BASE ((uint32_t)0x2201C000) /*!< SRAM2(16 KB) base address in the bit-band region */

#define SRAM3_BB_BASE ((uint32_t)0x22400000) /*!< SRAM3(64 KB) base address in the bit-band region */

#define PERIPH_BB_BASE ((uint32_t)0x42000000) /*!< Peripheral base address in the bit-band region */

#define BKPSRAM_BB_BASE ((uint32_t)0x42024000) /*!< Backup SRAM(4 KB) base address in the bit-band region

/*!< Peripheral memory map */

#define APB1PERIPH_BASE PERIPH_BASE

#define APB2PERIPH_BASE (PERIPH_BASE + 0x00010000)

#define AHB1PERIPH_BASE (PERIPH_BASE + 0x00020000)

#define AHB2PERIPH_BASE (PERIPH_BASE + 0x10000000)

/*!< APB1 peripherals */

#define TIM2_BASE (APB1PERIPH_BASE + 0x0000)

#define TIM3_BASE (APB1PERIPH_BASE + 0x0400)

#define TIM4_BASE (APB1PERIPH_BASE + 0x0800)

#define TIM5_BASE (APB1PERIPH_BASE + 0x0C00)

#define TIM6_BASE (APB1PERIPH_BASE + 0x1000)

#define TIM7_BASE (APB1PERIPH_BASE + 0x1400)

#define TIM12_BASE (APB1PERIPH_BASE + 0x1800)

#define TIM13_BASE (APB1PERIPH_BASE + 0x1C00)

#define TIM14_BASE (APB1PERIPH_BASE + 0x2000)

#define RTC_BASE (APB1PERIPH_BASE + 0x2800)

#define WWDG_BASE (APB1PERIPH_BASE + 0x2C00)

#define IWDG_BASE (APB1PERIPH_BASE + 0x3000)

#define I2S2ext_BASE (APB1PERIPH_BASE + 0x3400)

#define SPI2_BASE (APB1PERIPH_BASE + 0x3800)

#define SPI3_BASE (APB1PERIPH_BASE + 0x3C00)

#define I2S3ext_BASE (APB1PERIPH_BASE + 0x4000)

/*!< AHB1 peripherals */

#define GPIOA_BASE (AHB1PERIPH_BASE + 0x0000)

#define GPIOB_BASE (AHB1PERIPH_BASE + 0x0400)

#define GPIOC_BASE (AHB1PERIPH_BASE + 0x0800)

#define GPIOD_BASE (AHB1PERIPH_BASE + 0x0C00)

#define GPIOE_BASE (AHB1PERIPH_BASE + 0x1000)

#define GPIOF_BASE (AHB1PERIPH_BASE + 0x1400)

#define GPIOG_BASE (AHB1PERIPH_BASE + 0x1800)

#define GPIOH_BASE (AHB1PERIPH_BASE + 0x1C00)

#define GPIOI_BASE (AHB1PERIPH_BASE + 0x2000)

#define GPIOJ_BASE (AHB1PERIPH_BASE + 0x2400)

#define GPIOK_BASE (AHB1PERIPH_BASE + 0x2800)

/*!< APB2 peripherals */

#define TIM1_BASE (APB2PERIPH_BASE + 0x0000)

#define TIM8_BASE (APB2PERIPH_BASE + 0x0400)

#define USART1_BASE (APB2PERIPH_BASE + 0x1000)

#define USART6_BASE (APB2PERIPH_BASE + 0x1400)

#define ADC1_BASE (APB2PERIPH_BASE + 0x2000)

#define ADC2_BASE (APB2PERIPH_BASE + 0x2100)

#define ADC3_BASE (APB2PERIPH_BASE + 0x2200)

#define ADC_BASE (APB2PERIPH_BASE + 0x2300)

#define SDIO_BASE (APB2PERIPH_BASE + 0x2C00)

#define SPI1_BASE (APB2PERIPH_BASE + 0x3000)

/*!< FSMC Bankx registers base address */

#define FSMC_Bank1_R_BASE (FSMC_R_BASE + 0x0000)

#define FSMC_Bank1E_R_BASE (FSMC_R_BASE + 0x0104)

#define FSMC_Bank2_R_BASE (FSMC_R_BASE + 0x0060)

#define FSMC_Bank3_R_BASE (FSMC_R_BASE + 0x0080)

#define FSMC_Bank4_R_BASE (FSMC_R_BASE + 0x00A0)

今天分享的內容就到這里。結合我自己理解的同時,查閱了大量的相關文檔。本人能力有限,難免存在疏漏之處。如有問題,歡迎指正。

電子發燒友App

電子發燒友App

評論