的可行性。##以并行多相濾波結(jié)構(gòu)為基礎(chǔ)的算法實(shí)現(xiàn)了數(shù)字中頻信號(hào)的基帶變換,且數(shù)字下變頻后信號(hào)帶內(nèi)平坦度較好,滿足工程應(yīng)用需求。

2014-02-22 10:23:41 3144

3144 為了滿足智能手機(jī)功能日益提高的數(shù)據(jù)需求,現(xiàn)代數(shù)字移動(dòng)通信系統(tǒng)的基礎(chǔ)設(shè)施必須持續(xù)發(fā)展以支持更寬的帶寬和更快的數(shù)據(jù)轉(zhuǎn)換。為實(shí)現(xiàn)高速的數(shù)據(jù)速率,數(shù)字轉(zhuǎn)換器中的數(shù)字中頻處理、包括DDC(數(shù)字下變頻器)和DUC(數(shù)字上變頻器)是其中主要的功能模塊。

2016-11-21 13:16:12 3250

3250

問題,為什么不一次變頻到70M呢.我想用adf4153可以一次就產(chǎn)生1020-1820的混頻信號(hào),為什么不這么做呢?問題二,是不是下變頻的主電路都必須做50歐的阻抗控制(非數(shù)字部分).第三,有沒有軟件可以對(duì)整個(gè)電路,包括adf4113,adf4153在內(nèi)的下變頻,混頻,濾波,電阻橋負(fù)載均衡等進(jìn)行整體仿真

2015-09-20 11:47:07

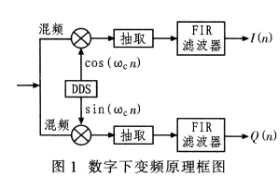

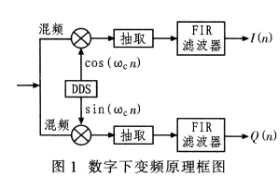

實(shí)現(xiàn)FPGA數(shù)字下變頻的多類濾波器分組級(jí)聯(lián)技術(shù)分析1 引 言 本文針對(duì)以下高效算法做了總結(jié),進(jìn)行合理的分組級(jí)聯(lián)并引入流水線技術(shù)以便于在FPGA上實(shí)現(xiàn)。數(shù)字下變頻(DDC)就是通過混頻、抽取和濾波等

2009-10-23 10:26:53

AD采樣80MHz,中頻信號(hào)60MHz,在數(shù)字下變頻時(shí)NCO輸出頻率設(shè)置為多少?

2017-02-15 16:00:19

數(shù)字下變頻中的抽取和直接降低AD的采樣率有什么區(qū)別?比如AD采樣率100M,下抽倍數(shù)為4倍,和AD采樣率25M有什么區(qū)別。

2017-11-03 21:53:13

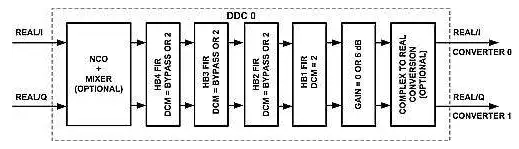

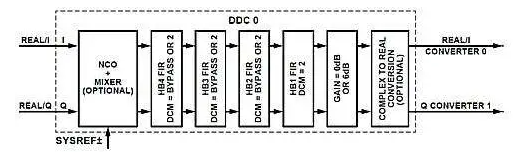

時(shí)的輸入時(shí)鐘為368.64 MHz,模擬 輸入頻率為270 MHz。首先,理解AD9680中數(shù)字處理模塊的 設(shè)置很重要。AD9680將設(shè)為使用數(shù)字下變頻器(DDC),其輸 入為實(shí)數(shù),輸出為復(fù)數(shù),數(shù)控

2018-11-01 11:19:48

數(shù)字上/下變頻器:VersaCOMM?白皮書

2019-07-08 09:33:14

AD9625或者AD9680之類的高速ADC本身自帶NCO和混頻功能以及DDC,這些功能使用的時(shí)候是否會(huì)帶來(lái)像ZERO-IF的直流偏置影響?我同事在用verilog自己做復(fù)數(shù)下變頻和復(fù)數(shù)混頻仿真

2023-12-20 07:42:09

為了滿足智能手機(jī)功能日益提高的數(shù)據(jù)需求,現(xiàn)代數(shù)字移動(dòng)通信系統(tǒng)的基礎(chǔ)設(shè)施必須持續(xù)發(fā)展以支持更寬的帶寬和更快的數(shù)據(jù)轉(zhuǎn)換。為實(shí)現(xiàn)高速的數(shù)據(jù)速率,數(shù)字轉(zhuǎn)換器中的數(shù)字中頻處理、包括DDC(數(shù)字下變頻

2019-08-01 07:26:17

TF功能包能干什么?TF坐標(biāo)變換如何實(shí)現(xiàn)?

2022-02-14 06:29:50

。關(guān)于pmsm在dq坐標(biāo)軸下的四大方程在此就不做贅述,下面給出simulink中自己搭建的坐標(biāo)變換模塊等文件,其中clark模塊的alpha軸參考是以A軸重合的,另外模塊中的Cta輸入指的是電機(jī)的電

2018-09-16 13:02:18

本帖最后由 eehome 于 2013-1-5 09:44 編輯

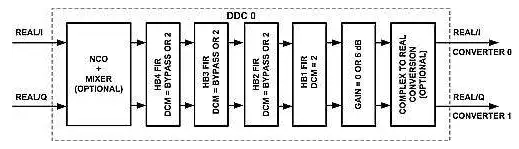

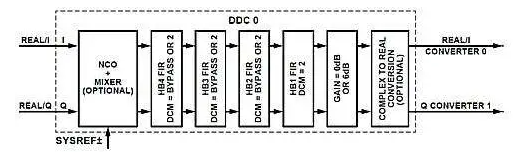

這是系統(tǒng)的一個(gè)模塊,實(shí)現(xiàn)了數(shù)字下變頻功能。

2012-06-06 15:59:13

小弟最近在做一個(gè)數(shù)字下變頻和脈沖壓縮的仿真,現(xiàn)在一點(diǎn)頭緒都沒有,有沒有大神指教一下方向的。希望大神不吝賜教,或者是有源代碼能分享一下,跪謝了。

2017-03-11 10:50:24

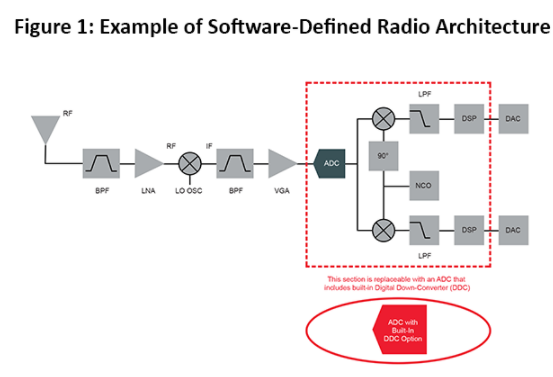

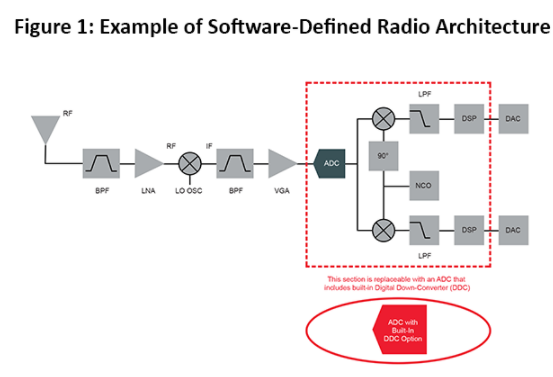

近年來(lái),軟件無(wú)線電已經(jīng)成為通信領(lǐng)域一個(gè)新的發(fā)展方向,數(shù)字下變頻技術(shù)(Digital Down Converter-DDC)是軟件無(wú)線電的核心技術(shù)之一,也是計(jì)算量最大的部分。基于FPGA的DDC

2019-09-20 06:13:11

近年來(lái),軟件無(wú)線電已經(jīng)成為通信領(lǐng)域一個(gè)新的發(fā)展方向,數(shù)字下變頻技術(shù)(Digital Down Converter-DDC)是軟件無(wú)線電的核心技術(shù)之一,也是計(jì)算量最大的部分。基于FPGA的DDC

2019-10-12 08:17:00

基于FPGA設(shè)計(jì)了一高速數(shù)字下變頻系統(tǒng),在設(shè)計(jì)中利用并行NCO和多相濾波相結(jié)合的方法有效的降低了數(shù)據(jù)的速率,以適合數(shù)字信號(hào)處理器件的工作頻率。

2019-09-26 07:06:35

采用ADC(LTC2208)、FPGA和SDRAM(HY57V561620)設(shè)計(jì)高速的數(shù)據(jù)采集及正交下變頻系統(tǒng),其中數(shù)據(jù)采樣速率90MSPS;實(shí)現(xiàn)70M中頻的數(shù)字正交下變頻…………請(qǐng)求大牛的幫助啊,我是小菜鳥,這方面還需要你們的大力提攜啊,萬(wàn)分感謝

2014-04-01 10:44:33

數(shù)字上變頻/下變頻(DUC/DDC)是數(shù)字中頻設(shè)計(jì)的重要組成部分,其功能是將基帶信號(hào)經(jīng)過內(nèi)插濾波后變到中頻的頻率,或者將中頻的信號(hào)經(jīng)過抽取濾波后降到基帶的頻率上。

2019-08-21 06:24:03

數(shù)字上變頻/下變頻(DUC/DDC)是數(shù)字中頻設(shè)計(jì)的重要組成部分,其功能是將基帶信號(hào)經(jīng)過內(nèi)插濾波后變到中頻的頻率,或者將中頻的信號(hào)經(jīng)過抽取濾波后降到基帶的頻率上。本文的主要目的就是介紹多天線多載波數(shù)字上下變頻的FPGA實(shí)現(xiàn)方法,以及Altera提供的一種數(shù)字信號(hào)處理的工具,DSP BUILDER。

2019-09-25 08:22:51

A/D轉(zhuǎn)換后的高速信號(hào),分別通過DDC進(jìn)行下變頻和多級(jí)抽取濾波。該無(wú)源雷達(dá)信號(hào)處理機(jī)已經(jīng)通過了外場(chǎng)試驗(yàn)驗(yàn)證,其中的中頻采集板卡經(jīng)測(cè)試可以精確實(shí)現(xiàn)數(shù)字下變頻功能,精確度為0.01Hz;抽取模塊實(shí)現(xiàn)信號(hào)

2019-06-04 05:00:17

數(shù)字上變頻/下變頻(DUC/DDC, digital up convert/ digital down convert)是數(shù)字中頻設(shè)計(jì)的重要組成部分,其功能是將基帶信號(hào)經(jīng)過內(nèi)插濾波后變到中頻的頻率

2019-08-09 06:52:39

如何使用一個(gè)FPGA實(shí)現(xiàn)64個(gè)獨(dú)立的下變頻通道?

2021-04-29 06:37:05

如何去實(shí)現(xiàn)一種基于STM32的正弦波上下變頻呢?有哪些步驟?

2021-11-15 07:47:06

在電機(jī)仿真過程中,需要采用坐標(biāo)變換理論把交流電機(jī)通過坐標(biāo)變換理論等效為直流電機(jī)進(jìn)行解耦控制,Park(abctodq0/dq0toabc)變換和Clark(abctoαβ/αβtoabc

2021-09-03 06:24:55

針對(duì)頻分復(fù)用(FDM) 應(yīng)用進(jìn)行額外濾波。高性能GSPS ADC現(xiàn)將數(shù)字下變頻(DDC)功能在信號(hào)鏈中進(jìn)一步提升,以使其位于基于賽靈思FPGA的設(shè)計(jì)解決方案的ADC之中。該方案為高速系統(tǒng)架構(gòu)師提供了多種

2019-07-29 07:14:03

我是Xilinx的全新用戶,請(qǐng)耐心等待。我想實(shí)現(xiàn)數(shù)字下變頻器,但我需要的參數(shù)不同于ISE中提供的DUC / DDC編譯器。例如,我沒有使用特定的無(wú)線標(biāo)準(zhǔn),我的通道帶寬是10 kHz而不是提供的選擇

2019-02-12 10:58:29

,因?yàn)殛P(guān)于樣本的信息要到ADC處理完信號(hào)之后才能確定。現(xiàn)在,高性能GSPS ADC讓數(shù)字下變頻(DDC)功能在信號(hào)鏈中前移,進(jìn)駐到ADC內(nèi)部。這就給高速系統(tǒng)架構(gòu)師提供了多種新的設(shè)計(jì)選擇。然而,這一功能

2018-10-26 11:16:21

本文提出的DSP控制多片DDC芯片的接口設(shè)計(jì)方案,對(duì)于4路A/D轉(zhuǎn)換后的高速信號(hào),分別通過DDC進(jìn)行下變頻和多級(jí)抽取濾波。

2021-04-20 06:20:27

本文介紹了一種應(yīng)用于數(shù)字化中頻頻譜分析儀的數(shù)字下變頻電路,整個(gè)電路基于FPGA實(shí)現(xiàn),結(jié)構(gòu)簡(jiǎn)單,易于編程實(shí)現(xiàn)。

2021-04-15 06:21:22

RF:2.401GHz~2.473GHz IF: 中頻輸出大概在70M左右射頻輸入頻率范圍如上所示。求助下變頻芯片推薦

2012-03-14 19:01:37

簡(jiǎn)要闡述數(shù)字下變頻器的發(fā)展和更新

2021-05-19 06:22:14

您好:數(shù)字下變頻芯片AD6620的使用手冊(cè)第18頁(yè)的figure28,注意其中的的CLK以及tDPR和tDPF,這個(gè)CLK是進(jìn)入DDC時(shí)的數(shù)據(jù)采樣時(shí)鐘嗎?如果是的話,那這個(gè)CLK是很大的值,意思是說

2018-12-04 09:05:41

數(shù)字濾波器的實(shí)現(xiàn)一般有哪幾條途徑?寬帶無(wú)線通信的數(shù)字上下變頻是什么?濾波器的輸入數(shù)據(jù)流有什么特點(diǎn)?

2021-04-14 06:21:44

GC5016及其結(jié)構(gòu)是什么?怎樣去設(shè)計(jì)GC5016數(shù)字上下變頻系統(tǒng)的硬件部分?怎樣去設(shè)計(jì)GC5016數(shù)字上下變頻系統(tǒng)的軟件部分?

2021-05-24 06:49:59

手冊(cè)可以發(fā)現(xiàn),就連設(shè)置鏈路都要面對(duì)一大堆字母組合。早先的LVDS ADC比較易于實(shí)現(xiàn),而新一代JESD204B ADC則稍微復(fù)雜一些。如果考慮到內(nèi)部數(shù)字下變頻器(DDC)的設(shè)置,則會(huì)更加復(fù)雜。盡管如此

2018-10-30 15:06:13

本文介紹了數(shù)字下變頻的組成結(jié)構(gòu),并通過一個(gè)具體的實(shí)例,給出了FPGA 實(shí)現(xiàn)的具體過程。

2009-11-30 14:11:52 34

34 數(shù)字下變頻器中坐標(biāo)變換模塊的ASIC 實(shí)現(xiàn)成都電子科技大學(xué)通信與信息工程學(xué)院劉欣 林水生 李廣軍摘要:本文介紹了一種基于CORDIC 算法的數(shù)字下頻器(DDC)中坐標(biāo)變換模塊的

2009-12-24 10:54:50 13

13 FPGA在軟件無(wú)線電中的工程應(yīng)用之數(shù)字上下變頻篇

2010-02-09 11:10:36 59

59 在微型SAR 實(shí)時(shí)成像樣機(jī)的設(shè)計(jì)中,對(duì)雷達(dá)回波在中頻進(jìn)行采樣,然后采用數(shù)字下變頻技術(shù)實(shí)現(xiàn)正交解調(diào),可以減少系統(tǒng)的復(fù)雜性,提高雷達(dá)的數(shù)字化程度和性能。該文針對(duì)微型SAR 方

2010-02-09 11:59:45 17

17 介紹了一種基于新型FPGA的高速數(shù)字下變頻的實(shí)現(xiàn)方法,它充分利用數(shù)字下變頻的優(yōu)化算法以及FPGA領(lǐng)域的新技術(shù),去除由于數(shù)據(jù)速率過高而造成的各種瓶頸,極大地減少了計(jì)算量和FPG

2010-07-02 16:49:24 21

21 數(shù)字下變頻是軟件無(wú)線電系統(tǒng)的重要組成部分,主要完成對(duì)信號(hào)的混頻、濾波、抽取和整形等工作,包括數(shù)字混頻模塊和抽取濾波模塊。在數(shù)字下變頻系統(tǒng)實(shí)現(xiàn)方案中,輸入的模擬

2010-11-02 15:26:27 48

48 基于FPGA芯片Stratix II EP2S60F672C4設(shè)計(jì)了一個(gè)適用于寬帶數(shù)字接收機(jī)的帶寬可變的數(shù)字下變頻器(VB-DDC)。該VB-DDC結(jié)合傳統(tǒng)數(shù)字下變頻結(jié)構(gòu)與多相濾波結(jié)構(gòu)的優(yōu)點(diǎn),實(shí)現(xiàn)了對(duì)輸入中頻信

2010-11-11 15:56:54 57

57 數(shù)字下變頻(DDC)是軟件無(wú)線電中的關(guān)鍵技術(shù)之一。通過DDC處理,大數(shù)據(jù)流中頻信號(hào)變?yōu)榈蛿?shù)據(jù)率的基帶信號(hào),以便于后續(xù)信號(hào)處理。以多通道GPS/BD-2陣列接收機(jī)項(xiàng)目為背景,提出了

2010-12-11 15:40:22 13

13 matlab坐標(biāo)變換

坐標(biāo)變換

cart2pol 笛卡兒坐標(biāo)變換為極坐標(biāo)或圓柱坐標(biāo) cart2sph 笛卡兒坐標(biāo)變換為球坐標(biāo)

2008-06-18 14:47:50 2210

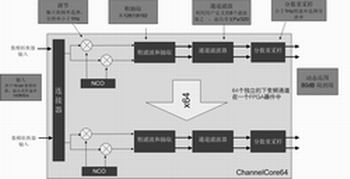

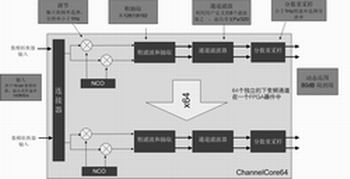

2210 使用一個(gè)FPGA便可實(shí)現(xiàn)的64通道下變頻器

RF Engines公司的ChannelCore64使設(shè)計(jì)者能夠用一個(gè)可對(duì)FPGA編程的IP核來(lái)替代多達(dá)16個(gè)DDC(直接下變頻器)ASIC,可顯著減少PCB面積

2010-01-18 16:34:34 1147

1147

數(shù)字下變頻是軟件無(wú)線電系統(tǒng)的重要組成部分,主要完成對(duì)信號(hào)的混頻、 濾波、抽取和整形等工作,包括數(shù)字混頻模塊和抽取濾波模塊。在數(shù)字下變頻系 統(tǒng)實(shí)現(xiàn)方案中,輸入的模擬中

2011-03-29 10:02:47 96

96 德州儀器(TI)推出數(shù)字上/下變頻轉(zhuǎn)換器(DUC/DDC)。 GC6016 可在具有高達(dá)155MS/s復(fù)合帶寬的 4 組發(fā)射串流與 8 組接收串流中支持 1 到 48 個(gè) DUC / DDC 通道

2011-04-26 09:37:51 1479

1479 本文以某雷達(dá)對(duì)抗偵察數(shù)字接收機(jī)為例,介紹一種基于TI公司的DSP TMS320C6416的數(shù)字下變頻器。

2011-08-09 11:15:54 2425

2425

寬帶短波信道模擬器是一種運(yùn)用仿真技術(shù)對(duì)真實(shí)的短波信道進(jìn)行模擬的儀器。首先指出數(shù)字下變頻在寬帶短波信道模擬器中的作用。然后,闡述了數(shù)字下變頻中的數(shù)控振蕩器、CIC 濾波器

2011-09-15 18:30:21 1669

1669

闡述了雷達(dá)中頻正交采樣的原理,研究了使用System Generator實(shí)現(xiàn)數(shù)字下變頻的一種自頂向下的新型設(shè)計(jì)方法。在Simulink中進(jìn)行了功能仿真驗(yàn)證.

2012-02-09 15:13:48 46

46 數(shù)字下變頻技術(shù)是軟件無(wú)線電的核心技術(shù)之一。本文首先介紹了DDC的組成結(jié)構(gòu),然后詳細(xì)分析了DDC各功能模塊的工作原理,通過Modelsim完成了DDC其主要模塊的仿真和調(diào)試,并進(jìn)行初步系統(tǒng)

2012-05-23 11:07:59 1984

1984

FPGA在軟件無(wú)線電中的工程應(yīng)用之數(shù)字上下變頻篇

2016-04-25 09:38:10 8

8 基于FPGA的DDC數(shù)字下變頻設(shè)計(jì),有興趣的同學(xué)可以下載學(xué)習(xí)

2016-04-27 16:18:12 59

59 一種基于流水線DA算法的數(shù)字下變頻器_周云

2017-01-07 22:14:03 2

2 數(shù)字下變頻程序,可直接用于項(xiàng)目

2017-08-30 08:45:24 23

23 設(shè)計(jì)和實(shí)現(xiàn)了基于FPGA的可編程數(shù)字下變頻器(DDC),用于寬帶數(shù)字中頻軟件無(wú)線電接收機(jī)中,主要完成了數(shù)字下變頻、數(shù)據(jù)抽取等功能。采用自頂向下的模塊化設(shè)計(jì)方法,將整個(gè)下變頻器劃分為基本單元,實(shí)現(xiàn)這些

2017-11-22 09:09:56 5706

5706

上下變頻的FPGA實(shí)現(xiàn)方法,以及Altera提供的一種數(shù)字信號(hào)處理的工具,DSP BUILDER。 DUC/DDC的實(shí)現(xiàn)架構(gòu) 以TD-SCDMA的DUC/DDC為例,基帶頻率1.28MHz, 4天線

2017-11-25 02:31:01 259

259

數(shù)字下變頻是 無(wú)線通信 鏈路層的重要組成部分, 寬帶 信號(hào)和窄帶信號(hào)的下變頻由于信號(hào)帶寬不同而抽取因子不同,使得同時(shí)具有寬帶和窄帶信號(hào)的系統(tǒng)采用基于 FPGA 的系統(tǒng)很難實(shí)現(xiàn)。本文提出采用專用數(shù)字

2017-12-05 09:49:31 3044

3044

數(shù)字上變頻/下變頻(DUC/DDC)是數(shù)字中頻設(shè)計(jì)的重要組成部分,其功能是將基帶信號(hào)經(jīng)過內(nèi)插濾波后變到中頻的頻率,或者將中頻的信號(hào)經(jīng)過抽取濾波后降到基帶的頻率上。本文的主要目的就是介紹多天線多載波數(shù)字上下變頻的FPGA實(shí)現(xiàn)方法,以及Altera提供的一種數(shù)字信號(hào)處理的工具,DSP BUILDER。

2019-03-13 15:16:58 1743

1743

重新思考快速寬頻ADC中的數(shù)字下變頻

2018-04-23 10:41:12 1

1 上下變頻的FPGA實(shí)現(xiàn)方法,以及Altera提供的一種數(shù)字信號(hào)處理的工具,DSP BUILDER。 DUC/DDC的實(shí)現(xiàn)架構(gòu) 以TD-SCDMA的DUC/DDC為例,基帶頻率1.28MHz, 4天線

2018-09-15 04:57:00 2800

2800 為了滿足智能手機(jī)功能日益提高的數(shù)據(jù)需求,現(xiàn)代數(shù)字移動(dòng)通信系統(tǒng)的基礎(chǔ)設(shè)施必須持續(xù)發(fā)展以支持更寬的帶寬和更快的數(shù)據(jù)轉(zhuǎn)換。為實(shí)現(xiàn)高速的數(shù)據(jù)速率,數(shù)字轉(zhuǎn)換器中的數(shù)字中頻處理、包括DDC(數(shù)字下變頻

2020-09-29 10:44:00 1

1 數(shù)字下變頻DDC(digital down lonvwrsionl作為系統(tǒng)前端A/D轉(zhuǎn)換器與后端通用DSP器件間的橋梁,通過降低數(shù)據(jù)流的速率,將低速數(shù)據(jù)送給后端通用DSP器件處理,其性能的優(yōu)劣將對(duì)

2020-08-06 15:31:17 728

728

本文檔的主要內(nèi)容詳細(xì)介紹的是使用FPGA實(shí)現(xiàn)數(shù)字下變頻器DDC的設(shè)計(jì)資料合集免費(fèi)下載。

2020-08-10 17:27:46 26

26 原理*數(shù)字下變頻器(DDC是接收機(jī)A/D變換后,首先要完成的處理工作,一般的DDC由本地振蕩器(NCO)、混頻器、低通濾波器和抽取器組成主要作用:其一是把中頻信號(hào)變?yōu)榱阒蓄l信號(hào);其二是降低采樣率

2020-08-17 16:38:31 13

13 系統(tǒng)先將射頻信號(hào)模擬混頻至統(tǒng)一的中頻信號(hào),使用ADC器件對(duì)其采樣,采樣后的中頻信號(hào)經(jīng)過數(shù)字下變頻器即圖中的DDC模塊變?yōu)榈退俚幕鶐盘?hào)再送往DSP進(jìn)行實(shí)時(shí)信號(hào)處理它在整個(gè)軟件無(wú)線電系統(tǒng)中的主要作用

2020-09-01 16:02:00 7

7 研究了高倍抽取的數(shù)字下變頻設(shè)計(jì),重點(diǎn)分析了基于級(jí)聯(lián)積分梳狀濾波器和級(jí)聯(lián)半帶濾波器的多級(jí)抽樣頻率算法。并提出了用最新的Systemgenerator軟件實(shí)現(xiàn)FPGA 的設(shè)計(jì)、仿真方案,縮短了開發(fā)周期

2020-11-05 17:04:55 14

14 數(shù)字上/下變頻器簡(jiǎn)介:VersaCOMM?可重構(gòu)數(shù)字轉(zhuǎn)換器

2021-05-12 20:53:04 0

0 AD6636:150 MSPS、寬帶、數(shù)字下變頻器(DDC)數(shù)據(jù)表

2021-05-27 20:46:49 4

4 基于FPGA的DDC(數(shù)字下變頻)設(shè)計(jì)與實(shí)現(xiàn)(電源技術(shù)審稿費(fèi)多少)-該文檔為基于FPGA的DDC(數(shù)字下變頻)設(shè)計(jì)與實(shí)現(xiàn)講解文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-09-15 12:04:22 28

28 基于FPGA的數(shù)字下變頻器(DDC)的設(shè)計(jì)(ups電源技術(shù)轉(zhuǎn)讓)-基于FPGA的數(shù)字下變頻器(DDC)的設(shè)計(jì).適合新手學(xué)習(xí)參考

2021-09-16 11:43:52 37

37 為了滿足智能手機(jī)功能日益提高的數(shù)據(jù)需求,現(xiàn)代數(shù)字移動(dòng)通信系統(tǒng)的基礎(chǔ)設(shè)施必須持續(xù)發(fā)展以支持更寬的帶寬和更快的數(shù)據(jù)轉(zhuǎn)換。為實(shí)現(xiàn)高速的數(shù)據(jù)速率,數(shù)字轉(zhuǎn)換器中的數(shù)字中頻處理、包括DDC(數(shù)字下變頻

2022-10-10 11:18:13 1449

1449 在本文的第一部分“數(shù)字下變頻器——第1部分”中,我們探討了行業(yè)對(duì)更高頻率RF頻段采樣的推動(dòng),以及數(shù)字下變頻器(DDC)如何實(shí)現(xiàn)這種類型的無(wú)線電架構(gòu)。討論了與AD9680系列產(chǎn)品中的DDC相關(guān)的幾個(gè)技術(shù)方面。

2023-01-05 14:28:21 1997

1997

變頻器電路系統(tǒng)主要由基帶數(shù)據(jù)生成模塊(pcm.v)、ASK調(diào)制模塊(ask_mod.v) 、按鍵消抖模塊(keyskew.v)、上變頻器模塊(duc.v)、下變頻器模塊(ddc.v)和選擇控制邏輯電路組成。

2023-01-31 09:21:11 1616

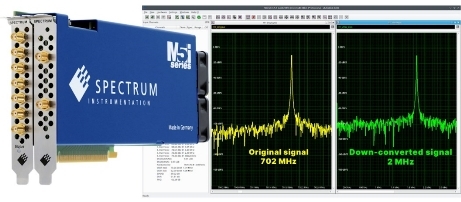

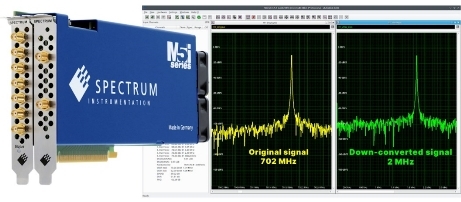

1616 Spectrum儀器PCIe數(shù)字化儀系列產(chǎn)品現(xiàn)已支持數(shù)字下變頻(DDC),這主要得益于產(chǎn)品使用的可進(jìn)行動(dòng)態(tài)及即時(shí)處理的外接顯卡,這也顯著降低了產(chǎn)品的成本。DDC被廣泛應(yīng)用于通信系統(tǒng),其中包括數(shù)字

2023-04-19 13:26:06 345

345

當(dāng)今的數(shù)字無(wú)線電架構(gòu)嚴(yán)重依賴先進(jìn)的數(shù)字信號(hào)處理技術(shù),例如用于同相和正交(I/Q)信號(hào)檢測(cè)的數(shù)字下變頻(DDC)和用于改善信噪比(SNR)的數(shù)字抽取濾波。DDC和許多其他數(shù)字處理功能通常由數(shù)字構(gòu)建模塊實(shí)現(xiàn),這些構(gòu)建模塊需要使用現(xiàn)場(chǎng)可編程門陣列(FPGA)進(jìn)行廣泛的固件操作。

2023-05-06 09:40:26 490

490

下變頻器(Downconverter)用于將高頻信號(hào)轉(zhuǎn)換為較低頻率的信號(hào)。輸入信號(hào)的幅度(即信號(hào)的電壓或功率級(jí)別)會(huì)對(duì)下變頻的影響產(chǎn)生以下幾個(gè)方面的影響。

2023-06-07 10:18:25 543

543 回想一下示例中,AD9680-500的工作輸入時(shí)鐘為491.52 MHz,模擬輸入頻率為150.1 MHz。AD9680設(shè)置為使用數(shù)字下變頻器(DDC),具有實(shí)輸入、復(fù)數(shù)輸出、155 MHzNCO

2023-06-30 15:18:00 717

717

在本例中,我們將介紹AD9680-500,其工作輸入時(shí)鐘為491.52 MHz,模擬輸入頻率為150.1 MHz。AD9680將設(shè)置為使用數(shù)字下變頻器(DDC),具有實(shí)際輸入、復(fù)數(shù)輸出、155

2023-06-30 15:20:25 747

747

電子發(fā)燒友網(wǎng)站提供《數(shù)字下變頻在人工智能引擎上的實(shí)現(xiàn)應(yīng)用說明.pdf》資料免費(fèi)下載

2023-09-13 15:06:31 0

0

![]() ,其中Si={-1,+1},則tanθi=Si2-i,可得

,其中Si={-1,+1},則tanθi=Si2-i,可得

,我們暫不考慮這個(gè)常數(shù)增益,這樣式(2-3)就變?yōu)?br>

,我們暫不考慮這個(gè)常數(shù)增益,這樣式(2-3)就變?yōu)?br>

,給定向量 一組初值如下

,給定向量 一組初值如下![]()

![]() ,即可求得向量A的幅值和相位。由式(2-4)可知每次旋轉(zhuǎn)的角度的正切值都是2的負(fù)冪次,在硬件實(shí)現(xiàn)時(shí)只需要執(zhí)行右移和相加運(yùn)算就可以實(shí)現(xiàn)每次迭代,易于硬件的實(shí)現(xiàn)。

,即可求得向量A的幅值和相位。由式(2-4)可知每次旋轉(zhuǎn)的角度的正切值都是2的負(fù)冪次,在硬件實(shí)現(xiàn)時(shí)只需要執(zhí)行右移和相加運(yùn)算就可以實(shí)現(xiàn)每次迭代,易于硬件的實(shí)現(xiàn)。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論