關(guān)鍵詞:直接數(shù)字頻率合成器 相位累加器 信號(hào)源 現(xiàn)場(chǎng)可編程門限列

1971年,美國(guó)學(xué)者J.Tierney等人撰寫的“A Digital Frequency Synthesizer”-文首次提出了以全數(shù)字技術(shù),從相位概念出發(fā)直接合成所需波形的一種新給 成原理。限于當(dāng)時(shí)的技術(shù)和器件產(chǎn),它的性牟指標(biāo)尚不能與已有的技術(shù)盯比,故未受到重視。近1年間,隨著微電子技術(shù)的迅速發(fā)展,直接數(shù)字頻率合成器(Direct Digital Frequency Synthesis簡(jiǎn)稱DDS或DDFS)得到了飛速的發(fā)展,它以有別于其它頻率合成方法的優(yōu)越性能和特點(diǎn)成為現(xiàn)代頻率合成技術(shù)中的姣姣者。具體體現(xiàn)在相對(duì)帶寬寬、頻率轉(zhuǎn)換時(shí)間短、頻率分辨率高、輸出相位連續(xù)、可產(chǎn)生寬帶正交信號(hào)及其他多種調(diào)制信號(hào)、可編程和全數(shù)字化、控制靈活方便等方面,并具有極高的性價(jià)比。

1 DDS基本原理及性能特點(diǎn)

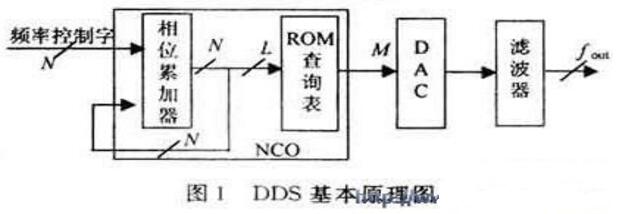

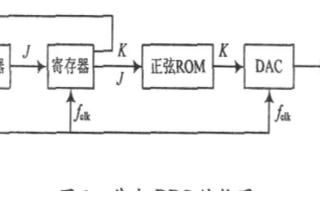

DDS的基本大批量是利用采樣定量,通過(guò)查表法產(chǎn)生波形。DDS的結(jié)構(gòu)有很多種,其基本的電路原理可用圖1來(lái)表示。

相位累加器由N位加法器與N位累加寄存器級(jí)聯(lián)構(gòu)成。每來(lái)一個(gè)時(shí)鐘脈沖fs,加法器將控制字k與累加寄存器輸出的累加相位數(shù)據(jù)相加,把相加后的結(jié)果送到累加寄存器的數(shù)據(jù)輸入端,以使加法器在下一個(gè)時(shí)鐘脈沖的作用下繼續(xù)與頻率控制字相加。這樣,相位累加器在時(shí)鐘作用下,不斷對(duì)頻率控制字進(jìn)行線性相位加累加。由此可以看出,相位累加器在每一個(gè)中輸入時(shí),把頻率控制字累加一次,相位累加器輸出的數(shù)據(jù)就是合成信號(hào)的相位,相位累加器的出頻率就是DDS輸出的信號(hào)頻率。

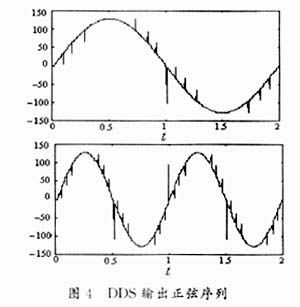

用相位累加器輸出的數(shù)據(jù)作為波形存儲(chǔ)器(ROM)的相位取樣地址。這樣就可把存儲(chǔ)在波形存儲(chǔ)器內(nèi)的波形抽樣值(二進(jìn)制編碼)經(jīng)查找表查出,完成相位到幅值轉(zhuǎn)換。波形存儲(chǔ)器的輸出送到D/A轉(zhuǎn)換器,D/A轉(zhuǎn)換器將數(shù)字量形式的波形幅值轉(zhuǎn)換成所要求合成頻率的模擬量形式信號(hào)。低通濾波器用于濾除不需要的取樣分量,以便輸出頻譜純凈的正弦波信號(hào)。

DDS在相對(duì)帶寬、頻率轉(zhuǎn)換時(shí)間、高分頭放力、相位連續(xù)性、正交輸出以及集成化等一系列性能指標(biāo)方面遠(yuǎn)遠(yuǎn)超過(guò)了傳統(tǒng)頻率合成技術(shù)所能達(dá)到的水平,為系統(tǒng)提供了優(yōu)于模擬信號(hào)源的性能。

(1)輸出頻率相對(duì)帶寬較寬

輸出頻率帶寬為50%fs(理論值)。但考慮到低通濾波器的特性和設(shè)計(jì)難度以及對(duì)輸出信號(hào)雜散的抑制,實(shí)際的輸出頻率帶寬仍能達(dá)到40%fs。

(2)頻率轉(zhuǎn)換時(shí)間短

DDS是一個(gè)開(kāi)環(huán)系統(tǒng),無(wú)任何反饋環(huán)節(jié),這種結(jié)構(gòu)使得DDS的頻率轉(zhuǎn)換時(shí)間極短。事實(shí)上,在DDS的頻率控制字改變之后,需經(jīng)過(guò)一個(gè)時(shí)鐘周期之后按照新的相位增量累加,才能實(shí)現(xiàn)頻率的轉(zhuǎn)換。因此,頻率時(shí)間等于頻率控制字的傳輸,也就是一個(gè)時(shí)鐘周期的時(shí)間。時(shí)鐘頻率越高,轉(zhuǎn)換時(shí)間越短。DDS的頻率轉(zhuǎn)換時(shí)間可達(dá)納秒數(shù)量級(jí),比使用其它的頻率合成方法都要短數(shù)個(gè)數(shù)量級(jí)。

(3)頻率分辨率極高

若時(shí)鐘fs的頻率不變,DDS的頻率分辨率就是則相位累加器的位數(shù)N決定。只要增加相位累加器的位數(shù)N即可獲得任意小的頻率分辨率。目前,大多數(shù)DDS的分辨率在1Hz數(shù)量級(jí),許多小于1mHz甚至更小。

(4)相位變化連續(xù)

改變DDS輸出頻率,實(shí)際上改變的每一個(gè)時(shí)鐘周期的相位增量,相位函數(shù)的曲線是連續(xù)的,只是在改變頻率的瞬間其頻率發(fā)生了突變,因而保持了信號(hào)相位的連續(xù)性。

(5)輸出波形的靈活性

只要在DDS內(nèi)部加上相應(yīng)控制如調(diào)頻控制FM、調(diào)相控制PM和調(diào)幅控制AM,即可以方便靈活地實(shí)現(xiàn)調(diào)頻、調(diào)相和調(diào)幅功能,產(chǎn)生FSK、PSK、ASK和MSK等信號(hào)。另外,只要在DDS的波形存儲(chǔ)器存放不同波形數(shù)據(jù),就可以實(shí)現(xiàn)各種波形輸出,如三角波、鋸齒波和矩形波甚至是任意的波形。當(dāng)DDS的波形存儲(chǔ)器分別存放正弦和余弦函數(shù)表時(shí),既可得到正交的兩路輸出。

(6)其他優(yōu)點(diǎn)

由于DDS中幾乎所有部件都屬于數(shù)字電路,易于集成,功耗低、體積小、重量輕、可靠性高,且易于程控,使用相當(dāng)靈活,因此性價(jià)比極高。

DDS也有局限性,主要表現(xiàn)在:

(1)輸出頻帶范圍有限

由于DDS內(nèi)部DAC和波形存儲(chǔ)器(ROM)的工作速度限制,使得DDS輸出的最高頻有限。目前市場(chǎng)上采用CMOS、TTL、ECL工藝制作的DDS工習(xí)片,工作頻率一般在幾十MHz至400MHz左右。采用GaAs工藝的DDS芯片工作頻率可達(dá)2GHz左右。

(2)輸出雜散大

由于DDS采用全數(shù)字結(jié)構(gòu),不可避免地引入了雜散。其來(lái)源主要有三個(gè):相位累加器相位舍位誤差造成的雜散;幅度量化誤差(由存儲(chǔ)器有限字長(zhǎng)引起)造成的雜散和DAC非理想特性造成的雜散。

2 實(shí)現(xiàn)DDS的三種技術(shù)方案

2.1 采用高性能DDS單片電路的解決方案

隨著微電子技術(shù)的飛速發(fā)展,目前高超 性能優(yōu)良的DDS產(chǎn)品不斷推出,主要有Qualcomm、AD、Sciteg和Stanford等公司單片電路(monolithic)。Qualcomm公司推出了DDS系列Q2220、Q2230、Q2334、Q2240、Q2368,其中Q2368的時(shí)鐘頻率為130MHz,分辨率為0.03Hz,雜散控制為-76dBc,變頻時(shí)間為0.1μs;美國(guó)AD公司也相繼推出了他們的DDS系列:AD9850、AD9851、可以實(shí)現(xiàn)線性調(diào)頻的AD9852、兩路正交輸出的AD9854以及以DDS為核心的QPSK調(diào)制器AD9853、數(shù)字上變頻器AD9856和AD9857.AD公司的DDS系列產(chǎn)品以其較高的性能價(jià)格比,目前取得了極為廣泛的應(yīng)用。AD公司的常用DDS芯片選用列表見(jiàn)表1.下面僅對(duì)比較常用的AD9850芯片作一簡(jiǎn)單介紹。

表1 AD公司的常用DDS芯片選用列表

型 號(hào) 最大工作(MHz) 工作電壓(V) 最大功耗(mw) 備 注

AD9832 25 3.3/5 120 小型封裝,串行輸入,內(nèi)置D/A轉(zhuǎn)換器。

AD9831 25 3.3/5 120 低電壓,經(jīng)濟(jì),內(nèi)置D/A轉(zhuǎn)換器。

AD9833 25 2.5~5.5 20 10個(gè)管腳的uSOIC封裝。

AD9834 50 2.5~5.5 25 20個(gè)管腳的TSSOP封裝并內(nèi)置比較器。

AD9835 50 5 200 經(jīng)濟(jì),小型封裝,串行輸入,內(nèi)置D/A轉(zhuǎn)換器。

AD9830 50 5 300 經(jīng)濟(jì),并行輸入,內(nèi)置D/A轉(zhuǎn)換器。

AD9850 125 3.3/5 480 內(nèi)置比較器和D/A轉(zhuǎn)換器。

AD9853 165 3.3/5 1150 可編程數(shù)字QPSK/16-QAM調(diào)制器。

AD9851 180 3/3.3/5 650 內(nèi)置比較器、D/A轉(zhuǎn)換器和時(shí)鐘6倍頻器。

AD9852 300 3.3 1200 內(nèi)置12位的D/A轉(zhuǎn)換器、高速比較器、線性調(diào)頻和可編程參考時(shí)鐘倍頻器。

AD9854 300 3.3 1200 內(nèi)置12位兩路正交D/A轉(zhuǎn)換器、高速比較器和可編程參考時(shí)鐘倍頻器。

AD9858 1000 3.3 2000 內(nèi)置10位的D/A轉(zhuǎn)換器、150MHz相頻檢測(cè)器、充電汞和2GHz混頻器。

AD9850是AD公司采用先進(jìn)的DDS技術(shù)1996年推出的高集成度DDS頻率合成器,它內(nèi)部包括可編程DDS系統(tǒng)、高性能DAC及高速比較器,能實(shí)現(xiàn)全數(shù)字編程控制的頻率合成器和時(shí)鐘發(fā)生器。接上精密時(shí)鐘源,AD9850可產(chǎn)生一個(gè)頻譜純凈、頻率和相位都可編程控制的模擬正弦波輸出。此正弦波可直接用作頻率信號(hào)源或轉(zhuǎn)換成方波用作時(shí)鐘輸出。AD9850接口控制簡(jiǎn)單,可以用8位并行口或串行口經(jīng)、相位等控制數(shù)據(jù)。32位頻率控制字,在125MHz時(shí)鐘下,輸出頻率分產(chǎn)率達(dá)0.029Hz。先進(jìn)的CMOS工藝使AD9850不僅性能指標(biāo)一流,而且功耗少,在3.3V供電時(shí),功耗僅為155mW。擴(kuò)展工業(yè)級(jí)溫度范圍為-40~+85攝氏度,其封裝是28引腳的SSOP表面封裝。

AD9850采用32位相位累加器,截?cái)喑?4位,輸入正弦查詢表,查詢表輸出截?cái)喑?0位,輸入到DAC。DAC輸出兩個(gè)互補(bǔ)的模擬電流,接到濾波器上。調(diào)節(jié)DAC滿量程輸出電流,需外接一個(gè)電阻Rset,其調(diào)節(jié)關(guān)系是Iset=32(1.248V/Rset),滿量程電流為10~20mA。

2.2 采用低頻正弦波DDS單片電路的解決方案

Micro Linear公司的電源管理事業(yè)部推出低頻正弦波DDS單片電路ML2035以其價(jià)格低廉、使用簡(jiǎn)單得到廣泛應(yīng)用。ML2035特性:(1)輸出頻率為直流到25kHz,在時(shí)鐘輸入為12.352MHz野外頻率分辨率可達(dá)到1.5Hz(-0.75~+0.75Hz),輸出正弦波信號(hào)的峰-峰值為Vcc;(2)高度集成化,無(wú)需或僅需極少的外接元件支持,自帶3~12MHz晶體振蕩電路;(3)兼容的3線SPI串行輸入口,帶雙緩沖,能方便地配合單片機(jī)使用;(4)增益誤差和總諧波失真很低。

ML2035為DIP-8封裝,各引腳功能如下:

(1)Vss:-5V電源;

(2)SCK:串行時(shí)鐘輸入,在上升沿將串行數(shù)據(jù)鎖入16位移位寄存器;

(3)SID:串行數(shù)據(jù)輸入,該串行數(shù)據(jù)為頻率控制字,決定6腳輸出的頻率;

(4)LATI:串行數(shù)據(jù)鎖存,在下降沿將頻率控制字鎖入16位數(shù)據(jù)鎖存器;

(5)Vcc:+5電源;

(6)Vout:模擬信號(hào)輸出;

(7)GND:公共地,輸入、輸出均以此點(diǎn)作為參考點(diǎn);

(8)CLK IN:時(shí)鐘輸入,可外接時(shí)鐘或石英晶體。

ML2035生成的頻率較低(0~25kHz),一般應(yīng)用于一些需產(chǎn)生的頻率為工頻和音頻的場(chǎng)合。如用2片ML2035產(chǎn)生多頻互控信號(hào),并與AMS3104(多頻接收芯片)或ML2031/2032(音頻檢波器)配合,制作通信系統(tǒng)中的收發(fā)電路等。

可編程正弦波發(fā)生器芯片ML2035設(shè)計(jì)巧妙,具有可編程、使用方便、價(jià)格低廉等優(yōu)點(diǎn),應(yīng)用范圍廣泛。很適合需要低成本、高可靠性的低頻正弦波信號(hào)的場(chǎng)合。

ML2037是新一代低頻正弦波DDS單片電路,生成的最高頻可達(dá)500kHz。

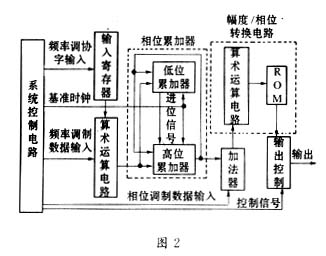

2.3 自行設(shè)計(jì)的基于FPGA芯片的解決方案

DDS技術(shù)的實(shí)現(xiàn)依賴于高速、高性能的數(shù)字器件。可編程邏輯器件以其速度高、規(guī)模在、可編程,以及有強(qiáng)大EDA軟件支持等特性,十分適合實(shí)現(xiàn)DDS技術(shù)。Altera是著名的PLD生產(chǎn)廠商,多年來(lái)一直占據(jù)著行業(yè)領(lǐng)先的地位。Altera的PLD具有高性能、高集成度和高性價(jià)比的優(yōu)點(diǎn),此外它還提供了功能全面的開(kāi)發(fā)工具和豐富的IP核、宏功能外它還提供了功能全面的開(kāi)發(fā)工具和豐富的IP核、宏功能庫(kù)等,因此Altera的產(chǎn)品獲得了廣泛的應(yīng)用。Altera的產(chǎn)品有多個(gè)系列,按照推出的先后順序依次為Classic系列、MAX(Multiple Array Matrix)系列、FLEX(Flexible Logic Element Matrix)系列、APEX(Advanced Logic Element Matrix)系列、ACEX系列、Stratix系列以及Cyclone等。

Max+plusII是Altera提供的一個(gè)完整的EDA開(kāi)發(fā)軟件,可完成從設(shè)備輸入、編譯、邏輯綜合、器件適配、設(shè)計(jì)仿真、定時(shí)分析、器件編程的所有過(guò)程。QuartusII是Altera近幾年來(lái)推出的新一代可編程邏輯器件設(shè)計(jì)環(huán)境,其功能更為強(qiáng)大。

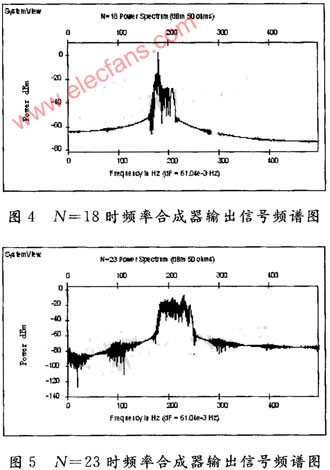

用Max+plusII設(shè)計(jì)DDS系統(tǒng)數(shù)字部分最簡(jiǎn)單的方法是采用原理圖輸入。相位累加器調(diào)用lmp_add_sub加減法器模擬,相位累加器的好壞將直接影響到整個(gè)系統(tǒng)的速度,采用流水線技術(shù)能大幅度地提升速度。波形存儲(chǔ)器(ROM)通過(guò)調(diào)用lpm_rom元件實(shí)現(xiàn),其LPM_FILE的值*.mif是一個(gè)存放波形幅值的文件。波形存儲(chǔ)器設(shè)計(jì)主要考慮的問(wèn)題是其容量的大小,利用波形幅值的奇、偶對(duì)稱特性,可以節(jié)省3/4的資源,這是非常可觀的。為了進(jìn)一步優(yōu)化速度的設(shè)計(jì),可以選擇菜單Assign|Globan Project Logic Synthesis的選項(xiàng)Optimize10(速度),并設(shè)定Global Project Logic Synthesis Style為FAST,經(jīng)寄存器性能分析最高頻率達(dá)到100MHz以上。用FPGA實(shí)現(xiàn)的DDS能工用在如此之高的頻率主要依賴于FPGA先進(jìn)的結(jié)構(gòu)特點(diǎn)。

雖然有的專用DDS芯片的功能也比較多,但控制方式卻是固定的,因此不一定是我們所需要的。而利用FPGA則可以根據(jù)需要方便地實(shí)現(xiàn)各種比較復(fù)雜的調(diào)頻、調(diào)相和調(diào)幅功能,具有良好的實(shí)用性。就可成信號(hào)質(zhì)量而言,專用DDS芯片由于采用特定的集成工藝,內(nèi)部數(shù)字信號(hào)抖動(dòng)很小,可以輸出高質(zhì)量的模擬信號(hào);利用FPGA也能輸出較高質(zhì)量的信號(hào),雖然達(dá)不到專用DDS芯片的水平,但信號(hào)精度誤差在允許范圍之內(nèi)。

DDS問(wèn)世之初,構(gòu)成DDS元器件的速度的限制和數(shù)字化引起的噪聲這兩個(gè)主要缺點(diǎn)阻礙了DDS的發(fā)展與實(shí)際應(yīng)用。近幾年超高速數(shù)字電路的發(fā)展以及對(duì)DDS的深入研究,DDS的最高工作頻率以及噪聲性能已接近并達(dá)到鎖相頻率合成器相當(dāng)?shù)乃健kS著這種頻率合成技術(shù)的發(fā)展,現(xiàn)已廣泛應(yīng)用于通訊、導(dǎo)航、雷達(dá)、遙控遙測(cè)、電子對(duì)抗以及現(xiàn)代化的儀器儀表工業(yè)等領(lǐng)域。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論