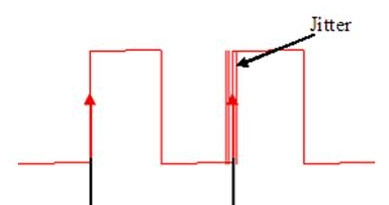

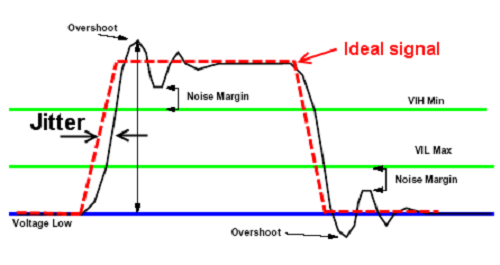

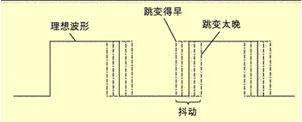

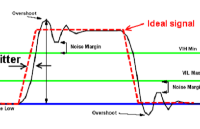

近年來,抖動(Jitter)已經成為通信工程師非常重視的信號特征。在數字系統中,時鐘頻率正在變得越來越高。隨著速率的升組,在上升沿或是下降沿哪性是微小的變化也變得越來越重要。因為時鐘或數據的抖動會影響到數據的完整性、建立時間和保持時間。并且在考慮信號速率與傳輸距離之間的折中時,抖動也成為必須考慮的因素。

抖動會使數字電路的傳輸性能惡化,由于信號上升沿或是下降沿在時間軸上的正確位置被取代,在數據再生的時候,數據比特流中就會引入錯誤。在合并了緩沖存儲器和相位比較器的數字儀表中,由于數據溢出或是損耗,錯誤就會引入到數字信號中。此外,在數模變換電路中,時鐘信號的相位調制會使恢復出的采樣信號惡化,這在傳輸編碼的寬帶信號時會造成問題。

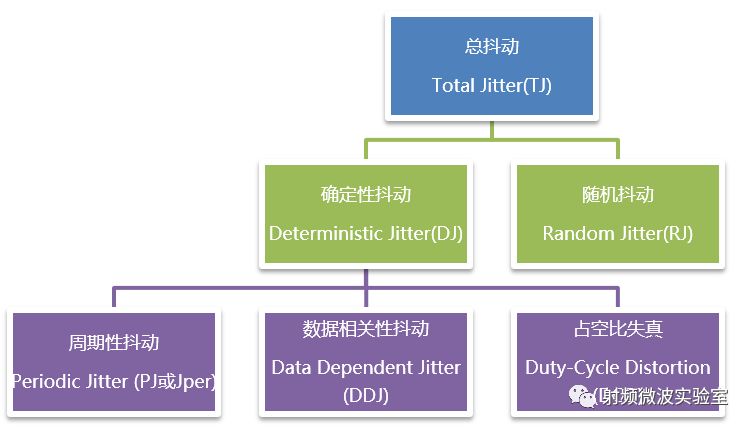

抖動分為系統抖動和隨機抖動。

(1)系統抖動是在信號再生電路時間上不準,或是碼是串擾,或是在幅頻轉換中的不準確的電纜均衡造成的。系統抖動取決于系統的性能。

(2)隨機抖動來源于內部或是外部的干擾信號,如噪聲、串擾、反射等。隨機抖動與傳輸信號的系統無關。

系統抖動與不同的脈沖再生電路的脈沖的模式有關,會連續地積累。隨機抖動則與脈沖再生電路的脈沖模式無關,而且也不會連續地積累;在大多數低速率的數字系統中,系統抖動占主導地位;而在高速系統中,隨機抖動變得越來越重要,甚至會占據主導地位。

干擾性的抖動可以利用信號再生電路劃中利用“去抖動”電路來減弱其影響。這種“去抖動”電路來減弱其影響。這種“去抖動”電路包括了一個帶有窄帶相位平滑電路的信號緩沖器。信號再生電路只能將抖動頻率高于時鐘再生電路的截止頻率的抖動成分減小,而低頻的抖動成分則仍然會出現在輸出信號或是信號再生電路中。在這種情況下,抖動被傳輸到輸出信號中,信號再生電路此時就象是一個低通濾波器。

抖動測量方法

傳統的抖動測量采用模擬測試的方法。圖1給出了傳統模擬測量方法的原理框圖,它是將數據信號與基準時鐘信號相比較,使用相位探測器的平均輸出。模擬測量方法帶來了很多問題,這都是因為相位探測器將相位表達成一個模擬電壓引起的。

以下是用模擬方法測試抖動的缺點:

*時鐘恢復限制了抖動測量的帶寬;

*時間恢復由于自由運行頻率的偏移引入了抖動噪聲;

*大動態范圍要求大頻率分割,導致產生了起出相位探測器范圍的低頻脈沖,進一步限制了測量的帶寬;

*模擬電壓受制于由噪聲和寄生電容產生的負面影響;

*模擬電壓的范圍受制于電源電壓的范圍;

*基準恢復由于其帶寬小獲得鎖相很慢。

??? 隨著DSP技術、ADC應用技術和ASIC技術的發展,抖動分析跟隨著科技從模擬到數字的轉變進程,發展了基于數字分析的抖動測量方法。基于數字的抖動分析方法有先進得多的特性,能使工程師們為下一代設計的測試和分析作更充分的準備。

下面圖2給出了基于數字分析的抖動測量方法的原理框圖。這里的目標是將每個NRZ沿用二進制數作時間標記,其中計數器最低位(LSB)權值就是時間間隔分辨率。時間間隔計數器完成時間標記功能,通過數字處理標記出抖動大小,再經過數字濾波器提供抖動測量所需的高通和低通濾波。在濾波過程中,可實現分辨率中兩個最佳位。抖動得到進一步的處理以檢測峰峰值、真有效值或其它參數,比如頻譜容量。

數字化的抖動測量有以下幾個優點:

*具有更寬的帶寬和更低的噪聲,因為它不需要時鐘恢復。

*具有更寬的帶寬和更光滑的頻率響應,因為數字相位探測器將每個NRZ沿以時間標記(不需要對模擬脈沖作平均處理)。

*具有更低的抖動噪聲,因為數字時間標記不受噪聲的影響。

*增益誤差率只有0.01%,因為信號處理是完全數字化的。

*動態范圍超過4000UIp-p,同時保持0.01UI的分辨率。

*測量時沒有延時,因為不使用鎖相環信號去獲取時鐘。

數字式抖動測試儀的研制

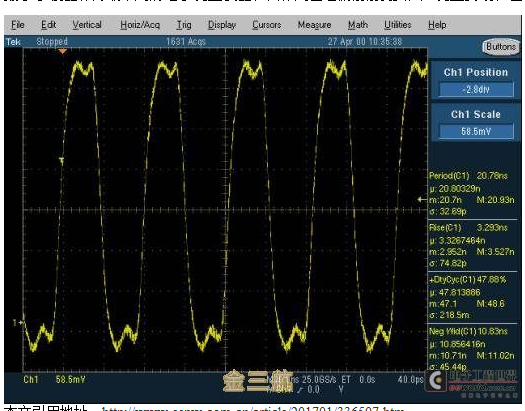

數字式抖動測試儀的基本要求是完成對2.048MHz的鎖相時鐘進行相位抖動測試,具體要求按ITU-TG.823建議執行。設計方案采用數字方法測試抖動。數字抖動測試方法中關鍵的就是計數器的設計,本設計選用的計數器的計數時鐘頻率為100MHz。但是為了保證測試抖動的精度要求,對于100MHz記數產生的誤差信號,專門設計了誤差脈沖展寬電路,以提高測試精度。圖3給出了數字式抖動測試儀的功能框圖。

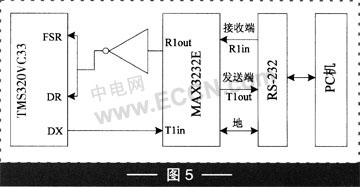

研制的抖動測試儀主要包括以下模塊:時鐘記數、脈沖展寬、數據存儲、數據處理。其中除了脈沖展寬模塊是模擬電路外,其余的3個模塊都是數字電路,所以該設計是一種數字與模擬的混合電路。在設計中,考慮到算法的復雜性和靈活性,開發時間的緊迫性以及系統的要求,選用了德州儀器(TI)的TMS320F206。

DSP選擇

TMS320F206是德州儀器公司用靜態CMOS技術集成的DSP芯片,屬于TMS320C2000系列。這是一種低功耗器件,采用了改進的哈佛結構,有1條程序總線和3條數據總線,有高度并行性的算術邏輯單元ALU、專用硬件邏輯、片內存儲器、片內外設和高度專業化的指令集,從而使該芯片速度高、操作靈活。TMS320F206有224K的尋址能力、3個外部中斷、1個同步串口和一個異步串口,最高時鐘為40MHz。由于每秒需處理數據2Mbit,每個符號采樣兩次,所以實際數據速率是4Mbps。通過其算法來估計其運算量,40MIPS的處理能力完全可以滿足其要求。在設計中使用了1個外部中斷,一個異步串口。異步串口和PC機的串口相連接,將DSP計算結果送回到PC機顯示。

時鐘記數模塊

該模塊主要作用有以下幾個:

①對二分頻后的2MHz時鐘信號用100MHz的時鐘進行記數;

②用100MHz時鐘對2MHz信號記數,產生誤差脈沖;

③對展寬后的誤差脈沖用100MHz的時鐘進行記數;

④產生與數據存儲模塊接口的寫時鐘和寫使能信號;

⑤將2MHz的記數值和展寬的誤差脈沖記數值通過一路8位的數據總線分時輸出。

此模塊的設計主要是用一塊XILINX公司的CPLD XC95108來完成的。

脈沖展寬模塊

脈沖展寬模塊是為了提高測試抖動的精度,這是本設計中非常關鍵的一個模塊。本設計測試抖動其實就是精確地測試出每個周期的時間,只有測試的時間精度提高,最終測試抖動才能達到要求的精度。若無脈沖展寬電路,僅用100MHz的時鐘記數的話,則單個周期的測時的最大誤差將會是20ns,這樣根本無法滿足抖動測試的精度要求。

為了測出小于度量單位的一個物理量的值,我們很容易地想到只要將該物理量放大一個固定的倍數后,使該放大后的物理量可測,此時只要測出該物理量后除以該放大倍數,即可得到原先的物理量的值。該模塊的設計就利用了這樣的思路。具體是利用LM234產生兩個恒流源,分別做為一個電容的充電電流和放電電流。利用充放電電流的不同產生斜率不同的充電曲線,再與一參考電壓進行比較,即可得到一展寬的脈沖。具體的脈沖展寬電路是用兩個三級管完成充放電工作和比較電路。三級管的型號是2SC3357,2SC3357是高頻三級管,其工作頻率可達到2GHz。選用高頻三級管對此設計相當重要,因為要測的誤差脈沖其時間只有幾個ns。

數據存儲模塊

數據存儲模塊主要是作為時鐘記數模塊所記數據的緩沖器,在時鐘記數模塊和數據處理模塊之間充當接口。正如前面所介紹的,選用了一片選進先出(FIFO)芯片,型號是IDT72230。此型號的FIFO具有2K×8的存儲空間。在FIFO的數據全滿后,由IDT72230的FF(全滿標志引腳)向數據處理模塊發送中斷請求信號。而數據處理模塊中的DSP會從FIFO中將這2K數據讀出來。

數據處理模塊

數據處理模塊以DSP為核心,來對記數器記得的值進行處理,最終算得Jitter的值。DSP中用到了中斷口IT1,當FIFO滿時,從FIFO中讀出2K個數據。而DSP與外部的通信則用的是異步串口。

調試

由于系統工作于較高的頻率,計數器為100MHz,DSP為40MHz,DSP的外圍設備一般為20MHz,最高為40MHz,因而在系統設計中,必須注意高頻影響。

在布線時,特意把數據和地址成組布線,以降低對其它信號的影響。對一些關鍵的控制線。如存儲器讀寫信號和FIFO讀寫信號,在其兩邊都加上了地線保護特別是FIFO的讀寫信號,由于其對干擾特別敏感。對一些較長的引線,可串接一個30Ω的小電阻或加終端匹配以減小反射。

在軟件設計中,采用C語言和匯編語言混合編程。具體的編程方法可查閱DSP的手冊。TI公司還提供了一個運行庫(RuntimeLib)。用TI公司的JATG調試器進行調試時,在DSP程序中調用運行庫的函數,可以打開PC機上的文件獲取數據,或將DSP的數據傳入PC機并存入文件,或通過PC機鍵盤向DSP傳遞信息和發送命令,從而為調試帶來了極大的方便。

由于在本設計中采用了DSP技術,使得開發的周期大為縮減,系統的靈活性也大大增強。隨著數字處理芯片(DSP)處理速率的加快,外圍通訊能力的加強,以及數字信號處理的實時性的需要,其應用范圍必將越來越廣泛。

電子發燒友App

電子發燒友App

評論