基于TMS320C6201 DSP的視頻圖像語音傳輸系統(tǒng)的硬件設計

隨著科學技術的高速發(fā)展,視頻圖像和語音數(shù)字化處理在軍事、科研、工農(nóng)業(yè)生產(chǎn)、醫(yī)療衛(wèi)生等領域的應用越來越廣泛。早期的糧情監(jiān)測主要是基于對糧倉溫度、濕度的采集觀測。隨著糧情系統(tǒng)的進一步完善,人們提出了更高要求,希望對糧倉內部進行實時圖像語音監(jiān)控,進一步加強對蟲害和火災觀測和預防。本文所采用的基于TMS320C6201的視頻圖像語音傳輸系統(tǒng)就是應用于糧情的監(jiān)測,在滿足以上要求的前提下設計完成的。

圖像語音的壓縮傳輸系統(tǒng)有二種基本的實現(xiàn)方法:一種是基于微機實現(xiàn),圖像語音處理系統(tǒng)通過PCI總線以插卡的形式集成在微機系統(tǒng)中,數(shù)據(jù)通過PCI總線或卡上所帶的接口進行交換和傳輸;另一種是脫離了微機而獨立運行,利用微處理芯片對圖像語音進行數(shù)字化壓縮傳輸。本文介紹的設計采用了后一種方法。

1? 系統(tǒng)的組成和基本原理

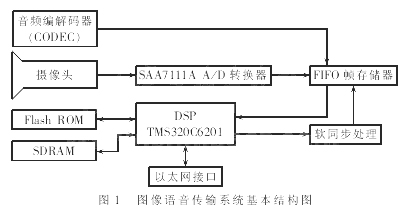

一個完整的視頻圖像語音傳輸系統(tǒng)不但要具備對圖像語音信號的采集功能,還要求完成對采集上來的圖像語音信號的分析及處理算法(如圖像壓縮等),最后采用一定的媒質將處理好的信號傳輸?shù)浇K端主機顯示。視頻圖像語音信號的分析及處理算法的運算量很大,同時又要滿足實時顯示的要求,因此采用了高速DSP芯片作為數(shù)據(jù)核心的處理單元。系統(tǒng)的基本結構模型如圖1所示。

2? 硬件結構

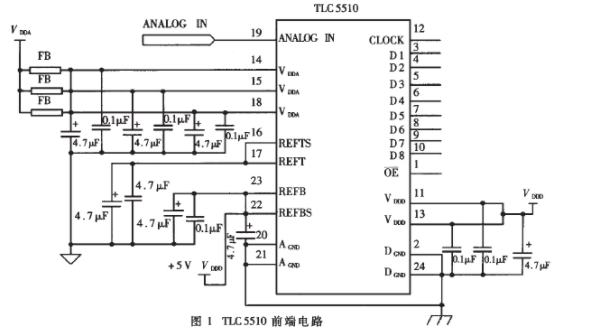

2.1 模擬視頻輸入接口設計

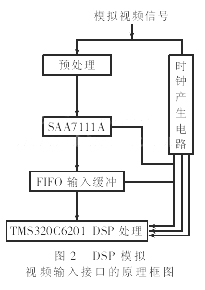

(1)視頻采樣要求。模擬視頻輸入接口電路的作用是對輸入的模擬視頻信號進行預處理,并將其數(shù)字化。視頻采樣有2個重要指標:采樣分辨率和采樣頻率。采樣分辨率代表圖像灰度量化的等級,位數(shù)越多,圖像層次越豐富,同時圖像數(shù)據(jù)量也越大;采樣頻率決定可數(shù)字化后圖像的空間分辨率,為了不失真,它必須大于模擬視頻信號的頻譜中最高頻率的2倍。另外,還要求模擬視頻輸入接口所引入的系統(tǒng)噪聲最小。DSP模擬視頻輸入接口的原理框圖如圖2所示。

(2)模擬視頻解碼模塊。視頻解碼模塊的作用是將復合視頻、YC分量等模擬視頻信號進行A/D轉換,提取其中的同步和時鐘信號,所有轉換電路均集中在一塊芯片內。根據(jù)以上要求,選擇Philips公司生產(chǎn)的可編程的數(shù)字視頻A/D變換器SAA7111A,它有4路模擬輸入和2路模擬信號處理通道,可以通過編程選擇信號制式。輸出信號可以是YUV411(12位)、YUV422(16位)、YUV422(CCIR-656)(8位)、RGB(5、6和5)(16位)或RGB(8、8和8)(24位)格式。系統(tǒng)通過I2C總線對SAA7111A編程,完成初始配置工作。來自攝像頭的模擬信號,首先在模擬信號控制下,進行信號箝位、模擬放大、反混淆濾波、A/D轉換,然后將得到的8位亮度信號和8位色度信號分別送往亮度處理電路和色度處理電路進行處理,產(chǎn)生16位的YUV信號。Y(7:0)為8位數(shù)字亮度信號,UV(7:0)為不同顏色(B-Y和R-Y)復用信號。信號輸出格式由I2C總線控制(YUV信號輸出格式由I2C總線控制電路決定),幀時序由HREF信號控制。在系統(tǒng)中將采用帶有I2C接口的、與51系列兼容的單片機T89C51IC2對SAA7111A進行控制,即對模擬視頻前端SAA7111A的采樣率、箝位電平、鎖相環(huán)等進行編程設置,以使整個視頻輸入接口電路按照預先設計的方式工作。

(3)采用FIFO作為實時圖像數(shù)據(jù)輸入緩沖器。從性能上來說,普通型的幀存儲體在采集的同時不能讀取采集數(shù)據(jù)。雖然采用雙端口RAM也可以解決并發(fā)訪問的問題,但它所必需的地址譯碼和占用大段的主存儲器映射空間(或繁雜的頁面切換)是不可忽視的實際問題。從對采集到的數(shù)據(jù)的處理方式可以看出,對于單純采集應用(不需要對數(shù)據(jù)做諸如疊加等預處理工作),其系統(tǒng)緩存單元在結構上相當于先進先出(FIFO)隊列,即按信號時間順序先采集的數(shù)據(jù)先被主處理芯片讀取及處理。所以采用專門的FIFO芯片可去掉復雜的緩存器幀內地址譯碼電路,大大簡化了系統(tǒng)設計。FIFO(IDT72V3640)用于向TMS320C6201傳輸經(jīng)SAA7111A轉換后的16位實時圖像數(shù)據(jù)VPO(0:15)。FIFO不存在地址線的問題,所以不用連接地址線。

2.2 音頻編解碼器的選取

采用Crystal公司的CS4231A芯片作為核心音頻編碼解碼器(CODEC)模塊。CS4231A多媒體芯片為系統(tǒng)提供一個靈活、通用的音頻前端。它是一個16位立體聲器件,包含完整的片上濾波、模擬混音和可編程控制的增益和衰減調節(jié)。CS4231A支持8、9.6、11.025、16、22.05、32、44.1、48kHz等通用的采樣頻率,如此寬范圍的采樣頻率可以適應從電信到音頻的各種應用需求。CS4231A采用頻率分別為16.9344MHz和24.576MHz的2個晶振來作為采樣頻率的時鐘源。

CS4231A同時提供了并行和串行接口,支持DMA及中斷工作方式,因而可以通過多種方式與DSP進行連接。這里采用的是其中最有效的方式:即串行接口傳輸音頻數(shù)據(jù),并行接口傳輸控制信息。CS4231A使用與DSP的McBSP(多通道緩存串行口)相兼容的串行音頻數(shù)據(jù)接口,這種接口方式為串行音頻數(shù)據(jù)提供了一個專用通道而不必占用DSP的EMIF的帶寬。在串行數(shù)據(jù)流中,CS4231A先傳輸左聲道數(shù)據(jù)然后傳輸右聲道數(shù)據(jù),并且傳輸時高位在前(與McBSP的工作方式相兼容)。CS4231A串口通過多路復用芯片CBT3257的4個2選1復用器連接到DSP的McBSP,這一設置使McBSP可以與板上的CS4231A相連,也可以在任一時刻與自己的具體應用子板相連。CS4231A包含1個8位寬度的并行控制/狀態(tài)接口,通過把接口寄存器映射到DSP的EMIF空間來進行控制和狀態(tài)讀取。這樣就使控制接口和音頻數(shù)據(jù)相分離,避免了在單個碼流上的信號復用,簡化了軟件驅動設計。CS4231A是5V器件,DSP是3.3V器件,它們相互連通后得并行控制信號,并且必須通過總線收發(fā)器進行信號轉換。CODEC模塊支持線性和話筒的多路輸入:音頻的放大器用來對話筒輸入信號進行預防和濾波;線性輸入經(jīng)過無源濾波、交流耦合送入CS4231A,輸入插座可以用來連接立體聲源,通過軟件可以獨立控制左、右輸入聲道的選擇和各自的增益。CODEC還包含一個可通過DSP軟件控制衰減的線性輸出。

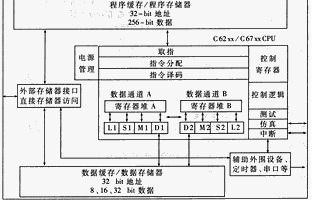

2.3 系統(tǒng)擴展存儲器接口設計

(1)程序存儲及數(shù)據(jù)預置。由于對不同的成像條件,要求其視頻運動估算和圖像處理算法能夠自動適應,所以必須存儲多種算法備選。因此要求選用大容量的存儲器或者多片小容量的存儲器。片外8位或16位的程序存儲器必須配置在TMS320C6201EMIF(外存接口)的CE1空間。這是因為:①系統(tǒng)復位后只能從CE1載入引導程序。②EMIF的4個存儲空間中,只有CE1可以與8位或16位的“窄存儲空間”接口。根據(jù)預存程序和數(shù)據(jù)的大小估計,采用相應容量的Flash ROM。

(2)采用SDRAM擴充系統(tǒng)外部數(shù)據(jù)動態(tài)存儲單元。在高速DSP視頻處理系統(tǒng)中,數(shù)據(jù)存儲器的作用是暫存圖像數(shù)據(jù)。而高速DSP器件TMS320C6201的片上數(shù)據(jù)RAM只有3Mb,無法保證大量數(shù)據(jù)的處理,因此必須擴充片外數(shù)據(jù)存儲器。其原因是:①系統(tǒng)對外部數(shù)據(jù)存儲器的容量要求。假如圖像要求分辨率為320×240,每個采樣點的灰度層為8位,則1幀單色圖像所占的的存儲空間為256KB,三色圖像為3×256KB。如果處理算法涉及到n幀圖像,存儲空間就為n倍。一般情況下,DSP視頻處理系統(tǒng)工作時允許在多種算法之間進行選擇,它所要求的數(shù)據(jù)存儲容量應該以涉及到幀數(shù)最多的算法來估計。②視頻圖像處理過程中圖像數(shù)據(jù)的存放安排。根據(jù)本系統(tǒng)的特點,在內部數(shù)據(jù)RAM和片外數(shù)據(jù)RAM的構成中,為了獲得較快的處理速度,必須注意數(shù)據(jù)的存放位置。這里,針對視頻圖像處理算法的性質給出存放數(shù)據(jù)的原則是:(a)幀內處理算法。處理時所用到的只是當前幀的一部分數(shù)據(jù)。需要存放的數(shù)據(jù)量很小,此時待處理以及已處理的視頻數(shù)據(jù)可以同時存放于片上RAM。(b)幀間處理算法。涉及到的數(shù)據(jù)量超過2幀以上時,則待處理的數(shù)據(jù)及處理過的數(shù)據(jù)均存于SDRAM,片內RAM只存放運算的中間結果。(c)片上數(shù)據(jù)的存放應注意地址的沖突問題。③SDRAM型號的選取。出于為系統(tǒng)圖像壓縮處理充分預留空間的需要,選用型號為MT48LC8M16A2(16MB)的SDRAM,根據(jù)DSP數(shù)據(jù)線為32位寬,選用2片MT48LC8M16A2進行擴展,總的擴展存儲容量為32MB。

2.4 系統(tǒng)以太網(wǎng)接口設計

本系統(tǒng)采用以太網(wǎng)作為傳輸介質。但目前還未有自帶以太網(wǎng)接口的DSP。所以采用以太網(wǎng)控制器RTL8019AS與DSP構成以太網(wǎng)互連接口。

RTL8019AS是***Realtek公司生產(chǎn)的以太網(wǎng)控制器,支持IEEE802.3;支持8位或16位數(shù)據(jù)總線;內置16KB的SRAM,用于收發(fā)緩沖;全雙工,收發(fā)同時達到10Mbps;支持10Base5、10Base2、10BaseT,并能自動檢測所連接的介質,在ISA總線網(wǎng)卡中占有相當比例。RTL8019AS與主機有3種接口模式:跳線模式、PnP模式和RT模式。

為了簡化DSP網(wǎng)絡接口的軟、硬件設計,不使用遠程自舉加載功能,并且選用跳線接口模式。用DSP的擴展I/O口代替跳線器對RTL8019AS進行初始化配置。這樣既省去了93C46的功能,又避免了跳線器更改資源配置的麻煩。RTL8019AS的總線接口與ISA總線兼容。雖然不能與DSP的外部總線直接接口,但是只要進行一些簡單的邏輯變換就可以實現(xiàn)直接接口。另外,DSP的總線電平為3.3V,而RTL8019AS的接口電平為5V,因此二者接口時要使用電平轉換器。

2.5 電源模塊及復位電路的設計

TMS320C6201的電源采用2種電壓供電:即內核電壓1.8V,I/O電壓3.3V。DSP對這2個電壓有上電順序的要求,要求內核電源(CVdd)先于I/O電源(DVdd)上電。為此在電源模塊的選用上,采用二套電源模塊,通過撥碼開關構成互補模式,這樣就能夠保證系統(tǒng)在一套電源模塊失效時還能夠繼續(xù)工作,增強了系統(tǒng)的可靠性。這二套電源模塊分別是:PT公司針對TI公司的DSP生產(chǎn)的電源模塊PT6405B(5V~3.3V)和PT6502B(5V~1.8V),該類型的電源模塊具有穩(wěn)定、額定電流大(3A)等優(yōu)點;另一套是由MAXIM公司生產(chǎn)的、采用帶有同步整流器的DC-DC轉換器MAX1742(輸出電流1A)和MAX1644(輸出電流2A),配合適當?shù)耐鈬娐贩謩e對DSP的I/O和內核供電。

為了保證TMS320C6201芯片在電源低于要求的電平時不會產(chǎn)生不受控制的狀態(tài),系統(tǒng)中應加入電源監(jiān)控電路,以確保DSP在系統(tǒng)加電過程中及電源電壓低于一定門限值時始終處于復位狀態(tài)。監(jiān)控電路采用TI公司的TPS3307-33d(它還可接一手動復位開關)。

3? 結束語

本文設計的基于TMS320C6201的視頻圖像語音傳輸系統(tǒng),與采用專用芯片加FPGA構成的系統(tǒng)比較,其硬件性能有了很大的提高。在軟件實現(xiàn)上也更加靈活多樣、修改方便。該系統(tǒng)結構緊湊,可靠性高,實時性強,能夠廣泛地運用于軍事、科研、工農(nóng)業(yè)生產(chǎn)和醫(yī)療衛(wèi)生等領域。

電子發(fā)燒友App

電子發(fā)燒友App

評論