基于雙DSP的實時圖像處理系統

介紹了基于雙DSP的實時圖像處理系統。該系統通過兩片TMS320C6201作為系統計算中心,通過可重構成的FPGA計算系統獲得系統體系機構上最大的靈活性。

??? 關鍵詞:實時圖像處理系統 雙DSP FPGA計算系統

實時圖像處理技術在目標跟蹤、機器人導航、輔助駕駛、智能交通監控中都得到越來越多的應用。由于圖像處理的數據量大,數據處理相關性高,實時的應用環境決定嚴格的幀、場時間限制,因此實時圖像處理系統必須具有強大的運算能力。各種高性能DSP不僅可以滿足運算性能方面的需要,而且由于DSP的可編程性,還可以在硬件一級獲得系統設計的極大靈活性。為了獲得足夠的計算能力,我們以兩片TMS320C6201作為系統的運算中心構筑了實時圖像處理系統;為了獲取最的靈活性,在系統體系機構上采用了一種可重構的FPGA計算系統模型。

TMS320C6x系列DSP是TI公司TMS320家庭中最新推出的產品之一。由于應用一種高性能的先進VLIW(Very Long Instruction Word)的VelociTI TM體系結構,因此可以更好地應用在一些多通道多功能的系統中。

VelociTI TM是一種提高處理器指令級并行程度的先進的VLIW技術。并行機制是DSP的處理性能超過其它超標量結構的處理芯片的力工具,正是由于在指令并行、流水結構、部件并行等方面的并行操作,使得TMS320C6x能夠達到1600MIPS的運行速度。

TMS320C6x系列的DSP芯片結構不同于一般的DSP,屬于類RISC結構,從而使它的C編譯器具有很高的效率,因此稱之為面向C語言結構的DSP芯片。這使得其在絕大多數應用中,可以采用C語言編寫TMS320C6x程序,從而充分利用大量的C描述的算法程序,并獲得遠勝于傳統DSP程序的可維護性、可移植性、可繼承性,縮短開發周期。

2 FPGA計算系統模型

FPGA是二十世紀80年代后期出現的新型的大規模可編程器件,由邏輯單元和互連線網絡兩部分組成,兩者均可編程。邏輯單元能完成一些基本操作。邏輯單元經互連線網絡互連,通過對基本邏輯塊互連線網絡編程,可以實現非常復雜的邏輯功能。由于FPGA是基于SRAM結構的器件,所有可編程邏輯加載在芯片內部的SRAM上,因此可以通過一定的步驟在系統運行時進行編程來改變該器件的功能,從而實現更大的靈活性。

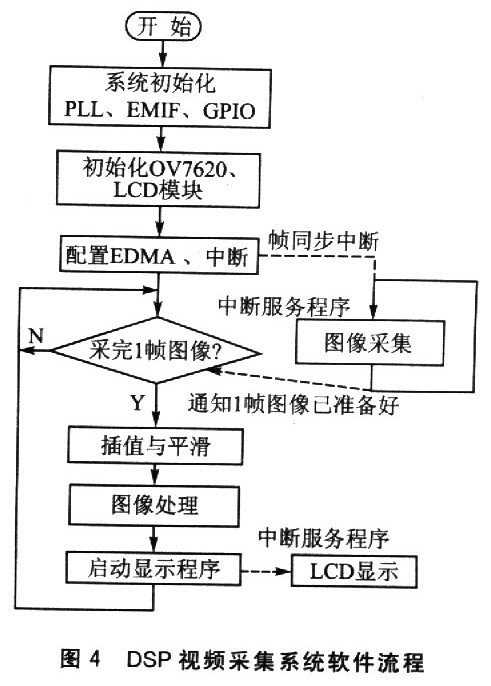

在通常的并行系統設計,微處理器在空間維上是固定的, 而在時間維上是可變的;而連接的專用芯片在空間維和時間維上都是固定的。這樣的系統往往只能適用于特定應用場合下的特定算法。為了使系統具有更加優良的性能和靈活性,隨著可編程器件FPGA的應用深入,一種新的通用處理模塊結構呈現在我們面前——FPGA計算系統結構。圖1給出了抽象的FPGA計算系統模型,該模型由微處理器、FPGA以及存儲器等三部分構成系統的核心。FPGA計算系統就是充分利用FPGA的高集成度和硬件可編程性在系統中用FPGA實現除了必要模塊(如微處理器和存儲器等)之外的其它邏輯和硬件互連,從而使系統具有空間上的可編程性。系統的空間可編程性是FPGA計算系統引入的新特征。它是指通過對FPGA的重新編程和配置來改變系統體系結構等一系列硬件邏輯結構。系統的空間可編程性是系統可重構的前提,它使得硬件系統的設計趨于軟件編程化。然而需要指出的是,由于FPGA內部結構的完全分布性和內部單元的百分之百的互連連通性,系統的硬件互連編程不象由中央處理單元引起的軟件編程那樣可以充分總結指令集。但在具體的系統設計中,可以根據實際的數據流結構進行部分限制,這樣可以為用戶提供一些可選擇的重構方案,方便用戶使用。

而在時間維上是可變的;而連接的專用芯片在空間維和時間維上都是固定的。這樣的系統往往只能適用于特定應用場合下的特定算法。為了使系統具有更加優良的性能和靈活性,隨著可編程器件FPGA的應用深入,一種新的通用處理模塊結構呈現在我們面前——FPGA計算系統結構。圖1給出了抽象的FPGA計算系統模型,該模型由微處理器、FPGA以及存儲器等三部分構成系統的核心。FPGA計算系統就是充分利用FPGA的高集成度和硬件可編程性在系統中用FPGA實現除了必要模塊(如微處理器和存儲器等)之外的其它邏輯和硬件互連,從而使系統具有空間上的可編程性。系統的空間可編程性是FPGA計算系統引入的新特征。它是指通過對FPGA的重新編程和配置來改變系統體系結構等一系列硬件邏輯結構。系統的空間可編程性是系統可重構的前提,它使得硬件系統的設計趨于軟件編程化。然而需要指出的是,由于FPGA內部結構的完全分布性和內部單元的百分之百的互連連通性,系統的硬件互連編程不象由中央處理單元引起的軟件編程那樣可以充分總結指令集。但在具體的系統設計中,可以根據實際的數據流結構進行部分限制,這樣可以為用戶提供一些可選擇的重構方案,方便用戶使用。

3 基于FPGA計算系統模型的雙DSP實時圖像處理系統

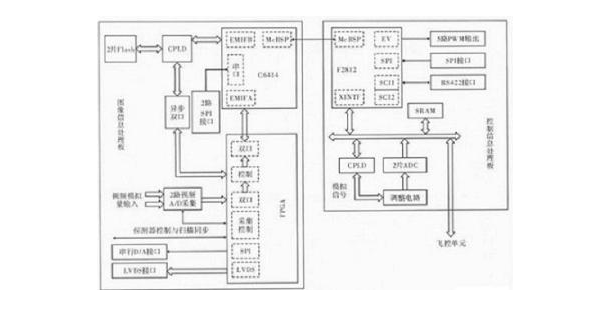

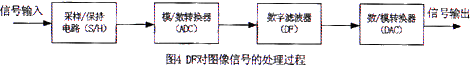

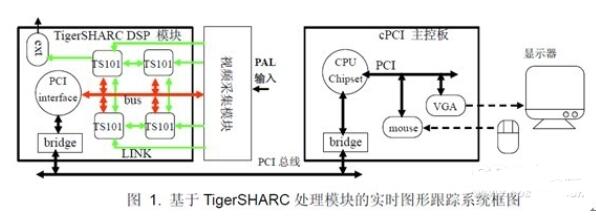

為了盡可能地獲得高性能,我們提出以兩個TMS320C62x為中央處理核心構成雙DSP處理系統,由FPGA(這里采用ALTERA的FLEX系列)實現系統互連。系統分為處理器模塊、FPGS組模塊和各總線接口模塊等,如圖2所示。其中處理器模塊包含TMS320C62x、內存空間以及相應邏輯。處理器作為最小處理單元模塊而存在,可以完成相應的處理子任務。在我們的系統中設備了兩個這樣的處理子任務。在兩個處理模塊都是在系統核心FPGA控制下運行的。而FPGA作為系統中心,負責兩個微處理器互相通信、互相協調以及它們與外界(這里通過主從總線和互連總線)的信息交換。同時,系統處理子任務可以由FPGA直接派發給處理器。靈活的FPGA體系結構設計是該系統有效性的保證。在實際應用中,可以根據系統的任務,通過配置FPGA控制兩個微處理器按流水線方式運行,也可以控制它們按MIMD方式并行處理同一輸入圖像。為了提高數據交換的效率,在FPGA控制下的數據交換中心設置了靈活的系統存儲空間。而這塊存儲空間與DSP的局部存儲空間構成了一種分布共享式的結構。然而不同于一般的分布共享式存儲結構的,我們的系統存儲空間相對獨立,不是直接掛接在各DSP的地址空間中,而是通過兩者的HPI口進行互連。從嚴格意義上講,這種結構不能算分布共享式存儲結構,而應稱之為一種松散的分布共享式存儲結構。 由于并行效率要求,我們將系統存儲空間設置為兩個Bank結構,兩個Bank是獨立控制和運行的,系統的實際框圖見圖3。

由于并行效率要求,我們將系統存儲空間設置為兩個Bank結構,兩個Bank是獨立控制和運行的,系統的實際框圖見圖3。

由于系統的互連、各個接口以及數據通道都是通過FPGA完成,并在FPGA內部實現除一些必要邏輯之外的其它所有邏輯,因此系統的重構非常方便。這是系統設計中的最大特點。另外系統還有其它幾個優點:(1)系統可測性。由于所有的接口邏輯(包括微處理器以及板上其它接口)都由FPGA實現,并且由于系統實現主從接口邏輯,完全可通過軟件獲取系統內部運行的所有狀態。在系統調試階段,可以增加一些測試點和測試狀態字節,相當于將該信息處理子系統在一個優良有數字測試環境下運行,使得系統的可測大大提高;(2)系統可裁減性。由于FPGA的實現完全類似于軟件的編程工作,我們可以使系統設計變為軟件模塊的設計,模塊化設計方法可以使系統具有功能的可裁減性。根據不同應用環境進行不同目標的設計將擁有不同的模塊功能;(3)系統設計的方便性。由于FPGA系統的引入,我們可以改變以往的硬件設計方案和步驟,初步的硬件連線只需關注以往的硬件設計方法和步驟,初步的硬件加線只需關注系統外部特征、微處理器系統的可能控制線性,無需詳細關注更多的細節,而在系統調試時才注意邏輯接口的具體功能,并且都在FPGA上完成,這使得系統設計的周期變短。本系統已成功地應用在智能移動機器人的實時視覺導航系統的,以得了滿意的效果。

電子發燒友App

電子發燒友App

評論