采用TMS320F206控制的同步調制解調器

介紹了一種采用數字信號處理器TMS320F206和調制解調芯片RC56D/SP設計的同步調制解調器。該調制器解調器能在多種信道上實現數據的同步傳輸,具有廣泛的用途。

??? 關鍵詞:調制解調 同步 數字信號處理

隨著數據通信的發展和普及,調制解調器的應用范圍越來越廣。歸結起來,凡是需利用模擬信道實現數據傳輸的場合,都需要用調制解調器作為DCE,完成DTE與線路的連接。在很多場合,例如通過電力線通信專網傳輸各種自動化信息時,要求進行同步傳輸。但目前市售的調制解調器均只支持異步通信。針對這種情況,我們研制了同步調制解調器。該調制解調器選用支持同步通信的RC56D/SP調制解調器芯片組完成調制解調功能,采用TMS320F206數字信號處理器實現有關的智能控制。

1 RC56D/SP及TMS320F206簡介

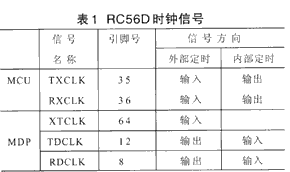

RC56D/SP是Conexant(原Rockwell)公司出品的56k調制解調芯片。RC56D/SP包括一片8bit的微控制器(MCU)和一片數據泵(MDP),通過執行固化在1Mbit(128K×8)RAM和2Mbit(ROM/Flash ROM內的固件來完成操作。該器件采用TCM網格編碼技術,兼容AT命令,支持V.42調制解調器鏈路存取協議(LAPM)和MNP10糾錯協議,支持V.80同步傳輸協議。在同步方式下,發送時鐘可采用內部、外部及從時鐘三種方式,且內置鎖相環具有時鐘提取功能,可從接收的同步數據流里提取與對端發送時鐘完全同頻同相的時鐘信號作為自身及DTE的接收時鐘,該芯片最高可支持33.6K/s的同步速率。

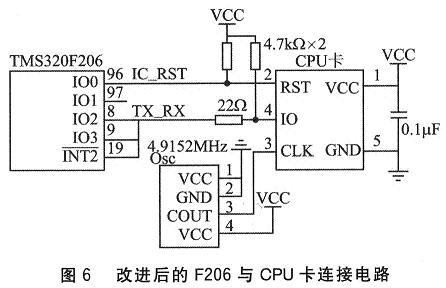

TMS320F206的CPU時鐘頻率為20MHz,具有豐富的片內外資源,且擁有功能強大的異步及同步串行口。

其異步串行口具有最大傳輸速率的全雙工發送和接收操作,數據的傳送通過發送器上的發送引腳(TX)和接收器上的接收引腳(RX)來完成。通過異步串行口控制寄存器(ASPCR)可以將IO0~IO3四個I/O口配置為握手控制信號以改善信號傳輸質量。

其同步串行口的發送和接收均涉及到一個4級先進先出(FIFO)緩沖器。通過減少傳送過程中出現的發送或接收中斷的數量,FIFO緩沖器可減少CPU的開鎖(在發送或接收數據時)。同步串行口的操作時鐘可由內部產生,也可來自一個外部時鐘源。采用內部時鐘方式時,發送和接收操作的最大速率為CPU時鐘頻率除以2.采用外部時鐘源時,數據傳輸速率將隨著外部時鐘源變化。

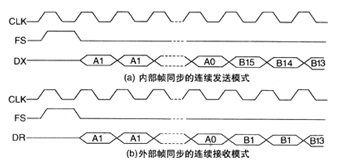

同步串行口的數據發送和接收操作必須上相應的發送幀同步脈沖(FSX)和接收幀同步脈沖(FSR)啟動。FSX既可由內部產生,也可由外部產生。FSR必須由外部產生。

同步串行口有連續及突發兩種操作模式,可支持一系列應用。在連續模式下,只需要一個幀同步脈沖就可以連續發送或接收多個軟件包;在突發模式下,在每一個幀同步脈沖之后只允許發送或接收一個16bit單字。具有內部幀同步的連續發送時序和具有外部幀同步的連續接收時序分別如圖1(a)和圖1(b)所示。

同步串行口具有發送中斷(XINTs)和接收中斷(RINTs)兩個硬件中斷,它通知處理器FIFO緩沖器需要服務。通過對中斷產生條件進行適當的設置,可使數據的發送和接收連續不斷地進行。

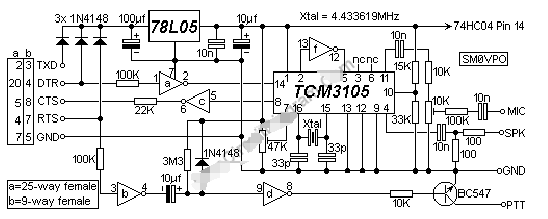

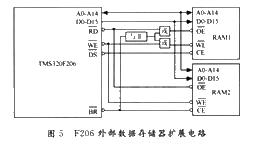

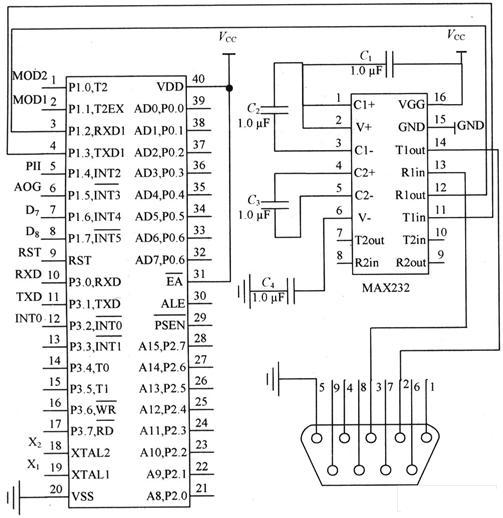

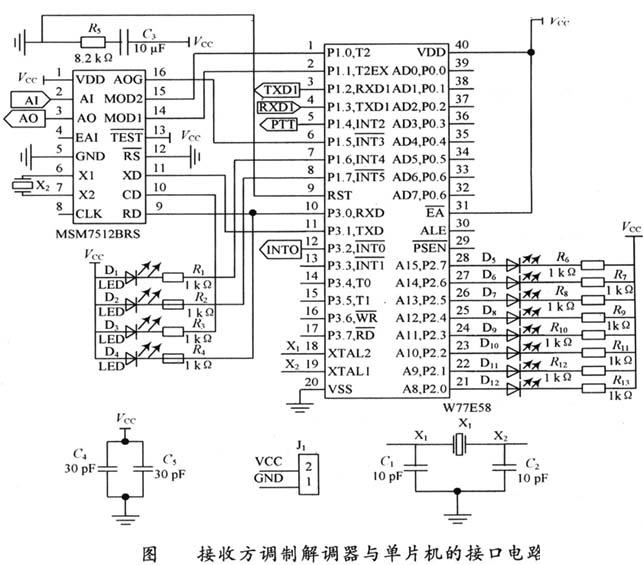

系統硬件電路原理框圖如圖2所示。調制解調器采用異步連接同步傳輸的工作方式,即在異步方式下進行連接,建立連接后進入同步傳輸狀態。由于TMS320F206及MCU都為TTL電平,故它們之間可直接相連。異步串行口及同步串行口具體連線見圖3和圖4。調制解調器異步和同步數據使用MCU上的相同數據口。因此MCU發送引腳上的數據即為從DTE過來將要發送出去的數據,而接收引腳上的數據為已經解調的對端數據,故TMS320F206的異步或同步數據發送(TXD)和接收(RXD)引腳對應相連。由于MCU異步功能僅用于調制解調器的設置及連接,故可不使用流量控制功能,即握手信號可不用。所以將MCU的RTS及DTR引腳接地,使其長期有效。

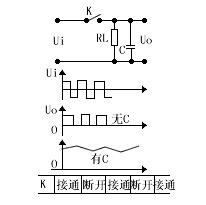

TMS320F206數據發送采用外部時鐘、內部幀同步及連續模式。接收則采用外部時鐘及連接模式,接收幀同步脈沖由MCU控制產生。當調制解調器建立連接且MCU接收到第一幀數據時,將控制脈沖形成電路產生一脈沖寬度與同步接收時鐘周期相同的單個脈沖,啟動TMS320F206接收數據。因系統在無有用數據時也長發一監測信號以保護連接狀態,故除非斷送,數據接收一經啟動就不會停止。TMS320F206的發送時鐘(TXCLK)及接收時鐘(RXCLK)均由調制解調器提供。

調制解調器發送時鐘分為內部、外部及從時鐘三種方式。它們可通過AT&X0(1、2)命令來進行設置。當設置為內部時鐘時,調制解調器發送時鐘由調制解調芯片內部振蕩電路提供。內部振蕩電路可產生300~56kHz之間的任一標稱頻率。采用外部時鐘方式時,外部時鐘XTCLK首先送入MDP、MDP一方面將之作為本芯片的同步發送時鐘,另一方面經片內鎖相環輸出一個與XTCLK同頻同相的時鐘信號TXCLK,并將之送給MCU及TMS320F206作為同步發送時鐘,因為MDP內部鎖相環只能鎖定于任一標稱頻率,所以必須使XTCLK頻率為300~33.6kHz之間的任一標稱頻率。使用從時鐘方式時,調制解調器將采用從接收數據流里提取出來的時鐘作為發送時鐘,即本端發送時鐘與對端發送時鐘相同。本調制解調器發送采用外部時鐘。

調制解調器同步接收時鐘由本端MDP提供。MDP可從接收數據流里提取出與對端發送時鐘完全相同的時鐘信號RXCLK,以其作為自身以及MCD和TMS320F206的接收時鐘。

3 調制解調器工作方式設置

調制解調器缺省工作方式為異瞇方式。若想使其進入同步工作方式,必須通過AT命令進行設置。我們用到的有關同步方式設置的AT命令有以下幾條:+ES、+ESA、&Q1以及&X1。其中+ES命令用于使能或禁止同步傳輸模式。+ESA命令用于對同步傳輸模式一些相關特性進行設置,如是否采用循環冗余碼校驗、是否采用反轉不歸零碼傳輸等。&Q1命令用于控調制解調器為異步連接同步傳送方式,即調制解調器以異步方式進行連接,一旦連通就立即進入同步傳輸方式。&X1命令用于選擇外部時鐘作為調制解調器發送時鐘。

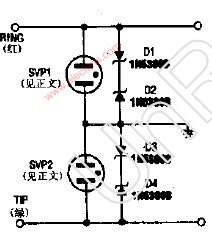

調制解調器的連接過程因系統的應用不同而不同。當經過公用電話交換網進行傳輸時,調制解調器可通過自動應答方式進行連接。這時調制解調器分為主叫端和被叫端。主叫端發起呼叫,即撥通被叫端用戶號碼。被叫端調制解調器通過檢測鈴流啟動應答過程,被叫端自動應答方式可通過ATS0=N(N=1…255)命令來啟動,其中N代表檢測到多少個鈴流信號后啟動應答過程,N=0則禁止自動應答功能。

當系統不經過公用電話交換網進行傳輸時,因線路上無鈴流信號,所以采用偽自動應答方式。所謂偽自動應答方式是指由DSP程序控制調制解調器進行應答,而不是由調制解調器自身啟動應答過程。實現原理如下:在被叫端線路口設計一個雙音多頻(DTMF)信號音檢測電路,當主叫端發起呼叫時,只需撥任一雙音多頻號,該信號音檢測電路檢測到信號音后,即產生一個方波脈沖信號,解發TMS320F206的INT1中斷。TMS320F206進入中斷服務程序后,向調制解調器送入ATA(強制應答)命令,從而啟動應答過程,與對端調制器建立連接。因線路上無撥號音,而調制解調器復位后的缺省狀態需要交換設備提供撥號音才能撥號,因此在對主叫端調制解調器進行初始化時,必須加上ATX1命令。該命令可使調制解調器不需要撥號音便可直接撥號。調制解調器撥號操作可通過ATD***(***代表所撥號碼)命令執行。

4 系統工作流程

TMS320F206程序流程圖如圖5所示。系統工作流程如下:系統上電復位后,TMS320F206首先進行初始化,打開異步口,然后檢測調制解調器是否準備好。若沒準備好,則對調制解調器再次復位;若準備好,則送AT命令進入調制解調器,對調制解調器進行初始化。即命名能調制解調器同步口,將調制解調器設置為異步連接同步傳輸方式,采用外部時鐘以及對同步傳輸械、傳輸速率等相關特性進行設置。同時決定主叫端是否加上ATX1命令以及被叫端是采用何種應答方式。調制解調器每次收到正確AT命令且正確進行相應操作后,會通過異步串口回送OK信號。因此,若TMS320F206收到OK信號,就表明初始化成功。調制解調器初始化完成后,主叫端便撥號啟動呼叫,被叫端進入自動應答或偽自動應答過程。連通后,調制解調器會回送CONNECT信息給TMS320F206。此后TMS320F206便禁止異步口、打開同步口,開始進行同步數據傳輸。

本同步調制解調器研制完成后,曾在專用線路、公用電話線路和電力載線路上進行同步傳輸試驗,都獲得了比較好的傳輸效果。在需要利用模擬信道完成同步傳輸傳務的場合,特別是在接入層,本調制解調器將具有廣泛的用途。

電子發燒友App

電子發燒友App

評論