高速實(shí)時(shí)頻譜儀是對實(shí)時(shí)采集的數(shù)據(jù)進(jìn)行頻譜分析,要達(dá)到這樣的目的,對數(shù)據(jù)采集系統(tǒng)的采樣精度、采樣率和存儲量等指標(biāo)提出了更高的要求。而在高速數(shù)據(jù)采集系統(tǒng)中,ADC在很大程度上決定了系統(tǒng)的整體性能,而它們的性能又受到時(shí)鐘質(zhì)量的影響。

2019-09-02 06:44:39

DSP28335+FPGA+AD7606的數(shù)據(jù)采集系統(tǒng),DSP采用TI公司的TMS320F28335,F(xiàn)PGA使用 ALTERA的Cyclone3 的 EP3C5E144C8N在設(shè)計(jì)的過程中遇到

2016-07-18 16:53:28

DSP28335+FPGA+AD7606的數(shù)據(jù)采集系統(tǒng),DSP采用TI公司的TMS320F28335,F(xiàn)PGA使用 ALTERA的Cyclone3 的 EP3C5E144C8N在設(shè)計(jì)的過程中遇到

2016-07-18 17:13:01

DSP的FPGA的高速數(shù)據(jù)采集系統(tǒng)的研究與設(shè)計(jì),大家可以看看

2015-04-03 21:23:48

高速數(shù)據(jù)采集系統(tǒng)的硬件結(jié)構(gòu)MAX7000系列CPLD及其開發(fā)平臺介紹CPLD在高速數(shù)據(jù)采集系統(tǒng)中的應(yīng)用

2021-04-08 06:11:56

單芯片12位數(shù)據(jù)采集系統(tǒng)

2023-03-28 18:28:42

單芯片12位數(shù)據(jù)采集系統(tǒng)

2023-03-23 07:59:40

《基于ARM與線性CCD的高速數(shù)據(jù)采集系統(tǒng)》

2012-08-16 14:06:55

測量速度和精度。 系統(tǒng)總體設(shè)計(jì)方案 本文提出了一種基于LABVIEW的USB接口高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì),充分利用DSP豐富的片上外設(shè)以及高性能的數(shù)字信號處理能力,將采集的數(shù)據(jù)經(jīng)DSP處理后通過高速

2014-12-16 11:32:57

申請理由:本開發(fā)板為ARM系類,能移植Linux系統(tǒng),可以實(shí)現(xiàn)快速高效的系統(tǒng),并且能實(shí)現(xiàn)數(shù)據(jù)云共享。對于高速數(shù)據(jù)采集系統(tǒng),開發(fā)板的資源可以適用,并且非常實(shí)用。項(xiàng)目描述:高速數(shù)據(jù)采集系統(tǒng)原理:通過高速

2015-07-17 14:43:58

申請理由:使用TI的片子感覺不錯(cuò),CCS的例程很豐富,自己有一塊C2000的板子,但是是最小系統(tǒng),想做一個(gè)數(shù)據(jù)采集系統(tǒng),需要一塊好的開發(fā)板做研發(fā)。項(xiàng)目描述:設(shè)計(jì)基于DSP的高速數(shù)據(jù)采集系統(tǒng)嗎,打算采用C6000的FIFO解決DSP芯片與A/D工作速率不匹配的問題,有效避免數(shù)據(jù)丟失

2015-10-29 14:13:45

TMS320C6748的使用,了解其新特性。2、學(xué)習(xí)利用dsp實(shí)現(xiàn)一些高級濾波算法。3、將dsp與fpga結(jié)合實(shí)現(xiàn)高速數(shù)據(jù)采集。4、分享5篇左右的開發(fā)板使用心得。

2015-10-09 15:10:00

申請理由:借助此平臺完成數(shù)據(jù)的處理項(xiàng)目描述:高速ADC+高密度FPGA+高性能DSP,其中FPGA主要負(fù)責(zé)高速數(shù)據(jù)緩存,并對整個(gè)高速數(shù)據(jù)采集系統(tǒng)進(jìn)行控制;DSP器件擁有很強(qiáng)的數(shù)字信號處理能力和良好

2015-11-06 10:01:48

對數(shù)據(jù)采集與處理系統(tǒng)提出了新的更高的要求,即高速度、高精度和高實(shí)時(shí)性。對數(shù)據(jù)采集與處理系統(tǒng)的設(shè)計(jì),有以下3種方案可供選擇:(1)A/D+DSP方案在傳統(tǒng)的高速信號處理中,大多采用這種方案。將A/D、D

2019-07-05 06:41:27

通用串行總線則具有安裝方便、高帶寬、易擴(kuò)展等優(yōu)點(diǎn),其中USB2.0標(biāo)準(zhǔn)具有480Mbps的最高數(shù)據(jù)傳輸率,這使USB成為本系統(tǒng)所選接口的主要類型。控制方面,傳統(tǒng)數(shù)據(jù)采集通常使用單片機(jī)或DSP作CPU來

2019-07-05 08:23:08

本帖最后由 mr.pengyongche 于 2013-4-30 03:26 編輯

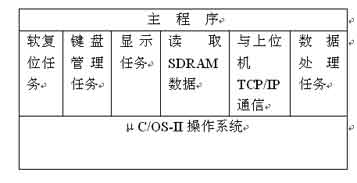

1 引言 數(shù)據(jù)采集系統(tǒng)是通信與信息技術(shù)領(lǐng)域中重要的功能模塊,應(yīng)用廣泛。而傳統(tǒng)的數(shù)據(jù)采集系統(tǒng)大多以單片機(jī)或中規(guī)模數(shù)字電路為核心,其模數(shù)轉(zhuǎn)換器(A/D轉(zhuǎn)換

2011-12-14 10:24:47

基于DSP和現(xiàn)場總線的數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)在電力系統(tǒng)的生產(chǎn)過程中,生產(chǎn)運(yùn)行部門通常有兩方面的考慮:一方面盡量提高設(shè)備與線路的利用率,實(shí)現(xiàn)系統(tǒng)的經(jīng)濟(jì)性;同時(shí)保證電力系統(tǒng)的安全、可靠運(yùn)行,提供高質(zhì)量的電能

2009-12-08 10:28:19

接口,它使電路工作在更加平穩(wěn)、簡潔而易丁控制,同時(shí)也提高了ARM的工作效率。為了提高通信速度,這里采用通用申行總線(USB)技術(shù)米與PC進(jìn)行通信。ARM是用來控制主處理器的數(shù)據(jù)采集,數(shù)據(jù)的計(jì)算和數(shù)據(jù)傳輸。結(jié)果證明,整個(gè)系統(tǒng)能高效運(yùn)作。該系統(tǒng)可應(yīng)用于高速數(shù)據(jù)采集及多路模擬信號的工作環(huán)境下。

2023-09-26 07:41:28

基于FPGA 的DSP 數(shù)據(jù)采集分析系統(tǒng)設(shè)計(jì)

2012-08-20 15:35:41

基于FPGA+DSP的高速數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

2012-06-27 17:23:53

24期摘 要:傳統(tǒng)的數(shù)據(jù)采集系統(tǒng)大都是由ARM+DSP實(shí)現(xiàn)的,雖然DSP的優(yōu)勢在于數(shù)據(jù)處理,但是隨著FPGA技術(shù)的發(fā)展,很多FPGA已經(jīng)可以取代DSP的作用了。尤其是在高速實(shí)時(shí)的數(shù)據(jù)采集領(lǐng)域,采集

2018-05-09 12:09:43

目前,在數(shù)據(jù)采集系統(tǒng)的硬件設(shè)計(jì)方案中,有采用通用單片機(jī)和USB相結(jié)合的方案,也有采用DSP和USB相結(jié)合的方案,前者雖然硬件成本低,但是時(shí)鐘頻率較低,難以滿足數(shù)據(jù)采集系統(tǒng)對速度要求;后者雖然可以實(shí)現(xiàn)

2019-09-05 07:22:57

基于FPGA的高速實(shí)時(shí)數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

2012-08-20 20:00:14

速度和精度。

系統(tǒng)總體設(shè)計(jì)方案

本文提出了一種基于LABVIEW的USB接口高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì),充分利用DSP豐富的片上外設(shè)以及高性能的數(shù)字信號處理能力,將采集的數(shù)據(jù)經(jīng)DSP處理后通過高速USB

2018-12-26 07:00:05

基于PCI-1713和LabVIEW的高速數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

2013-06-01 16:58:57

基于USB總線的高速數(shù)據(jù)采集系統(tǒng)介紹了一種基于USB總線的高速數(shù)據(jù)采集系統(tǒng),討論了USB控制器EZ-USB FX2?CY7C68013?的性能及傳輸方式?給出了該系統(tǒng)的硬件和基于GPIF主控方式實(shí)現(xiàn)

2009-04-11 17:20:15

測量速度和精度。系統(tǒng)總體設(shè)計(jì)方案 本文提出了一種基于LABVIEW的USB接口高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì),充分利用DSP豐富的片上外設(shè)以及高性能的數(shù)字信號處理能力,將采集的數(shù)據(jù)經(jīng)DSP處理后通過高速USB

2019-05-07 09:40:04

本帖最后由 eehome 于 2013-1-5 10:11 編輯

基于labview與dsp串口的數(shù)據(jù)采集系統(tǒng)

2012-05-10 15:28:18

高速連續(xù)數(shù)據(jù)采集系統(tǒng)的背景及功能是什么?如何利用FPGA實(shí)現(xiàn)高速連續(xù)數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)?FPGA在高速連續(xù)數(shù)據(jù)采集系統(tǒng)中的應(yīng)用有哪些?

2021-04-08 06:19:37

數(shù)據(jù)采集在現(xiàn)代工業(yè)生產(chǎn)及科學(xué)研究中的重要地位日益突出,對實(shí)時(shí)高速數(shù)據(jù)采集的要求也不斷提高。在信號測量、圖像處理、音頻信號處理等一些高速、高精度的測量中,都要求進(jìn)行高速、高精度的數(shù)據(jù)采集。這就對數(shù)據(jù)采集

2019-07-31 07:25:28

本帖最后由 eehome 于 2013-1-5 09:43 編輯

高速數(shù)據(jù)采集和生成高速數(shù)據(jù)采集前端解決方案的方框圖 (SBD),它使用高速 ADC 和 DAC、放大器和 TI DSP 來采集

2012-12-12 11:48:15

怎么實(shí)現(xiàn)基于USB2.0的高速同步數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)?

2021-05-21 06:47:15

數(shù)據(jù)采集是通過采樣電路將輸入的模擬信號轉(zhuǎn)換成離散信號,并送入CPU進(jìn)行處理,已經(jīng)廣泛應(yīng)用在現(xiàn)代工業(yè)控制的各個(gè)方面。數(shù)據(jù)采集的速度和精度,很大程度上影響到整個(gè)系統(tǒng)的工作能力。常用數(shù)據(jù)采集方案是以MCU

2019-08-16 06:57:48

高速數(shù)據(jù)采集系統(tǒng)的硬件結(jié)構(gòu)MAX7000系列CPLD及其開發(fā)平臺介紹CPLD在高速數(shù)據(jù)采集系統(tǒng)中的應(yīng)用

2021-04-30 06:43:12

高速數(shù)據(jù)采集系統(tǒng)的硬件設(shè)計(jì)高速數(shù)據(jù)采集系統(tǒng)的軟件設(shè)計(jì)

2021-06-03 06:04:08

怎么設(shè)計(jì)一種高速數(shù)據(jù)采集系統(tǒng)?數(shù)據(jù)采集系統(tǒng)的組成及原理是什么?如何實(shí)現(xiàn)高速A/D轉(zhuǎn)換器與DSP的接口設(shè)計(jì)?

2021-04-12 06:10:22

基于AVR和CPLD的高速數(shù)據(jù)采集系統(tǒng)該怎樣去設(shè)計(jì)?

2021-04-29 06:59:21

高速數(shù)據(jù)采集卡系統(tǒng)的硬件怎樣去設(shè)計(jì)?高速數(shù)據(jù)采集卡系統(tǒng)的軟件怎樣去設(shè)計(jì)?

2021-04-28 06:16:28

采用PCI總線流水式高速數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)摘要:目前基于PCI總線的高速數(shù)據(jù)采集系統(tǒng),大多采用高速A/D,CPLD或FPGA,FIFO或雙端口RAM以及通用PCI接口來設(shè)計(jì),其通用性、靈活性差,不能

2009-10-30 15:09:49

深入研究高速數(shù)字電路設(shè)計(jì)中的信號完整性問題;分析電路中破壞信號完整性的原因;結(jié)合一個(gè)實(shí)際的DSP 數(shù)據(jù)采集系統(tǒng), 闡述實(shí)現(xiàn)信號完整性的具體方法。

2009-04-15 09:08:03 16

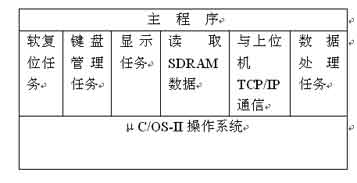

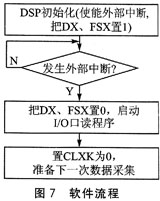

16 介紹一種基于DSP和以太網(wǎng)的數(shù)據(jù)采集處理系統(tǒng)。論述數(shù)據(jù)采集處理系統(tǒng)中的以太網(wǎng)應(yīng)用,分析系統(tǒng)的硬件設(shè)計(jì)方案,提出基于實(shí)時(shí)操作系統(tǒng)DSP/BIOS 進(jìn)行軟件設(shè)計(jì)的思路和實(shí)現(xiàn)方法。

2009-04-16 09:56:45 24

24 基于DSP和CAN總線的機(jī)車故障數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

2009-05-08 17:19:01 16

16 介紹一種基于DSP和以太網(wǎng)的數(shù)據(jù)采集處理系統(tǒng)。論述數(shù)據(jù)采集處理系統(tǒng)中的以太網(wǎng)應(yīng)用,分析系統(tǒng)的硬件設(shè)計(jì)方案,提出基于實(shí)時(shí)操作系統(tǒng)DSP/BIOS 進(jìn)行軟件設(shè)計(jì)的思路和實(shí)現(xiàn)方法。

2009-05-15 14:19:19 23

23 介紹一個(gè)基于USB2.0 接口和DSP的高速數(shù)據(jù)采集處理系統(tǒng)的工作原理、設(shè)計(jì)及實(shí)現(xiàn)。該高速數(shù)據(jù)采集處理系統(tǒng)采用TI 公司的TMS320C6000 數(shù)字信號處理器和Cypress 公司的USB2.0 接口芯片,可以

2009-05-16 14:48:53 21

21 深入研究高速數(shù)字電路設(shè)計(jì)中的信號完整性問題;分析電路中破壞信號完整性的原因;結(jié)合一個(gè)實(shí)際的DSP 數(shù)據(jù)采集系統(tǒng), 闡述實(shí)現(xiàn)信號完整性的具體方法。

2009-05-18 13:24:58 17

17 提出了一種基于DSP 的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)方案,對其中高速A/D、高速緩存。DSP 控制以及數(shù)據(jù)通訊接口等內(nèi)容進(jìn)行了討論,提出了更為有效的同步控制方式。該設(shè)計(jì)方案電路

2009-06-12 16:37:58 17

17 基于PCI總線的高速數(shù)據(jù)采集卡系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn):本文介紹一種基于PCI總線的高速數(shù)據(jù)采集卡系統(tǒng)的設(shè)計(jì)方法,討論了設(shè)計(jì)高速數(shù)據(jù)采集系統(tǒng)的關(guān)鍵技術(shù),給出了系統(tǒng)整體設(shè)計(jì)方案和P

2009-06-22 19:04:54 44

44 本文對高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)進(jìn)行了討論,介紹利用高速線性放大器、高速A/D 轉(zhuǎn)換芯片、ISP 器件制作的DMA 接口,設(shè)計(jì)以單片機(jī)為核心的高速數(shù)據(jù)采集系統(tǒng)的方法。關(guān)鍵詞: I

2009-07-15 11:16:00 22

22 介紹了CAN 總線在航天領(lǐng)域的應(yīng)用狀況,在對CAN 總線技術(shù)和DSP 芯片功能研究的基礎(chǔ)上,設(shè)計(jì)了基于CAN 總線和DSP 的雙層數(shù)據(jù)采集系統(tǒng),本數(shù)據(jù)采集系統(tǒng)對于CAN 總線技術(shù)在航天領(lǐng)域

2009-09-26 09:11:39 23

23 設(shè)計(jì)了基于Matlab 和VC 混合編程的DSP 數(shù)據(jù)采集系統(tǒng),實(shí)現(xiàn)了在Matlab 平臺上控制和操作DSP 目標(biāo)板進(jìn)行數(shù)據(jù)采集,并把采集的數(shù)據(jù)上傳到Matlab 平臺進(jìn)行實(shí)時(shí)分析處理和圖形顯示,然

2010-01-25 14:43:13 50

50 基于MAX3420的實(shí)時(shí)數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

針對TMSC3206000數(shù)字信號處理器的特點(diǎn),設(shè)計(jì)了基于DSP和MAX3420的實(shí)時(shí)數(shù)據(jù)采集系統(tǒng).

2010-06-11 17:26:23 39

39 本文介紹了CYPRESS 公司的高速雙口RAM CY7C026 的工作原理,以及它基于DSP TMS320VC5402 芯片的高速數(shù)據(jù)采集方面的應(yīng)用,同時(shí)討論了CY7C026 作為高速數(shù)據(jù)采集系統(tǒng)中的高速接口的優(yōu)點(diǎn)

2010-07-13 11:44:26 17

17 介紹一種以DSP為核心處理器的高速遠(yuǎn)程數(shù)據(jù)采集與處理系統(tǒng)! 該系統(tǒng)以分時(shí)采集方式對多路模擬信號進(jìn)行數(shù)據(jù)采集"采樣率達(dá)40MHZ經(jīng)過高速處理器的實(shí)時(shí)處理"通過光纜將數(shù)據(jù)傳送

2010-07-22 16:14:18 16

16 在以XilinxⅡ- PRO 和MAX104A 為主要部件的高速數(shù)據(jù)采集系統(tǒng)中,提高系統(tǒng)處理速度的關(guān)鍵是芯片和芯片之間數(shù)據(jù)高速傳輸。文章重點(diǎn)介紹了LVDS 和LVPECL 接口匹配設(shè)計(jì)和高速串行RocketIO

2010-09-22 08:36:07 11

11 數(shù)據(jù)采集系統(tǒng)是通過采樣電路將輸入的模擬信號轉(zhuǎn)換成離散信號,并送入CPU、MCU或DSP進(jìn)行處理。現(xiàn)在流行的基于PCI總線設(shè)計(jì)的采集卡是數(shù)據(jù)采集系統(tǒng)的主流,其優(yōu)點(diǎn)是可以利用PCI

2009-04-19 10:52:31 817

817

MAX1420/MAX12553 example

Abstract: This application note demonstrates how to quickly verify

2009-05-01 10:46:40 613

613

高速USB數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)

在圖像處理、瞬態(tài)信號測量等一些高速、高精度的應(yīng)用中,需要進(jìn)行高速數(shù)據(jù)采集。USB 2.0接口以其高速率等優(yōu)點(diǎn)漸有取

2009-09-26 18:05:46 677

677

基于CPLD和嵌入式系統(tǒng)的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)

介紹一種基于CPLD和嵌入式系統(tǒng)的高速數(shù)據(jù)采集系統(tǒng),并詳細(xì)闡述了系統(tǒng)的結(jié)構(gòu)和軟硬件的實(shí)

2009-10-15 23:46:59 616

616

基于A/D和DSP的高速數(shù)據(jù)采集技術(shù)

中頻信號分為和差兩路,高速A/D與DSP組成的數(shù)據(jù)采集系統(tǒng)要分別對這兩路信號進(jìn)行采集。對于兩路數(shù)據(jù)采集電路,A/

2009-10-17 10:17:41 1201

1201

基于CPLD/FPGA高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)

0 引 言 傳統(tǒng)的數(shù)據(jù)采集系統(tǒng)一般采用單片機(jī),系統(tǒng)大多通過PCI總線完成數(shù)據(jù)的傳輸。其缺點(diǎn)是數(shù)學(xué)運(yùn)算能力差;

2010-01-27 09:35:01 508

508

利用DSP和USB的三維感應(yīng)測井數(shù)據(jù)采集系統(tǒng)

數(shù)據(jù)采集是DSP最基本的應(yīng)用領(lǐng)域,本文設(shè)計(jì)的數(shù)據(jù)采集系統(tǒng)利用TI公司的TMS320F2812 DSP芯片。該芯片的主要特點(diǎn)有:150 MI/s(百萬

2010-03-04 10:10:44 626

626

FPGA芯片在高速數(shù)據(jù)采集緩存系統(tǒng)中的應(yīng)用

概 述在高速數(shù)據(jù)采集方面,F(xiàn)PGA有單片機(jī)和DSP無法比擬的優(yōu)勢。FPGA的時(shí)鐘頻率高,內(nèi)部時(shí)延小,全部控制邏輯都可由硬

2010-03-30 10:51:15 881

881

摘要:為準(zhǔn)確地分析工業(yè)生產(chǎn)中的各種數(shù)據(jù)參數(shù),結(jié)合高速DSP和FPGA的特點(diǎn),設(shè)計(jì)一套數(shù)據(jù)采集系統(tǒng),應(yīng)用FPGA的內(nèi)部邏輯實(shí)現(xiàn)時(shí)序控制,以DSP作為采集系統(tǒng)的核心,對采集到的數(shù)據(jù)進(jìn)行濾波等處理,并將處理后的結(jié)果通過USB口傳輸?shù)接?jì)算機(jī)。設(shè)計(jì)中還采用ADC0809模數(shù)轉(zhuǎn)換

2011-02-27 23:04:00 96

96 摘要:在介紹電容層析成像系統(tǒng)組成原理的基礎(chǔ)上,重新構(gòu)建了一套數(shù)字化的數(shù)據(jù)采集系統(tǒng),它具有較高的采集速度和分辨率真,著重分析了FPGA控制A/D采集和DSP響應(yīng)中斷進(jìn)行DMA傳輸?shù)挠嘘P(guān)問題。 關(guān)鍵詞:DSP DMA 中斷服務(wù)程序 ECT

2011-02-28 12:36:44 48

48 中頻信號分為和差兩路,高速A/D與 DSP 組成的數(shù)據(jù)采集系統(tǒng)要分別對這兩路信號進(jìn)行采集。對于兩路數(shù)據(jù)采集電路,A/D與DSP的接口連接是一樣的。

2011-09-08 17:48:04 42

42 CPLD在高速數(shù)據(jù)采集系統(tǒng)中的應(yīng)用! 介紹了高速數(shù)據(jù)采集系統(tǒng)的整體框架分析了其中的通用部分CPLD系列產(chǎn)品的特點(diǎn)及其開發(fā)軟件.CPLD根據(jù)高速數(shù)據(jù)采集系統(tǒng)的需要VHDL語言的形式,介紹了由

2011-12-17 00:12:00 26

26 中頻信號分為和差兩路,高速A/D與DSP組成的數(shù)據(jù)采集系統(tǒng)要分別對這兩路信號進(jìn)行采集。對于兩路數(shù)據(jù)采集電路,A/D與DSP的接口連接是一樣的。兩個(gè)A/D同時(shí)將和路與差路信號采

2012-03-28 10:41:38 4990

4990

基于LABVIEW與DSP串口的數(shù)據(jù)采集系統(tǒng)。

2016-01-20 16:26:53 41

41 高速大容量數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn),下來看看

2016-05-10 11:24:33 14

14 高速數(shù)據(jù)采集系統(tǒng)中的FPGA的設(shè)計(jì),下來看看

2016-05-10 11:24:33 15

15 基于FPGA的高速數(shù)據(jù)采集硬件系統(tǒng)設(shè)計(jì).

2016-05-10 17:06:40 43

43 基于FPGA的高速數(shù)據(jù)采集系統(tǒng)接口設(shè)計(jì).

2016-05-10 17:06:40 27

27 基于FPGA的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì),下來看看

2016-05-10 17:06:40 19

19 基于FPGA的高速數(shù)據(jù)采集系統(tǒng)設(shè)計(jì),用ad芯片和sdram構(gòu)成高速數(shù)據(jù)采集系統(tǒng)。

2016-05-17 09:49:51 35

35 六通道高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)

2017-01-17 19:54:24 11

11 基于PXI架構(gòu)的高速數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)_黃宇

2017-02-07 15:17:36 6

6 單片機(jī)高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)_張俊梅

2017-03-19 11:28:16 2

2 基于CPLD高速數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)_鮮果

2017-03-19 11:45:23 3

3 高速數(shù)據(jù)采集系統(tǒng)設(shè)計(jì),DSP嵌入式系統(tǒng)開發(fā)典型案例

2017-10-19 13:29:25 14

14 基于ARM與DSP的聲頻數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

2017-10-20 08:34:12 6

6 基于Matlab和VC混合編程的DSP數(shù)據(jù)采集系統(tǒng)

2017-10-20 09:31:09 4

4 對數(shù)據(jù)采集與處理系統(tǒng)提出嚴(yán)格的要求。本文設(shè)計(jì)并實(shí)現(xiàn)一種基于DSP和USB的高速數(shù)據(jù)采集與處理系統(tǒng)。該系統(tǒng)電路簡單,可靠性好,具有一定的通用性,并且可以進(jìn)行多通道擴(kuò)展。 1 原理概述 基于DSP和USB的高速數(shù)據(jù)采集與處理系統(tǒng)的原

2017-11-06 14:58:00 16

16 數(shù)據(jù)采集系統(tǒng)廣泛地應(yīng)用于工業(yè)、國防、圖像處理、信號檢測等領(lǐng)域。DSP處理器是一種高速的數(shù)字信號處理器,藍(lán)牙技術(shù)作為一種低成本、低功耗、近距離的無線通信技術(shù),已廣泛應(yīng)用于許多行業(yè)和領(lǐng)域

2017-12-02 17:45:54 353

353 介紹了1種基于FPGA和DSP的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)和實(shí)現(xiàn),其FPGA采用Altera公司ACEX 1K系列的EPIK50Tcl443器件,DSP芯片采用TI公司TMs320系列

2018-11-07 17:18:24 18

18 2018年8月,西安慕雷電子發(fā)布了全球頂級高速數(shù)據(jù)采集記錄存儲系統(tǒng),采樣率高達(dá)4GSPS,分辨率12bit,模擬帶寬2GHZ,記錄存儲帶寬高達(dá)6GB/S!西安慕雷電子供應(yīng)全球頂級高速數(shù)據(jù)采集卡及超寬

2018-11-13 21:21:34 486

486 本文詳細(xì)介紹了一種基于PCI 總線的高速數(shù)據(jù)采集系統(tǒng)的原理、組成和功能以及在Windows2000 環(huán)境下進(jìn)行數(shù)據(jù)采集和存儲的方法。該系統(tǒng)用于某型號衛(wèi)星下行的高速數(shù)據(jù)采集。系統(tǒng)設(shè)計(jì)與技術(shù)的通用性可應(yīng)用于其它類似的高速數(shù)據(jù)采集與處理系統(tǒng)中。

2019-11-27 16:19:00 4

4 本文詳細(xì)介紹了一種基于 PCI 總線的高速數(shù)據(jù)采集系統(tǒng)的原理、組成和功能以及在 Windows 2000 環(huán)境下進(jìn)行數(shù)據(jù)采集和存儲的方法。該系統(tǒng)用于某型號衛(wèi)星下行的高速數(shù)據(jù)采集。系統(tǒng)設(shè)計(jì)與技術(shù)的通用性可應(yīng)用于其它類似的高速數(shù)據(jù)采集與處理系統(tǒng)中。

2021-04-14 14:29:30 13

13 電子發(fā)燒友網(wǎng)為你提供Maxim(Maxim)MAX1420CCM+TD相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊,更有MAX1420CCM+TD的引腳圖、接線圖、封裝手冊、中文資料、英文資料,MAX1420CCM+TD真值表,MAX1420CCM+TD管腳等資料,希望可以幫助到廣大的電子工程師們。

2023-01-15 19:41:54

高速可靠地傳遞至主控計(jì)算機(jī)作進(jìn)一步的分析處理。本文主要介紹高速模數(shù)轉(zhuǎn)換器SC1083芯片用于DSP前端的數(shù)據(jù)采集與處理。DSP前端系統(tǒng)的數(shù)據(jù)采集部分主要完成超聲波信

2023-05-18 10:01:54

正在加载...

電子發(fā)燒友App

電子發(fā)燒友App

評論