目前發展起來的高速數字信號處理器(DSP)在語音處理系統中得到了廣泛應用。TMS320VC5402的TI公司生產的一種性能價格比較高的16位定點DSP。它的指令周期為10ns,具有運算速度快、通用性能、接口連接方便等特點,尤其適合在語音編碼和通信中應用。

TLC320AD50C是TI公司生產的∑-Δ型A/D、D/A音頻接口芯片,為V3.4調制解調器以及音頻應用提供了通用的模擬接口,可以直接與TMS320VC5402相連。本文詳細介紹TLC320AD50C與TMS320VC5402的硬件接口連接和軟件設計。

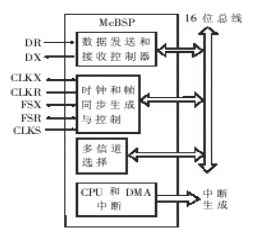

1 TMS320VC5402的McBSP

TMS320VC5402有兩個McBSP(多通道緩存串行口)。

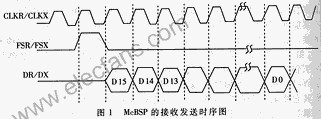

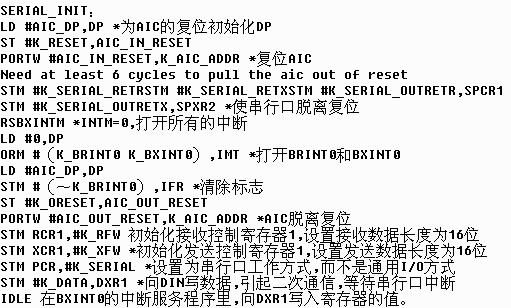

McBSP提供了全雙工的通信機制,以及雙緩存的發送寄存器和三緩存的接收寄存器,允許連續的數據流傳輸,數據長度可以為8、12、16、20、24、32;同時還提供了A-律和μ-律壓擴,多達128個通道的發送和接收。McBSP通過7個引腳使得一個數據通路和一個控制通路與外部設備相連。數據經McBSP與外設的通信通過DR和DX引腳傳輸,控制信號則由CLKX、CLKR、FSX、FSR等四條引腳來實現。CPU和DMA控制器可以讀取DRR的數據實現接收,并且可以對DXR寫入數據實現發送。接收和發送幀同步脈沖既可以由內部采樣速率產生器產生,也可以由外部脈沖源驅動。當FSR和FSX都為輸入時(FSXM=FSRM=0,外部脈沖源驅動),McBSP分別在CLKR和CLKX的下降沿檢測,且DR的數據也在CLKR的下降沿進行采樣。而當FSR和FSX都為輸出時,則在CLKX和CLKR的上升沿進行檢測。

16-bit的串行口控制寄存器SPCR和引腳控制寄存器PCR用來配置串行口;接收控制寄存器RCR和發送控制寄存器XCR分別設置接收和發送的不同參數,如幀長度、每幀的數據長度等。

圖1是當FSR和FSX為輸出時McBsp的發送和接收時序圖。另外,McBSP還可以通過(R/X)DATDLY設置接收和發送數據延遲,通過(R/X)PHASE設置接收和發送的多階段。

2 音頻模擬接口芯片TLC320AD50C

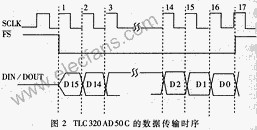

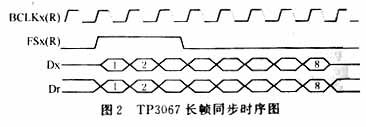

TLC320AD50C是TI生產的∑-Δ型單片音頻接口芯片。它集成了16位A/D和D/A轉換器,采樣速率最高可達22.05kb/s,其采樣速率可通過DSP編程來設置。在TLC320AD50C內部DAC之前有插值濾波器,而在ADC之后有抽樣濾波器,接收和發送可以同時進行。TLC320AD50C與TMS320VC5402之間采用串行通信方式,有兩種數據傳輸模式:16們傳輸模式和15+1位傳輸模式。若采用15+1位傳輸模式,其中的D0位用來表示二次通信。TLC320AD50C的數據傳輸時序如圖2所示。

該器件采用兩組模擬輸入和兩組模擬輸出,有足夠的共模抑制能力,可以工作在差分或單端方式。當模擬輸出時,輸出端通常接600Ω的負載。

TLC320AD50C的工作由7個控制寄存器控制。其中,控制寄存器1:軟件復位以及DAC的16位或15+1位模式選擇。

控制寄存器2:ADC的16位或15+1位模式選擇。

控制寄存器4:選擇輸入和輸出放大器的增益;通過選擇N確定采樣速率fs;選擇PLL,如果選擇PL(D7=0),則fs=MCLK/(128N),否則(D7=1),fs=MCLK/(512N)。其中,N=1-8。

該器件工作方式的設定和采樣頻率均可以由DSP編程來實現,所以TLC320AD50C使用靈活、設置容易、與TMS320VC5402的連接易于實現。

3 TMS320VC5402與TLC320AD50C硬件連接及軟件實現

3.1 硬件連接

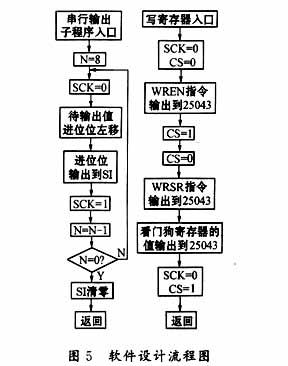

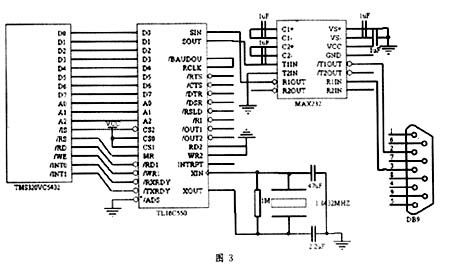

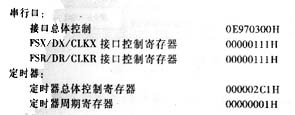

根據圖1和圖2的時序,則容易實現TLC320AD50C與TMS320VC5402的硬件連接,如圖3所示。

TLC320AD50C的MCLK外接8.192MHz的晶振,TMS320VC5402的FSX和FSR由TLC320AD50C設置。如果選擇D7=0,N=8,則采樣速率為8kHz。

3.2 通信協議

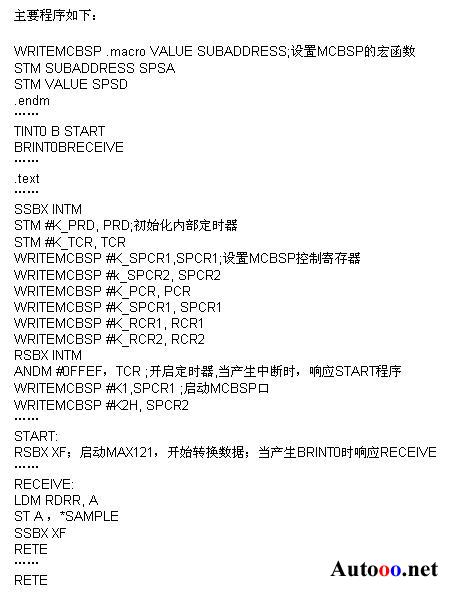

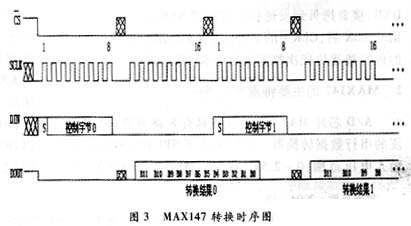

TLC320AD50C的通信有兩種格式:一次通信格式和二次通信格式。

一次通信格式的16位都用來傳輸數據。DAC的數據長度由寄存器1的D0位決定。啟動和復用時,缺省值為15+1位模式,最后一位要求二次通信。如果工作在16位傳輸模式,則必須由FC產生二次通信請求。

二次通信格式則用來初始化和修改TLC320AD50C內部寄存器的值。在二次通信中可以通過向DIN寫數據來初始化。

格式如下:

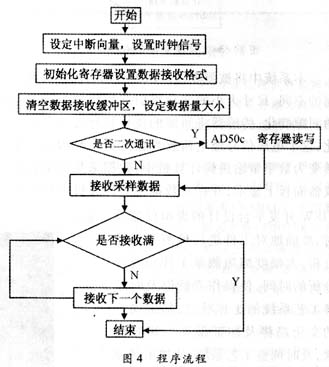

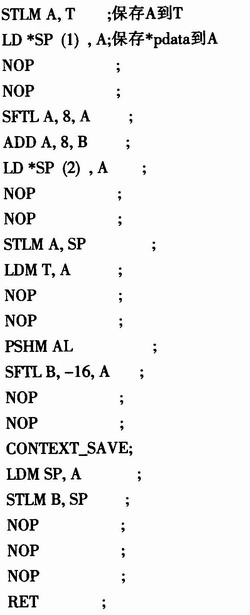

系統復位后,必須通過DSP的DX口向TLC320AD50C的DIN寫數據,如果采用一片TLC320AD50C,只需初始化其寄存器1、寄存器2和寄存器4。

由于通信數據長度為16位,初始化時應通過RCR1和XCR1設置McBSP的傳輸數據長度為16。考慮到TLC320AD50C復位后至少經過6個MCLK才可以脫離復位,故可以在此時間內初始化DSP的串行口。

3.3 軟件實現

電子發燒友App

電子發燒友App

評論