從設(shè)備組成,主設(shè)備啟動(dòng)與從設(shè)備的同步通信,從而完成數(shù)據(jù)的交換。標(biāo)準(zhǔn)的SPI僅僅使用4個(gè)引腳,常用于主設(shè)備和外設(shè)(flash、實(shí)時(shí)時(shí)鐘、dsp等器件)的通信。

2022-07-07 09:33:49 3296

3296 CPLD在DSP系統(tǒng)中的應(yīng)用設(shè)計(jì)

2011-08-03 16:15:49

CPLD的串口通信設(shè)計(jì)

2012-08-20 17:59:18

本帖最后由 zhaironghui 于 2015-7-28 17:40 編輯

自己做的一塊板子,(CPLD 和 DSP 上電后有引腳連接在一起)1.當(dāng)只向其中一塊芯片下載程序時(shí)能成功。(比如向

2015-07-28 17:24:08

CPLD控制AD 轉(zhuǎn)換芯片進(jìn)行轉(zhuǎn)換,轉(zhuǎn)換之后將數(shù)字信號(hào)傳給外部RAM ,請(qǐng)問各位大神,怎么編寫DSP訪問外部RAM的程序。

2016-03-05 11:37:37

自己做的DSP2812+CPLD板子

2016-01-18 14:39:49

DSP、MCU、ARM、CPLD/FPGA對(duì)比分析哪個(gè)好?

2021-10-22 07:17:10

的速度是480Mbits/s,完全可以滿足圖像采集、傳輸以及后續(xù)處理的要求。系統(tǒng)中采用 DSP+CPLD的硬件設(shè)計(jì)方案,采用現(xiàn)場(chǎng)可編程芯片 CPLD及兩片 SRAM構(gòu)成的圖像采集和存儲(chǔ)系統(tǒng),可以根據(jù)

2019-06-20 07:31:29

是480Mbits/s,完全可以滿足圖像采集、傳輸以及后續(xù)處理的要求。系統(tǒng)中采用 DSP+CPLD的硬件設(shè)計(jì)方案,采用現(xiàn)場(chǎng)可編程芯片 CPLD及兩片 SRAM構(gòu)成的圖像采集和存儲(chǔ)系統(tǒng),可以根據(jù)

2019-07-26 07:16:41

如何在CPLD內(nèi)部構(gòu)造一個(gè)雙口RAM,實(shí)現(xiàn)DSP從CPLD中讀寫數(shù)據(jù)

2015-10-25 17:14:50

用的貴公司的TL138F-EVM A2開發(fā)板。想利用SPI協(xié)議實(shí)現(xiàn)FPGA和DSP通信。看了核心板引腳說明 沒有看到FPGA這邊SPI協(xié)議要用的接口,是不是這塊板子不能實(shí)現(xiàn)DSP和FPGA的SPI通信。麻煩床龍工程師指導(dǎo)下。還有其他方法嗎?

2020-04-24 06:46:47

dsp 2407+CPLD實(shí)驗(yàn)指導(dǎo)書

2012-05-02 00:19:20

實(shí)驗(yàn)不正確了,我和別的板子對(duì)比的時(shí)候發(fā)現(xiàn)rw和IOStrb 這兩個(gè)管腳輸出的信號(hào)和正常板子輸出的不一致。問題應(yīng)該處在哪?如果板子的dsp芯片壞了,會(huì)不會(huì)只會(huì)通信那部分壞了?如果是cpld程序不對(duì)?是不是cpld本身時(shí)序有問題?

2014-06-06 17:40:21

正在用ADE7763做電能計(jì)量,通過SPI與DSP2812進(jìn)行通信,看了ADE7763的手冊(cè),發(fā)現(xiàn)都是原理介紹或者寄存器設(shè)置介紹,沒看到SPI通信協(xié)議啊?請(qǐng)問各位誰有這個(gè)協(xié)議的說明的?也就是說側(cè)重這個(gè)芯片使用方面的資料,感激不盡了!!

2014-08-09 11:22:57

我正在使用 CY8C5867LTI-LP025。

我知道我需要使用 SIO 端口來使用 I2C、UART 等。

SPI通信是否也需要使用 SIO 端口?

2024-03-06 06:23:39

DSP新手求助啊!!實(shí)驗(yàn)室讓F28335通過SPI通信連DA外設(shè),我在看SPI的時(shí)候不知道FIFO是一個(gè)什么存在呢?不是單單通過SPITXBUF和SPIDAT就能發(fā)送數(shù)據(jù)嘛?

2017-08-09 17:15:29

網(wǎng)上看到有4種通信方式:1.CAN總線2.HPI通信3.CPLD/FPGA通信(當(dāng)雙口RAM)4.SPI通信 請(qǐng)問一下這幾種方式的優(yōu)缺點(diǎn)。

2017-07-07 16:08:51

STM32模擬SPI通信協(xié)議SPI的簡介:SPI是串行外設(shè)接口的縮寫,是一種高速的,全雙工、同步的串行通信總線;SPI也可以實(shí)現(xiàn)一主多從,而實(shí)現(xiàn)一主多從是通過CS片選來實(shí)現(xiàn),于IIC有些不同;SPI

2022-02-17 08:03:14

用兩塊DSP2812進(jìn)行SPI通信遇到問題好久都不能解決。只是想讓主機(jī)發(fā)送一組16位的數(shù)據(jù)在whili語句中發(fā)送給從機(jī),從機(jī)收到數(shù)據(jù)后在數(shù)碼管上顯示。兩塊板子的地、時(shí)鐘、SIMO連在一起。主機(jī)

2016-10-20 13:47:22

基于DSP***的模擬SPI————你真的理解SPI通信嗎?? 你真的理解SPI是怎么通信的嗎?SPI通信時(shí),什么時(shí)候發(fā)送數(shù)據(jù)?什么時(shí)候數(shù)據(jù)采樣?我們?cè)谧瞿MSPI時(shí)怎么體現(xiàn)出SPI的四種工作模式

2022-02-17 06:37:57

,6為地址總線驅(qū)動(dòng)電路使能信號(hào),7為DSP輸出控制總線,8為CPLD譯碼后輸人DSP的信號(hào)線,9為DSP同步外圍電路的時(shí)鐘,10為DMA輸人時(shí)鐘,11為RAM,8237和聲卡的讀寫信號(hào),12為鎖存信號(hào)

2018-12-14 10:57:58

(Digital Signal Processor)與CPLD的連接是通過DSP的外部存儲(chǔ)器接口實(shí)現(xiàn)的。我們通過/IS管腳將其擴(kuò)展到外部I/O空間,數(shù)據(jù)總線的高8位和地址總線的低8位與CPLD相連,并且我們將

2019-05-21 05:00:16

我要做基于CPLD的SPI控制器的研究與實(shí)現(xiàn),有沒有會(huì)的人,求教,有什么資料推薦點(diǎn)也行

2013-04-27 14:37:53

極大地提高現(xiàn)有空間瞬態(tài)信號(hào)探測(cè)的自動(dòng)錄取和分析能力。在實(shí)時(shí)信號(hào)處理技術(shù)中,dsp+cpld方式是目前國際上比較通用的方法,如美國、俄羅斯等多采用這種方式。dsp是一種可編程的數(shù)字微處理器。與單片機(jī)相比

2019-06-25 06:26:46

串行外圍設(shè)備接口,是一種高速全雙工的通信總線。它被廣泛地使用在要求通訊速率較高的場(chǎng)合。SPI用于多設(shè)備之間通訊

2021-12-06 08:27:27

ARM主要是用來實(shí)現(xiàn)系統(tǒng)控制和網(wǎng)絡(luò)傳輸,要如何來實(shí)現(xiàn)arm與多DSP之間的通信問題?arm和一片dsp之間的通信可以通過hpi,多個(gè)的話能不能實(shí)現(xiàn),硬件上要如何設(shè)計(jì)?謝謝了

2022-04-18 09:28:30

本設(shè)計(jì)以Xilinx公司的XC95108為例,通過在CPLD中開辟2塊獨(dú)立的SRAM區(qū)域(各1字節(jié))來實(shí)現(xiàn)DSP2407A與S3C4480的并行通信。

2021-06-03 07:06:56

嗨,大家好!我正在使用JTAG Cable xilinx平臺(tái)電纜型號(hào)DLC9G。我必須通過1個(gè)JTAG端口控制4個(gè)CPLD。現(xiàn)在我可以同時(shí)將相同的代碼放入4個(gè)CPLD中。但我必須將4個(gè)不同的代碼分別

2020-06-09 17:33:18

本文介紹的智能控制單元采用數(shù)字信號(hào)處理器(DSP)及嵌入式實(shí)時(shí)操作系統(tǒng)完成各種數(shù)據(jù)的處理、通信和算法的設(shè)計(jì),而狀態(tài)量的采集和執(zhí)行信號(hào)輸出將由復(fù)雜可編程邏輯器(CPLD)完成,主要是基于CPLD內(nèi)部硬件電路結(jié)構(gòu)的可靠性和對(duì)狀態(tài)采集的實(shí)時(shí)性,該系統(tǒng)可以滿足系統(tǒng)控制實(shí)時(shí)性及可靠性的要求。

2021-05-08 06:44:24

IO口模擬SPI根據(jù)SPI通信規(guī)范,與IO口模擬I2C類似,通過普通IO端口模擬也可以實(shí)現(xiàn)單片機(jī)(主設(shè)備)與從設(shè)備的SPI通信,其中使能信號(hào)CS在開始SPI通信前置低,在通信結(jié)束后置高,時(shí)鐘線SCK

2022-02-17 07:19:10

有償找一位精通CPLD和DSP的高手,需要教的內(nèi)容為:在CPLD中用Verilog語言編寫增量式編碼器信號(hào)的鑒相細(xì)分、計(jì)數(shù)功能,以及CPLD與DSP之間進(jìn)行數(shù)據(jù)傳輸通信、DSP中編寫相關(guān)算法以及

2013-07-26 20:49:22

我是用STM32和EPM240做SPI通信,STM32為主SPI,CPLD為從SPI,8位通信,將always@(posedge CS_N or negedge rst_n) 下的 elsebegintxd_data

2018-06-02 17:25:26

我在做fpga與dsp的SRIO通信,我用的是論壇上提供的SRIO test程序,目前dsp端能夠?qū)崿F(xiàn)端口0的外部回環(huán)測(cè)試。fpga端的協(xié)議還沒做通,我想用dsp直接給fpga發(fā)包,fpga根據(jù)收到

2018-06-21 10:45:13

請(qǐng)教一下。dsp6713和fpga通信,如果選擇spi通信,,它和emif通信相比誰更有優(yōu)勢(shì),謝謝

2018-07-25 08:47:48

求STM32與DSP的spi通信注意事項(xiàng)

2019-04-17 06:35:22

另外,在DSP系統(tǒng)中為什么要使用CPLD?有大俠指導(dǎo)嗎?

2019-07-05 03:42:00

我在使用郵箱處理SPI與射頻模塊的通信,實(shí)現(xiàn)郵箱收發(fā)函數(shù),使用的是spi2,想咨詢下,如何確定郵箱發(fā)送對(duì)應(yīng)的是端口是 spi2呢?在哪里設(shè)置或者體驗(yàn)?例如使用兩個(gè)串口UART1和UART2,當(dāng)用郵箱發(fā)送函數(shù)時(shí),怎么確定是串口1 還是 串口2?

2019-01-11 10:35:45

的接口電路整個(gè)系統(tǒng)結(jié)構(gòu)框圖如圖2所示。從圖中可以看出,CPLD主要完成數(shù)據(jù)總線驅(qū)動(dòng)、地址總線驅(qū)動(dòng)、地址鎖存器、譯碼和時(shí)鐘分頻等功能,其中譯碼電路是整個(gè)電路的核心。數(shù)據(jù)總線驅(qū)動(dòng)電路和地址總線驅(qū)動(dòng)將DSP

2019-05-31 05:00:03

系統(tǒng)結(jié)構(gòu)框圖如圖2所示。從圖中可以看出,CPLD主要完成數(shù)據(jù)總線驅(qū)動(dòng)、地址總線驅(qū)動(dòng)、地址鎖存器、譯碼和時(shí)鐘分頻等功能,其中譯碼電路是整個(gè)電路的核心。數(shù)據(jù)總線驅(qū)動(dòng)電路和地址總線驅(qū)動(dòng)將DSP的內(nèi)部數(shù)據(jù)

2019-06-05 05:00:14

結(jié)合繼電保護(hù)測(cè)試裝置的研制體會(huì),介紹基于DSP 的CPLD 多方案現(xiàn)場(chǎng)可編程配置方法,給出硬件的配置連接、CPLD 配置數(shù)據(jù)的獲取與存儲(chǔ)方法和CPLD 在DSP 控制下的被動(dòng)串行配置過程。設(shè)

2009-04-15 08:50:55 29

29 講述快速器件DSP和慢速器件液晶模塊的接口方法;結(jié)合作者實(shí)際工作的一個(gè)成功應(yīng)用,給出TMS320C32 DSP 與內(nèi)藏T6963C 控制器的液晶模塊通過CPLD 接口的硬件和軟件實(shí)例。

2009-04-16 10:26:44 22

22 結(jié)合繼電保護(hù)測(cè)試裝置的研制體會(huì),介紹基于DSP 的CPLD 多方案現(xiàn)場(chǎng)可編程配置方法,給出硬件的配置連接、CPLD 配置數(shù)據(jù)的獲取與存儲(chǔ)方法和CPLD 在DSP 控制下的被動(dòng)串行配置過程。設(shè)

2009-05-18 14:33:24 16

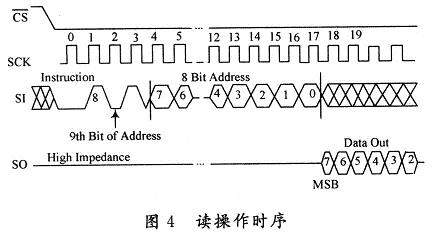

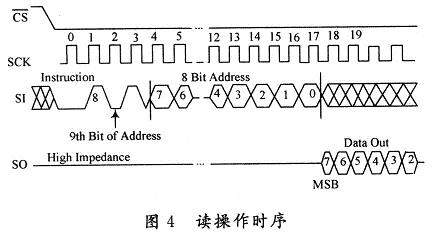

16 本文根據(jù)SPI 同步串行接口的通信協(xié)議,介紹了在CPLD 中利用VHDL 語言實(shí)現(xiàn)PC/104

總線擴(kuò)展SPI 接口的設(shè)計(jì)原理和編程思想。通過該方法的介紹,使得那些沒有SPI

接口功能的

2009-05-30 09:28:18 41

41 講述快速器件DSP 和慢速器件液晶模塊的接口方法;結(jié)合作者實(shí)際工作的一個(gè)成功應(yīng)用,給出TMS320C32 DSP 與內(nèi)藏T6963C 控制器的液晶模塊通過CPLD 接口的硬件和軟件實(shí)例。關(guān)鍵

2009-05-31 14:27:22 22

22 設(shè)計(jì)了利用TMS320LF2407A 與EPM3032A 控制的ADS7805 多通道采集系統(tǒng)的邏輯結(jié)構(gòu),介紹了系統(tǒng)的工作原理,詳細(xì)描述了ADS7805、DSP 及CPLD 之間接口的硬件與軟件設(shè)計(jì)。關(guān)鍵詞 DSP;CPLD

2009-06-18 08:14:30 58

58 針對(duì)柔性化制造的要求,構(gòu)建了以DSP+CPLD為基礎(chǔ)的數(shù)控系統(tǒng)平臺(tái)。該平臺(tái)集成度高、穩(wěn)定性強(qiáng),能實(shí)現(xiàn)生產(chǎn)過程的高速度、高精度要求,實(shí)現(xiàn)了基于CPLD的可重構(gòu)設(shè)計(jì),提高了系

2009-06-18 09:58:25 23

23 本文主要介紹數(shù)字信號(hào)處理器(DSP)和復(fù)雜可編程邏輯控制器(CPLD)在遠(yuǎn)動(dòng)終端控制系統(tǒng)中的應(yīng)用。為提高系統(tǒng)的實(shí)時(shí)響應(yīng)性能和信號(hào)處理能力,在硬件上,采用DSP 和CPLD技術(shù),提

2009-08-07 10:36:53 11

11 基于CPLD 和DSP 設(shè)計(jì)了線陣CCD 檢測(cè)系統(tǒng),CCD 的時(shí)序驅(qū)動(dòng)由CPLD 實(shí)現(xiàn),經(jīng)過運(yùn)放后的視頻信號(hào)由TMS320F2812 進(jìn)行采集和處理,此檢測(cè)系統(tǒng)已成功應(yīng)用于醫(yī)藥包裝行業(yè)的數(shù)粒機(jī)系統(tǒng),能夠可

2009-08-13 14:53:46 22

22 介紹了采用CPLD 實(shí)現(xiàn)DSP 芯片TMS320C6713 和背板VME 總線之間高速數(shù)據(jù)傳輸?shù)南到y(tǒng)設(shè)計(jì)方法。設(shè)計(jì)中采用VHDL 語言對(duì)CPLD 進(jìn)行編程。同時(shí)由于CPLD 的現(xiàn)場(chǎng)可編程特性,增強(qiáng)了整個(gè)系統(tǒng)

2009-08-15 08:39:23 51

51 本文詳細(xì)介紹了TMS320VC5509A DSP 電測(cè)量系統(tǒng)中實(shí)現(xiàn)SPI 閃速引導(dǎo)的方法。以Atmel 公司閃存AT25F1024 為例,介紹了電測(cè)量系統(tǒng)DSP 在線系統(tǒng)編程燒寫方TMS320VC5509A 串行SPI 8 位引導(dǎo)的原理與實(shí)現(xiàn)

2009-09-01 10:14:56 19

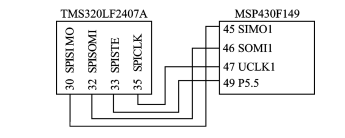

19 簡述了SPI總線協(xié)議工作時(shí)序和配置要求,通過一個(gè)成功的實(shí)例詳細(xì)介紹了使用SPI總線實(shí)現(xiàn)DSP與MCU之間的高速通信方法,并參考實(shí)例給出了SPI接口的硬件連接、初始化、以及傳輸

2009-11-27 15:10:35 58

58 本文介紹了一種基于DSP TMS320F2812和CPLD EPM7128SQC100的液晶模塊的設(shè)計(jì)與實(shí)現(xiàn)方法。將CPLD作為DSP與液晶模塊之間連接的橋梁,解決了快速處理器DSP與慢速外設(shè)液晶模塊的匹配問題,給

2010-01-20 14:48:15 54

54 為了實(shí)現(xiàn)實(shí)時(shí)便攜式數(shù)字圖像穩(wěn)定系統(tǒng)的現(xiàn)場(chǎng)應(yīng)用,設(shè)計(jì)一種基于DSP C6416的實(shí)時(shí)數(shù)字圖像穩(wěn)定系統(tǒng)。該系統(tǒng)由CPLD進(jìn)行處理邏輯和視頻同步控制,通過兩個(gè)雙端口RAM作為數(shù)據(jù)輸

2010-07-10 16:29:11 35

35 針對(duì)柔性化制造的要求,構(gòu)建了以DSP+CPLD為基礎(chǔ)的數(shù)控系統(tǒng)平臺(tái)。該平臺(tái)集成度高、穩(wěn)定性強(qiáng),能實(shí)現(xiàn)生產(chǎn)過程的高速度、高精度要求,實(shí)現(xiàn)了基于CPLD的可重構(gòu)設(shè)計(jì),提高了系統(tǒng)的

2010-07-13 15:44:02 13

13 以max700系列為代表!介紹了CPLD在DSP系統(tǒng)中的應(yīng)用實(shí)例" 該方案具有一定的普遍適用性"

2010-07-19 17:05:21 39

39 設(shè)計(jì)了一種基于DSP+CPLD構(gòu)架的電能質(zhì)量監(jiān)測(cè)裝置,該裝置利用CPLD產(chǎn)生DSP外圍器件的控制時(shí)序,丈中詳細(xì)介紹了CPLD對(duì)DSP外圍器件的邏輯接口設(shè)計(jì),通過MAX+PLUSII對(duì)CPLD的控制時(shí)序進(jìn)行

2010-08-26 16:06:20 31

31 摘要:以Altera公司MAX700舊系列為代表,介紹了CPLD在DSP系統(tǒng)中的應(yīng)用實(shí)例。該方案具有一定的普遍適用性DSP的速度較快,要求譯碼的速度也必

2006-03-11 17:39:49 1464

1464

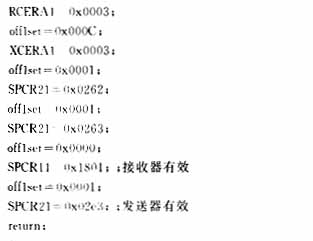

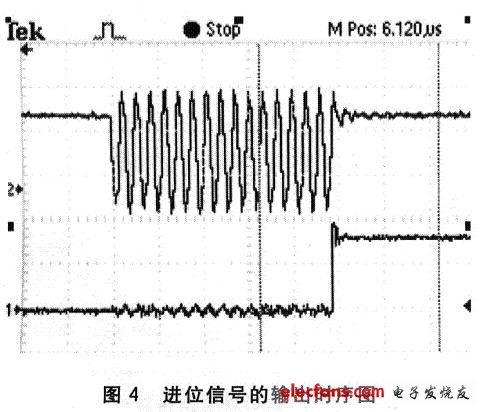

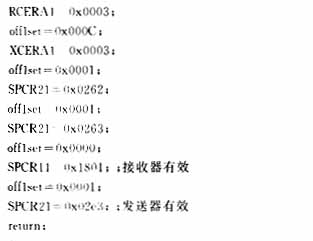

介紹了SPI通信協(xié)議,并著重介紹了TI公司生產(chǎn)的TMS320C5402 DSP用于SPI協(xié)議通信時(shí)的串口配置方法和接口電路設(shè)計(jì)實(shí)例,最后給出了串口McBSP的配置程序。

2009-05-06 20:17:55 2345

2345

【摘 要】 利用DSP和CPLD來設(shè)計(jì)寬帶信號(hào)源,將DSP軟件控制上的靈活性和CPLD硬件上的高速、高集成度和可編程性有機(jī)地結(jié)合起來,一方面使得信號(hào)源控制簡單、可靠,同時(shí)保證產(chǎn)生

2009-05-16 19:06:01 1031

1031

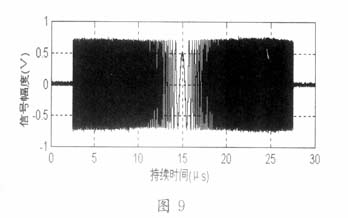

基于雙DSP的并聯(lián)控制系統(tǒng)中串行通信的研究

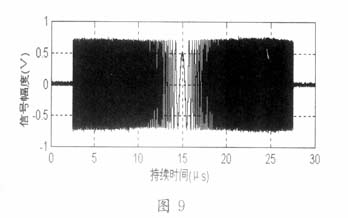

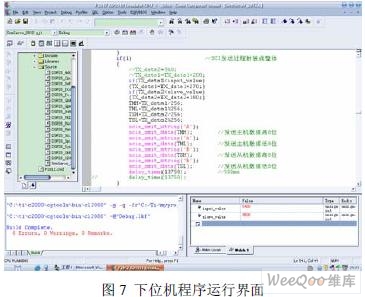

摘 要:概要地介紹了TMS320F2812 DSP 的基本性能,重點(diǎn)介紹了利用DSP 的SPI 模塊進(jìn)行雙DSP 同步串行通信,以及在Visual Basic 6

2010-01-08 10:30:07 1353

1353

基于DSP和CPLD的液晶模塊的設(shè)計(jì)

引言DSP芯片具有高速的信息處理能力、較好的系統(tǒng)支持、硬件配置強(qiáng)等優(yōu)良技術(shù)和較低的價(jià)格特性。嵌入式系統(tǒng)的實(shí)時(shí)性好、占用資

2010-01-21 10:31:13 744

744 基于DSP和CPLD 可重構(gòu)數(shù)控系統(tǒng)的設(shè)計(jì)與仿真

1、前言

隨著計(jì)算機(jī)技術(shù)的高速發(fā)展,各工業(yè)發(fā)達(dá)國家投入巨資,對(duì)現(xiàn)代

2010-02-09 10:52:11 576

576

基于SPI方式DSP外部E2PROM接口設(shè)計(jì)

0 引 言

近年來,隨著DSP技術(shù)的普及、高性能DSP芯片的出現(xiàn),DSP已越來越多地被廣大的工程師所接受,

2010-01-06 14:10:53 1909

1909

提出一種測(cè)量儀器的多處理機(jī)分布式控制方案, 并對(duì)DSP 與移植了Linux 操作系統(tǒng)的ARM之間SPI 通信設(shè)計(jì)進(jìn)行了著重闡述。對(duì)于這樣的特定系統(tǒng), 首先要完成Linux 下的SPI 驅(qū)動(dòng)程序開發(fā), 然后才

2011-06-14 17:25:58 127

127 本文的設(shè)計(jì)師基于DSP和CPLD搭建的智能IED(Intelligent Electronic Device,智能電力監(jiān)測(cè)裝置)可以同時(shí)采集多路信號(hào),并通過FFT算法得到電網(wǎng)運(yùn)行的關(guān)鍵數(shù)據(jù)

2011-07-02 11:15:58 1277

1277

本文通過使用IDT70261雙端口RAM,實(shí)現(xiàn)了ARM與TMS320C6211 DSP之間的高速實(shí)時(shí)數(shù)據(jù)通信,給出了雙端口RAM 與TMS320C6211和ARM的硬件連接圖和ARM驅(qū)動(dòng)編寫細(xì)節(jié)。

2012-07-27 11:33:12 3643

3643

DSP之spi_loopback教程,很好的DSP自學(xué)資料,快來學(xué)習(xí)吧。

2016-04-15 17:00:14 34

34 基于DSP_CPLD的開關(guān)磁阻電機(jī)的控制器設(shè)計(jì),有興趣的同學(xué)可以下載學(xué)習(xí)

2016-04-26 17:53:46 37

37 PC機(jī)與CPLD通信問題的研究

2017-01-19 21:22:54 5

5 本應(yīng)用筆記提供了一個(gè)例子的硬件和軟件接口的串行外設(shè)接口(SPI)RTC與摩托羅拉DSP,有一個(gè)內(nèi)置的SPI接口模塊。這個(gè)例子使用了摩托羅拉DSP演示工具作為電路的基礎(chǔ)。

2017-04-12 16:29:10 18

18 基于DSP_CPLD的四電動(dòng)舵機(jī)伺服控制器設(shè)計(jì)

2017-10-20 08:24:04 4

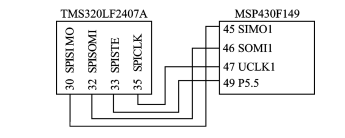

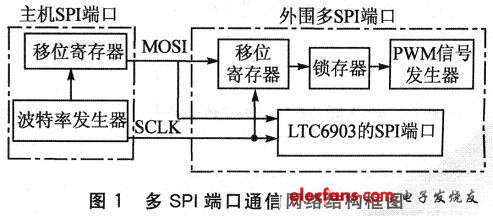

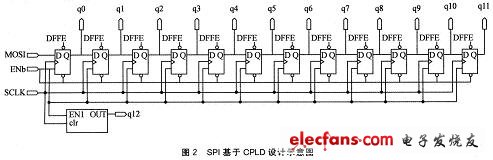

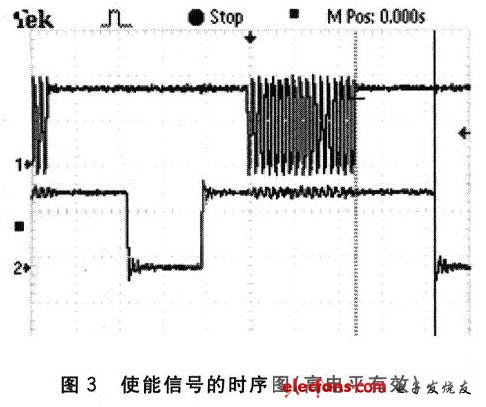

4 。本文以一種超聲波電機(jī)運(yùn)動(dòng)控制裝置為應(yīng)用背景,討論了基于CPLD的DSP控制芯片多SPI端口通信技術(shù)。 串行同步外設(shè)端口(SPI)通常也稱為同步外設(shè)端口,具有信號(hào)線少、協(xié)議簡單、傳輸速度快的特點(diǎn),大量用在微控制器與外圍芯片的通

2017-10-24 10:57:56 2

2 數(shù)據(jù)雙向通信,TMS320F2812 DSP芯片內(nèi)部集成了一個(gè)SPI模塊,方案提出了一種基于SPI通信接口的兩片DSP的雙向通信和任務(wù)同步,兩片DSP中固定一片作為SPI通信主機(jī),另一片作為SPI通信從機(jī)[1],最后提出通信故障的解決辦法。 1 DSP SPI外設(shè)接口模

2017-10-30 15:00:04 10

10 DSP參考程序spi

2018-04-10 15:46:46 11

11 隨著數(shù)字信號(hào)處理器(DSP)在系統(tǒng)控制領(lǐng)域中的廣泛應(yīng)用,控制各系統(tǒng)的DSP 之間 通信問題也越來越突出。利用DSP 本身的高速同步串行接口(SPI)模塊,可以讓DSP 直 接對(duì)接實(shí)現(xiàn)芯片間的同步串行

2019-02-06 08:56:00 6115

6115

項(xiàng)目中需要使用CPLD完成一部分算法設(shè)計(jì),參數(shù)由AVR給出,因此需要完成AVR和CPLD的通信。因此寫了一個(gè)測(cè)試程序。CPLD掛在AVR的數(shù)據(jù)和地址總線上,AVR使用ATmega128,在CPLD中設(shè)置幾個(gè)寄存器,通過AVR讀寫寄存器來實(shí)現(xiàn)兩者之間的通信。

2019-06-03 15:24:28 1012

1012 )數(shù)據(jù)通信速率至少是UART通信的115200波特率PCB上MCU與CPLD之間通過3個(gè)普通IO引腳連接二、功能分析MCU與CPLD之間有3根線,那么可以選擇UART通信或者SPI通信方式。由于CPLD無法通知MCU數(shù)據(jù)傳輸?shù)拈_始與結(jié)束,MCU需要自行判別,那么MCU可以通過中斷方式來檢測(cè)

2021-10-25 10:21:08 15

15 SPI簡介SPI是一種串行外圍設(shè)備通信接口,高速全雙工通信總線,主要用于通信速率較高的場(chǎng)合。SPI硬件連接硬件連接圖如下:SPI通訊使用3條總線及片選線,總線分別為:SCK、MOSI、MISO

2021-11-24 15:06:04 49

49 DSP芯片(master):TMS320F28069FPGA芯片(slave):Spartan-xc6slx25-2ftg256SPI協(xié)議:SCK:5MHz數(shù)據(jù)長度:8ByteFalling

2021-12-05 17:21:15 34

34 本文目的是通過SPI的通信方式進(jìn)行OLED的顯示,同時(shí)與之前學(xué)的I2C通信方式進(jìn)行對(duì)比,在實(shí)踐中學(xué)習(xí)SPI通信。目錄(一)SPI簡介(一)SPI簡介

2021-12-08 09:06:09 31

31 SPI通信分析許久不更,想你們了。SPI 模式的配置SPI通信配置STM官方的芯片手冊(cè)中對(duì)于SPI通信模式的配置過程,CPHA和CPCL的配置對(duì)于通信模式的影響如下圖所示:note :中斷模式

2021-12-22 19:12:41 2

2 SPI簡介SPI是一種串行外圍設(shè)備通信接口,高速全雙工通信總線,主要用于通信速率較高的場(chǎng)合。SPI硬件連接硬件連接圖如下:SPI通訊使用3條總線及片選線,總線分別為:SCK、MOSI、MISO

2021-12-22 19:13:53 2

2 基于DSP28035的模擬SPI————你真的理解SPI通信嗎?? 你真的理解SPI是怎么通信的嗎?SPI通信時(shí),什么時(shí)候發(fā)送數(shù)據(jù)?什么時(shí)候數(shù)據(jù)采樣?我們?cè)谧瞿MSPI時(shí)怎么體現(xiàn)出SPI的四種工作

2021-12-22 19:16:16 7

7 STM32模擬SPI通信協(xié)議SPI的簡介:SPI是串行外設(shè)接口的縮寫,是一種高速的,全雙工、同步的串行通信總線;SPI也可以實(shí)現(xiàn)一主多從,而實(shí)現(xiàn)一主多從是通過CS片選來實(shí)現(xiàn),于IIC有些不同;SPI

2021-12-22 19:20:00 21

21 SD卡操作分為SPI模式與SDIO模式,這里選擇SPI模式,DSP為SPI主機(jī),SD卡為從機(jī),本文對(duì)SD卡SPI通信進(jìn)行說明,關(guān)于SPI雙機(jī)通信后續(xù)有時(shí)間也會(huì)特別寫篇文章進(jìn)行說明SPI---串行外設(shè)

2021-12-22 19:35:41 14

14 基于DSP+CPLD的低壓斷路器群組控制.pdf

2022-02-07 11:18:31 4

4 本應(yīng)用筆記提供了用于將串行外設(shè)接口(SPI)RTC與內(nèi)置SPI接口模塊的摩托羅拉DSP連接的硬件和軟件示例。本示例使用摩托羅拉DSP演示套件作為電路的基礎(chǔ)。

2023-01-10 11:45:22 840

840

快速 SPI 端口可通過 GPIO 引腳進(jìn)行位沖擊,并作為具有 SPI 端口的 8051 兼容微控制器的低成本替代方案。本應(yīng)用筆記所示的代碼利用8051特有的特性,使用最少的額外代碼創(chuàng)建快速SPI端口。

2023-01-12 16:18:32 592

592

現(xiàn)今的工控系統(tǒng)中,為了提高系統(tǒng)的實(shí)時(shí)性和適用性,一般采用DSP來完成核心算法與控制,而使用MCU來實(shí)現(xiàn)人機(jī)對(duì)話,以實(shí)現(xiàn)實(shí)時(shí)控制功能。這樣,DSP和MCU需要一種高效的數(shù)據(jù)總線來完成它們之間的大量數(shù)據(jù)傳送。SPI總線由于占用的接口線少,通信效率高,并且大部分處理器芯片都支持,因而是一種理想的設(shè)計(jì)方案。

2023-07-23 17:11:09 1127

1127

電子發(fā)燒友網(wǎng)站提供《基于MSP430單片機(jī)MCU與DSP的SPI通信設(shè)計(jì).pdf》資料免費(fèi)下載

2023-10-30 10:14:15 4

4

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論