摘要:MPC860 是PowerPC系列產品,PowerPC 可運行于多種操作環境,廣泛應用于便攜式設備到服務器TMS320C6000 系列是1997 年美國TI公司推出的DSP芯片,這種芯片是定點、浮點兼容的DSP系列,它們提供了HPI(Host Port Inter face)接口,文中介紹了TMS320C6000與MPC860之間HPI接口的硬件設計。經實驗驗證,MPC860可以對擴展總線進行讀操作,也可以寫操作,該設計方案已經實現了初步的功能。因此具有一定的實用性。

1 TMS320C6000的主要特點

TMS320C6000系列DSP(數字信號處理器)是TI公司最新推出的一種并行處理的數字信號處理器。TMS320C6000片內有8 個并行的處理單元。分為相同的兩組。它的體系結構采用超長指令字( VLIW) 結構,單指令字長為32 bit。8個指令組成一個指令包。總字長為8×32= 256 bit.芯片內部設置了專的指令分配模塊,可以將256 bit 的指令包同時分配到8 個處理單元,并由8個單元同時運行。芯片的最高時鐘頻率可以達到300MHz,通過片內的鎖相環( PLL) 將輸入時鐘倍頻獲得。當片內的8個處理單元同時行時。最大處理能力可以達到2400MIPS。

2 TMS320C6000的擴展總線

目前,TMS320C6000系列中只有C6202和C6203具有擴展總線。它們是在C6201/C6701主機接口(HPI)的基礎上發展起來的。

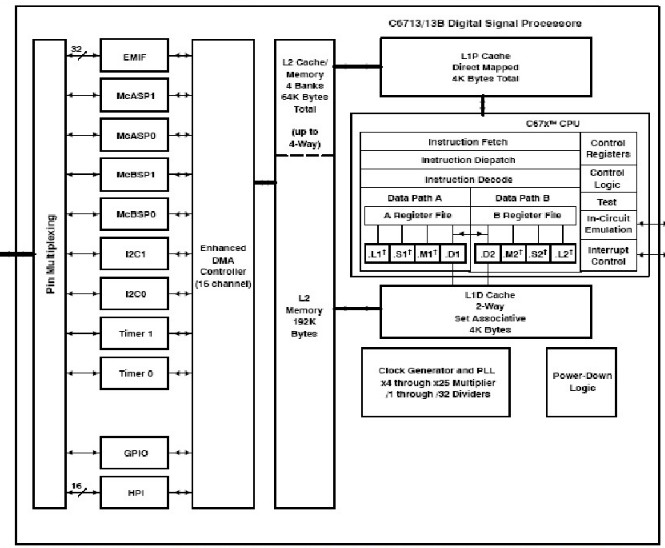

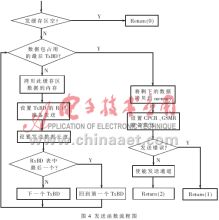

擴展總線從結構上可以分為兩部分:I/O接口和主機接口,如圖1所示。

?

擴展總線是一個32bit寬的總線,支持與異步外設、異步/同步FIFO、PCI橋及外部主控處理器的接口。它同時還提供了一個靈活的總線仲裁機制,可以進行內部仲裁,也可以由外部邏輯完成。

I/O接口,擴展總線共管轄4個XCE外部空間,4個空間可以分別配置成兩種工作模式:異步I/O模式和同步FIFO模式。這兩種模式可以在一個系統中同時工作。異步I/O模式的接口信號時序與EMIF類似,具有可編程程度高的特點。這一模式下,擴展總線接口的4根地址信號使得每個XCE空間最多可以掛接16個外部設備。FIFO模式則提供了與同步FIFO無縫接口的能力,可以直接控制1個進行讀操作的同步FIFO或4個進行寫操作的同步FIFO。借助少量外部邏輯,每個XCE空間可以管理16個讀操作FIFO或16個寫操作FIFO。擴展總線I/O口與DSP的其他存儲空間由DMA控制器進行連接。

主機接口也有兩種工作模式:同步和異步。同步模式提供了主控和從屬兩種工作方式,此時地址信號和數據信號復用相同的管腳。異步模式只有從屬功能,它與C6201/C6211/C6701/C6711的HPI操作完全類似,只是數據寬度為32bit。異步模式可以用來與其他微處理器接口。擴展總線主機接口與DSP存儲器的連接由DMA輔助通道完成。

在同步主機接口模式下,主機的數據與地址信號復用,并且與i960Jx兼容。目前主流的PCI接口芯片都采用i960總線作為芯片內部總線,這樣C6000與PCI總線接口時,需要的外部邏輯可以減少到最少。尤其在作為從屬處理器時,同步主機接口同樣可以非常方便地與其他一些通用處理器接口。C6202的擴展總線還具有突發傳輸的能力。本文即利用這一方式實現MPC860與C6202擴展總線的接口。

C6202處理器的工作頻率最高可以采用50MHz,經內部4倍頻后升至200MHz,每個時鐘周期最多可以并行執行8條指令,從而可以實現1600MIPS的定點運算能力,完成1024點定點FFT的時間只需70μs。

3 MPC860介紹

MPC860 是摩托羅拉公司的單片集成嵌入式微處理器, 它內部集成了微處理器和通信領域常用的外圍組件, 特別適用于互聯網絡和數據通信市場。MPC860 通信處理器可根據用戶要求提供2~4 個串行通信控制器、不同規格的指令和數據緩存及各種級別的網絡協議支持。

該產品專為寬帶接入設備如:遠程接入路由器、DSLAM、接入集線器、LAN /WAN 交換機、PBX 系統和網關等設計。

MPC860包括3個主要模塊:Power PC核心、系統接口單元(SIU) 、通信處理模塊(CPM)。PowerPC是主要的處理機單元,通常稱為Embedded Pow er PC 核心(或EPPC),它包括高速緩存和存儲器管理單元(MMU),在40 MHz 時鐘時為50 MIPS 指令速度;第二個主要模塊為系統接口單元,它的主功能是提供內部總線和外部總線的接口;第三個主要模塊為通信處理機模塊,CPM 在不同的通信設備如SCC和SMC上發送接收數據通信,通信設備可以獨立工作。

4 擴展總線接口實現

MPC860內部集成了嵌入式的PowerPC核和使用特定RISC處理器的通信處理模塊(CPM)。這個雙處理器結構優于傳統結構,因為CPM可以從嵌入式的PowerPC核卸出外圍任務。

4.1 接口實現

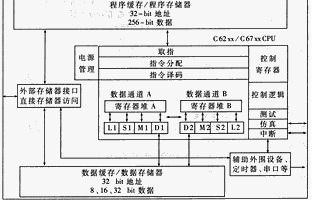

同步主機接口模式下,C6202和MPC860的接口如圖2所示。盡管圖2中的C6202處于從方式,但還是具有擴展總線仲裁的能力,用于異步I/O和擴展總線的FIFO接口。只有當這兩個設備共享總線時,MPC860內部的仲裁才被使用。

?

擴展總線的管腳定義

擴展總線管腳 MPC860的管腳 功能定義

XCNTL A[29] MPC860用于控制信號的地址位,A31是MPC860地址總線的LSB

XBLAST

觸發傳輸指示,XBLAST的極性(在這個例子高有效)由復位時XD[13]的上拉電阻決定

?

讀寫存取指示,

的極性(在這個例子高有效)由復位時候的XD[12]的上拉電阻決定

?

XD[31:0] D[0:31] MPC860用D[0:31]作為32位的接口。D0是MPC860數據總線的MSB,而XD31是擴展總線的MSB

XCLK CLKOUT 自身(擴展)總線時鐘

XHOLD 間接邏輯需與 擴展總線仲裁信號

XHOLDA BR、BG 注意內部擴展總線仲

和BB連接 裁已經處于使能端

新的轉移開始指示

?

A[28:0] MPC860的地址解碼從而產生

信號

?

TSIZE[1:0]、 字節使能用TSIZE和A

?

A[31:30] [31:30]的解碼來實現

SETA bit 在MPC860選擇寄存器中設置為1,用于指示

由外部總線產生

?

MPC860的內部總線仲裁處于禁止狀態,相反擴展總線的仲裁處于使能狀態。DSP的字節使能信號由TSIZE[1:0]和MPC860的地址線A[31:30]通過解碼得到,DSP字節使能換算表如表1所示。

?

4.2 自舉配置

MPC860及擴展總線把數據總線的上拉和下拉電阻用于硬件復位的BOOT配置,MPC860和DSP需要不同的上拉電阻配置。方法之一就是用總線開關。在這個例子中用SN74CBT16390(2個16bit和32bit之間FET復用/解復用總線開關)在復位的時候分離MPC860和DSP的數據總線,允許每一個設備有自己不同的復位配置字。方法之二就是首先硬件復位(復位的過程中,XBUS的上拉和下拉電阻用于配置MPC860),而DSP復位應該在MPC860之后。在DSP復位之后,MPC860有效地驅動數據總線上用于配置DSP的數據值,從而DSP將被配置。

由于兩個設備都可以運行在內部總線仲裁使能或者禁止方式,所以內部擴展總線仲裁處理總線的仲裁。不管內部還是外部的仲裁配置都在系統復位時設置。如果設備處于外部仲裁,那么在MPC860從數據總線上取樣硬件復位配置字的候,MPC860的ERAB位必須設置為1;而當DSP從復位到內部總線仲裁的數據總線上取樣硬件復位配置字的時候,TMS320C6000的XARB位必須設置為1。

通過在XD[31:0]上拉和下拉電阻的擴展總線自舉配置如下:

字段(field) 定義

BLPOL 當DSPs作為擴展總線的從屬時,XBLAST信號的極性BLPOL=1,XBLAST是高有效

RWPOL 擴展總線讀/寫信號的極性,RWPOL=1, 為

?

HMOD 主機(host)的模式(對應于HPIC中的XB狀態),HMOD=1,外部的主機接口處于同步的主/從模式

XARB 擴展總線仲裁使能(對應于XBGC中的狀態), XARB=1,內部擴展總線仲裁處于使能狀態

FMOD FIFO模式(對應于XBGC中的狀態)

LEND 小端模式,LEND=1,系統運行在小端模式

BootMode[4:0] 設定設備自舉模式,包括主機口自舉、ROM、boot、存儲器映射選擇

為使工作準確,MPC860的高速緩存必須關閉使能。數據緩存是否使用,只要將相應的狀態寫入DC_CST寄存器。在禁止狀態,緩存標志狀態位被忽略,訪問將通過總線傳輸。數據緩存在復位后默認為禁止。禁止的數據緩存不影響數據地址的邏輯轉換,在MSRDR位的控制下繼續進行,任何寫入DC_CST寄存器的操作必須優先于一個同步指令,則確保在數據存儲時,數據緩存的使能變化。由于總線錯誤或者執行特定的直接緩存線性控制時,數據緩存產生一個中斷信號,緩存進入禁止狀態,類似于禁止。每一頁都有不同的存儲控制屬性, MPC860支持緩存禁止(CI)、 寫入(WT)和監視(G)屬性,但不支持存儲器的一致性。對于要求存儲一致性的頁,必須編程設置為緩存禁止。G屬性用于映射那些對不確定存儲比較敏感的I/O設備,有G屬性的頁使存儲強行停止,除非是非敏感性存儲或者被核(core)取消。是否可緩存的區域必須定義,對于主要存儲區的寫回(write-back)或寫通(write-through)模式,必須在使數據緩存使能之前通過初始化MMU來選擇。

電子發燒友App

電子發燒友App

評論