引言

?????? 用于實時控制的嵌入式系統有多路模擬量輸入,要求對多路輸入進行連續掃描并進行高速高精度處理,具有16位16路差分輸入通道的ADS7805能夠滿足系統通道數量及精度的要求。通道的快速切換及系統關鍵控制信號的產生成為制約系統性能的瓶頸,利用TMS320LF2407A豐富的I/O接口及高頻時鐘,配合EPM3032A靈活的譯碼功能,則可以控制ADS7805進行多個通道的高精度高速數據采集,由于采用了DSP與CPLD等可編程器件,系統可操作性得到了保證,也極大地簡化了硬件電路。

1 系統結構設計

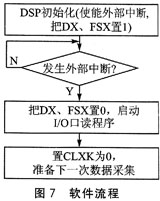

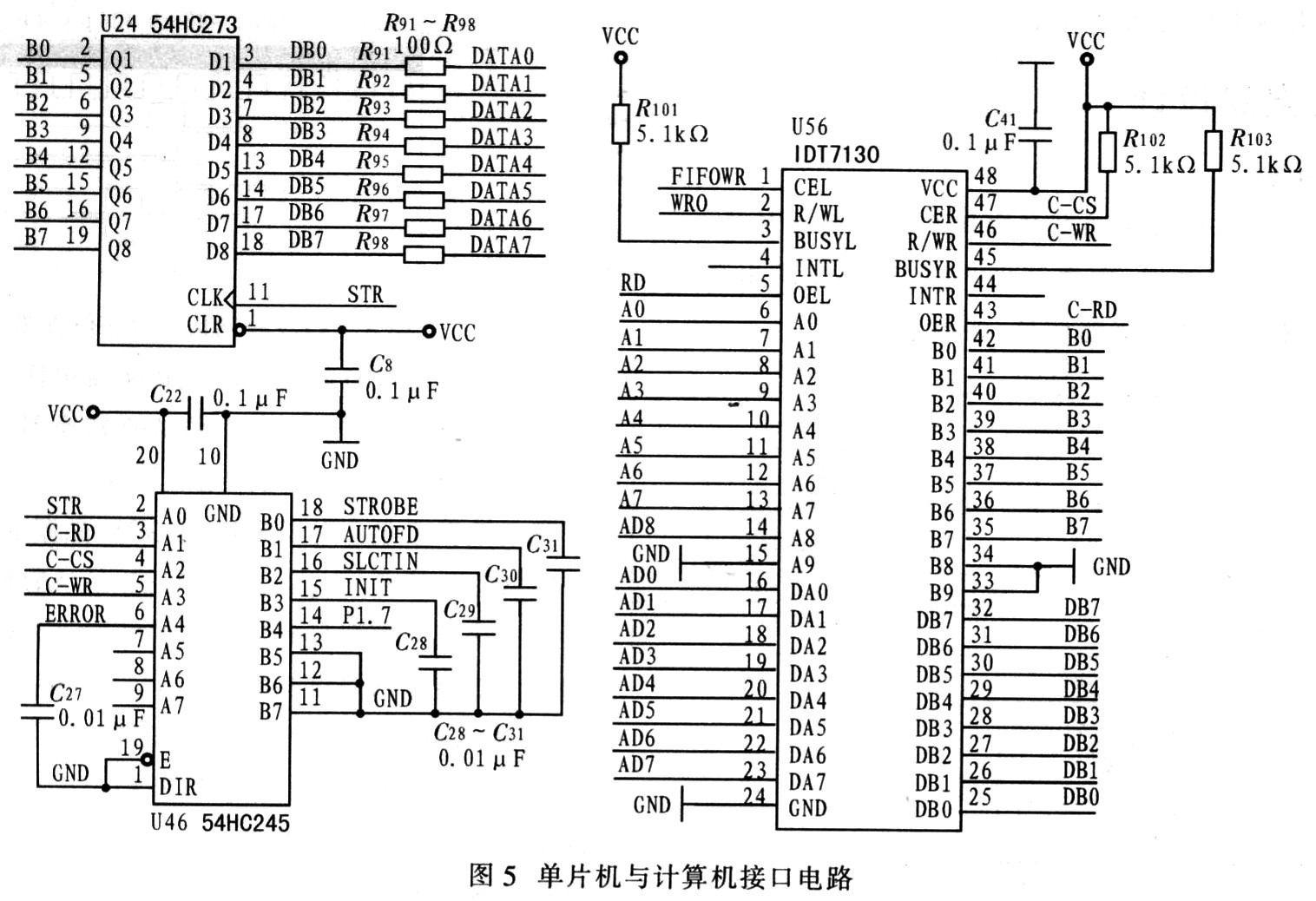

????? 系統以DSP與CPLD為核心構建,模擬信號從多路復用器接入,利用CPLD使能或禁止其輸出,DSP的I/O引腳控制通道的選擇,當選通一路時,多路復用器輸出差分再經過運放轉為單端信號作為ADC的輸入,ADC片選由DSP的I/O引腳控制,啟動由CPLD控制,當片選有效時啟動ADC,并按照規定的時序控制片選信號,ADC開始工作,轉換結果輸出到CPLD譯碼得到的地址。ADC與DSP之間的緩沖器件用來做電平匹配,利用CPLD將其鎖定在選通狀態。ADC在轉換完成時發起一個外部中斷到DSP,請求DSP處理轉換結果[1]。

2 硬件設計

模擬信號輸入到多路復用器ADG726(ADI公司產品),1.8~5.5V電源供電,由引腳VDD輸入;接受16路差分或32路單端模擬信號輸入(引腳S1A~S16A,S1B~S16B)。DA,DB為差分信號輸出引腳;A0~A3是通道選擇控制引腳。片選引腳CSA、CSB低電平有效。引腳EN、WR分別為芯片使能和寫使能,EN低有效,WR上的有效電平波形如圖2所示。

信號從DA,DB引腳輸出之后,在到達ADC之前先轉成單端信號,這里采用ADI公司易用型運放AD620,±12V模擬電源供電。

ADI公司生產的低功耗16位模數轉換器ADS7805為逐次逼近型結構,+5V單電源供電,標準±10V輸入,最小采樣率100KSPS。REF引腳接內部或者外部參考電壓,用于設定模擬輸入電壓范圍,與模擬地之間連接一個2.2μF的鉭電容,本設計采用內部參考;VANA引腳是+5V模擬電源輸入端,并聯一個0.1μF和一個10μF的鉭電容接到模擬地上;VDIG為數字電源輸入端,直接連到VANA上。AGND1和AGND2是模擬地;CAP引腳為參考緩沖電容,與模擬地之間接一個2.2μF鉭電容;DGND是數字地;BYTE引腳電平決定轉換結果的字節位置,低電平時引腳6到13輸出結果的高8位,引腳15到22輸出結果的低8位,高電平時正好相反。當啟動引腳R//C為低時,片選CS的下降沿激活一次轉換。BUSY在轉換時保持低電平,轉換完成時變高。轉換結果由16個引腳并行輸出,經過緩沖74LVTH16245A做5V到3.3V的電平轉換到DSP,輸出引腳為三態驅動。

系統的主控制器采用TI(德州儀器)公司的TMS320LF2407A,3.3V靜態CMOS工藝,40MIPS,具有16位地址總線,16位數據總線,3個獨立的存儲空間,包括可用的64K字程序空間,35.5K字數據空間以及64K字I/O空間。訪問不同的存儲空間時,DSP有相應的引腳作為選通信號,即PS對應程序空間,DS對應數據空間,IS對應I/O空間,均為低電平有效。本設計將ADC映射到I/O空間。TMS320LF2407A具有豐富的通用數字I/O口,利用其中一個對ADS7805進行啟動控制。通道選擇也由數字I/O實現,利用DSP 4個I/O引腳作為ADG726的4-16譯碼輸入可選擇系統的16路差分。設計將ADC的BUSY引腳接到DSP的外部中斷引腳XINT1上,當BUSY上升沿到來時,將觸發DSP外部中斷,中斷的極性、優先級均可軟件設定。EMP3032A是ALTERA公司推出的高性價比CPLD,在系統中用來控制ADC的引腳CS,配合引腳R//C來激活ADC,對CS的控制同時也將ADC映射在了DSP的I/O空間,因為使CS變為有效的控制邏輯來自于CPLD對DSP的4根地址線(A15到A12)及IS的譯碼。多路復用器的寫使能由CPLD控制,即ADG726也被映射在DSP的I/O空間,這樣設計的優點是對映射地址執行一個讀操作就能得到需要的時序,雖然利用DSP的數字I/O引腳也能實現,但是需要在軟件中模擬信號的時序,實現由高到低、延時并上跳變的過程,相對較復雜[2-4]。

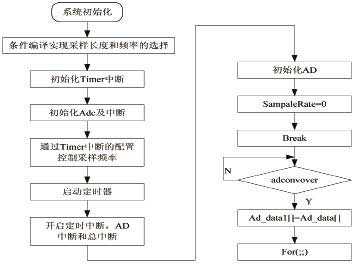

3 軟件設計

首先編寫CPLD程序對ADG726及ADS7805進行地址譯碼,然后對CPLD在線編程生成譯碼電路。

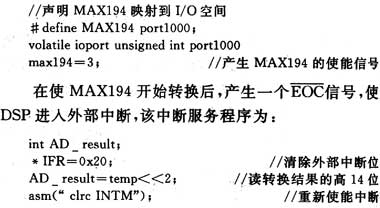

/*--adc mux--*/

assign mux_wr=~((addr==4'h3)&(~is)&(~dsp_wr));//ADG726映射到I/O空間的地址0x3000~0x3FFF,得到寫使能信號

assign mux_en=0;//ADG726的使能引腳始終有效

/*--adc--*/

assign buffer_cs=(~(addr==4'h0))|is;//ADC映射到I/O空間的地址0x0000~0x0FFF,得到緩沖器的片選信號

assign adc_cs=~((addr==4'h0)&(~is)&dsp_rdwr);//得到ADC的片選信號

在DSP程序中,對0x3000~0x3FFF的任意地址執行一個讀操作,由DSP選擇的通道就被選通,信號由ADG726輸出到運放AD620,差分轉單端后輸出到ADC。通過寫數字I/O的控制寄存器,先將R//C拉低,再對I/O空間的0x0000~0x0FFF執行一個讀操作,然后將R//C拉高,就啟動了ADC。讀0x0000~0x0FFF 其中任一個地址產生低電平的CS信號,該信號保持的時間由訪問I/O空間的等待時間決定,通過設置等待狀態寄存器來保證獲得有效的延時時間。

/*--設置等待狀態寄存器--*/

WSGR = 0x01C0;//bit8-6=111,訪問I/O空間時插入7個等待狀態

ADC轉換完成置BUSY為高電平,向DSP申請中斷,相應中斷被使能之后DSP開始處理中斷服務程序,完成數據的讀取與其他處理。

/*--初始化ADC字程序--*/

*MCRA &= 0xFC3F;//配置4個I/O引腳bit9-6為通用功能用于ADG726通道選擇

*MCRB &= 0xFF7F;//bit7對應的I/O引腳控制R//C??

*PADATDIR |= 0xC000;//bit7-6配置為輸出,對應通道選擇的兩個引腳

*PBDATDIR |= 0x0300;//bit1-0配置為輸出,對應通道選擇的另兩個引腳

*PCDATDIR |= 0xC000;//bit6配置為輸出,對應R//C

*XINT1CR |= 0x7;//上升沿有效,低優先級,使能外部中斷

*IMR |= 0x20;//使能內核對應的中斷??

/*--聲明ADG726,ADC映射到的存儲單元--*/

#define???? AD_Output?? port0000

volatile??? ioport????? unsigned int??? port0000;

#define???? mux_ad????? port3000

volatile??? ioport????? unsigned int??? port3000;

/*--ADG726通道選擇函數--*/

*PADATDIR &= 0xFF3F;//bit7,bit6清0

*PBDATDIR &= 0xFFFC;//bit1,bit0 清0

*PADATDIR |= ( nChlNum & 0x3 ) << 6;//設置bit7,bit6

*PBDATDIR |= ( nChlNum & 0xC ) >> 2;//設置bit1,bit0

mux_ad = 0;//產生寫使能信號

/*--主程序--*/

int temp;

……

AD_Init();//初始化

ADC_MUX(13);//選擇通道13

/*--啟動ADC--*/

*PCDATDIR &= 0xFF7F;//使AD_R/C*變低

temp=AD_Output;//產生有效的AD_CS*

*PCDATDIR |= 0x80;// 使AD_R/C*變高?

for(;;);//等待ADC中斷

......

/*--中斷服務程序--*/

int???? AD_result;

*IFR = 0x20; //清除中斷標志位,以響應后續中斷

AD_result = AD_Output;//讀轉換結果

asm(“? clrc INTM”);//重新使能中斷,因為一進服務程序中斷就被禁止了

4 結束語

本文設計了基于TMS320LF2407A與EPM3032A的ADS7805多通道采集系統,介紹了系統的工作原理,詳細描述了ADS7805、DSP及CPLD之間接口的硬件與軟件設計,該方案已在筆者參與研制的嵌入式實時控制系統中得到了成功應用。

電子發燒友App

電子發燒友App

評論