在IC卡公用電話系統中,在線式公用電話由于其具有保密性高、可擴展性強等特點,已逐漸獲得人們的青睞。這種公用電話系統被置于終端和交換機之間,對兩者的信號進行調制、解調以及其它的運算,來完成諸如卡驗證、終端維護、多媒體信號傳輸等工作。與軟件無線電相類似,這種系統的硬件平臺通用性很強,數字信號處理的算法將由專門的芯片來承擔,所以這種系統可以兼容目前在電話線上應用的各種調制解調方法,也可以適應未來出現的其它調制解調標準。

由此可以看出,要實現這樣一個系統,數據采集是一個非常重要的方面。為了節約成本和提高DSP芯片的利用率,在這個系統中,一片DSP要承擔16個通道的運算。從數據采集的角度來說,由于通道同時對應著終端和交換機兩端,故DSP需要高速采集32個通道的數據。另外,高速ADC的出現和DSP性能的不斷提高也對系統將來的升級提出了要求。所以對數據采集部分來說,高速、可擴展性是兩具非常重要的指標。實現的系統就是以這兩個指標為指導的。

目前的高速多通道數據采集系統一般有以下幾種實現方法:一是直接采用高速的多通道模/數轉換芯片,這些芯片有專門設計的與DSP接口的部分,但是這些芯片一般價格都非常昂貴;二是直接用FPGA完成整個的采集過程,這將耗費FPGA巨大的資源;三是DSP和模/數轉換芯片的地址以及數據總線直接相接,通過單片機控制轉換等過程,這種方法雖然便宜,但是可擴展性太差。綜上所述,提出一種通過CPLD實現接口,將模擬轉換通道映射到DSP的I/O設備空間甚至內存空間的方法。這種方法大大提高了DSP可以訪問的外設數目;同時由于DSP不直接與模/數轉換模塊接口,所以ADC芯片的升級或者替代都不會影響原來的數據采集;而且采用了時分復用方式讀取轉換完成的數據,因此這個系統數據采集速率可以達到所采用的ADC芯片輸出的最高速率。

??? DSP雖然在算法處理上功能很強大,但其控制功能是非常弱的;而CPLD本身并不具有內部寄存器,雖然可以用CPLD的邏輯塊來實現寄存器,但是這將耗費大量的CPLD資源。然而,CPLD的強項在于時序和邏輯控制。本文介紹的多路數據采集系統就是充分利用了DSP和CPLD的優點,將多個A/D轉換單元通過CPLD映射到DSP的I/O地址空間,利用CPLD屏蔽A/D轉換的初始化以及讀寫操作過程,使得DSP可以透過CPLD這個"黑匣子"快速、準確地獲取數據。

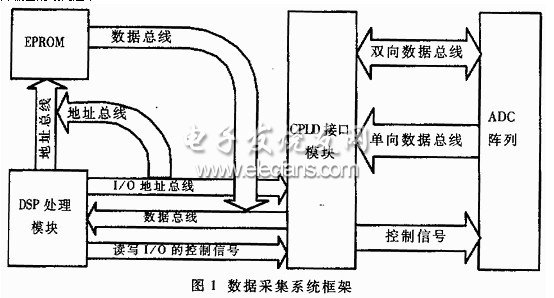

1 數據采集系統框架

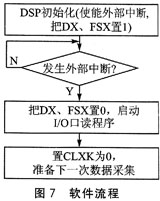

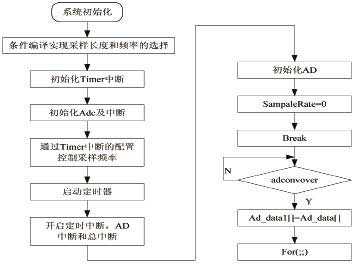

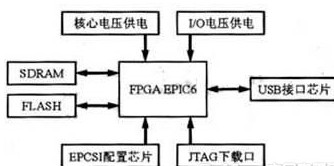

整個數據采集系統主要由DSP處理模塊、CPLD接口模塊和ADC陣列三個部分組成,如圖1所示。透過這樣一個結構,DSP可以在未知ADC的控制方式的情況下,定時地以訪問外設的方式來獲得總共32個通道的模/數轉換后的數據。

這樣的系統框圖只是完成了一個完整的數據采集功能,至于數據的處理以及DSP需要完成的其它功能,此圖并未涉及。但對于一個DSP系統來說,數據采集在硬件中占據了很大的比重,這也符合DSP芯片應用的原則:用軟件完成大部分的數字處理算法。

2 各功能模塊的實現

2.1 ADC陣列的實現

此數據采集系統的設計目標是完成32路信號的采樣,并且要求每路的采樣率為50kHz。所以,這樣一個系統達到的整體采樣率為32×50k=1.6MHz。

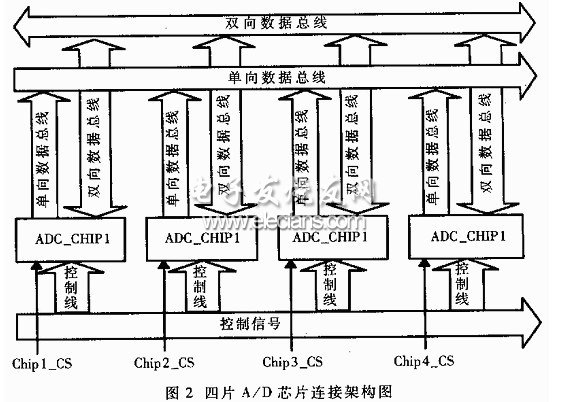

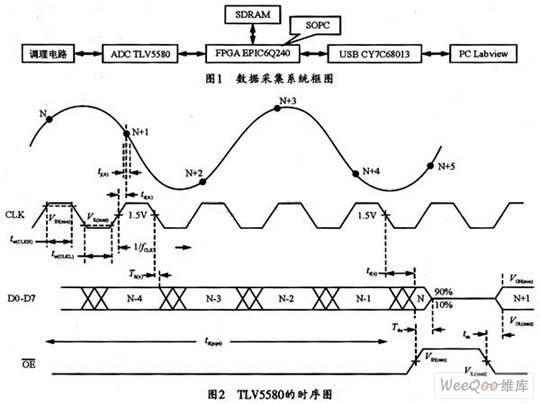

在模/數轉換環節,采用的A/D芯片一片一次可以同時完成4路轉換。為了達到設計目標,需要8片這樣的芯片。但是,如果直接將8片模/數轉換芯片的數據總線全部連接起來輸入到CPLD中或者將CPLD出來的某條控制信號線直接連接到8片芯片上,那么在驅上就會出現總是。基于此種考慮,此系統將8片芯片分成兩組,每組4片,然后從CPLD中引出兩組數據總線以及兩級控制總線分別對它們實現控制。這樣就能很好地解決芯片的驅動問題。圖2就是其中一組芯片的連接架構圖。

從這個架構圖可以看出,這4片A/D轉換芯片除了片選控制信號以外,其它的數據總線以及控制總線全部是分別連在一起的。將片選控制與其它控制分開的原因在于:芯片的初始化以及轉換過程需要同時完成,但是轉換后數據的輸出則分則完成。ADC控制時序框圖如圖3所示。

要實現這樣的控制時序,各個階段對芯片的片選控制如下:在初始化階段,所以A/D芯片的片選信號有效,此時可以對每片芯片寫入相同的模式選擇信號,同時啟動采樣脈沖和轉換脈沖;在轉換階段,所有片選信號全部無效,此時芯片本身在內部完成模/數轉換,同時將轉換完成的數據放置在芯片內部的寄存器中;在數據輸出階段,首先是第一片芯片的片選有效,此時若有一個脈沖下降沿到A/D芯片的RD端口,則芯片1的轉換完成,第一路數據將浮出到數據總線上,而其它芯片由于片選信號無效,雖然有RD輸入也不會有數據輸出,不會造成總線沖突。對于芯片1而言,接下來的幾個RD脈沖可以分別使得轉換完成后的幾路數據浮現在數據總線上。芯片1的數據全部輸出完成后,片選1無效,此時可使芯片2的片選信號有效。依此類推,就可以完成4片芯片的轉換及數據輸出。

2.2 CPLD接口模塊的實現

整個CPLD接口模塊實際上就是一片ALTERA公司的7000系列的CPLD(外部時鐘電路除外),它控制ADC模塊的初始化,同時接收并分析DSP過來的I/O端口讀取信號,為DSP和ADC之間搭起一個通道。

在DSP要求讀取數據時,CPLD將DSP過來的IOSTROBE作為A/D芯片的RD信號,同時對I/O地址總線的第3位至第5位譯碼產生A/D芯片的片選信號,這樣只要是地址按照每次遞增1的方式讀取數據,就可以使得8片A/D分時片選有效,完全符合上面提到的讀取數據的要求。另外,還依靠最高位地址確定CPLD到DSP的數據輸出總線是否定義成高阻態來避免總線沖突。

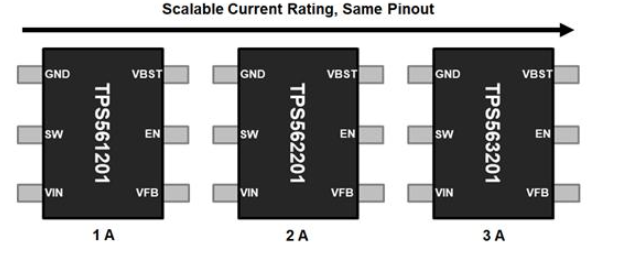

??? 由于A/D芯片是采用5V供電的,所以其輸出高電平將高于DSP輸入高電平所能承受的范圍。解決這個總是的方法之一是采用降壓芯片(比如LVT系列)用3.3V供電,3.3V供電可以承受5V的輸入,同時輸出也和3.3V兼容,但是這種方法需要單獨外接幾片LVT芯片,占據寶貴的PCB板空間;方法之二是給CPLD芯片提供雙電源,其中提供給I/O腳的電源為3.3V,此時輸入電壓可以和5V及3.3V系統兼容,同時電平可以達到3.3V,符合A/D芯片高電平最低電壓2.4V的要求。所以,數據總線通過CPLD到DSP實際上是因為電平轉換的需要。

2.3 DSP處理模塊

DSP處理模塊在硬件電路上是非常簡單的,主要由一片DSP芯片、一片EEPROm以及一片介于這兩者之間的用作電平轉換的LVT系列的芯片組成。

DSP通過地址總線可以區分訪問的模擬通道的標號。需要注意的是:由于采用的A/D芯片是通過對RD脈沖信號計數來確定訪問的是同一片芯片內部4路中的哪一路,所以實際上地址總線的低兩位是沒有選擇功能的,對一片A/D芯片訪問時,最后兩位地址一定要從00開始遞增到11,否則所讀取的數據就是亂的。例如,轉換完成后的DSP若想越過前兩個通道來獲得第3個通道的數據,它必須給出兩個讀取I/O端口的指令,緊接著這兩個指令后的讀取端口指令才可以獲得3個通道的有效數據。

當然,可以通過CPLD首先將所有轉換完成的數據緩存下來,然后分析I/O地址來將對應的通道的數據浮現到數據總線上。這樣做使得DSP可以自由地選擇需要訪問的通道,但需要比較大的緩存,利用CPLD作緩存是非常不經濟的。

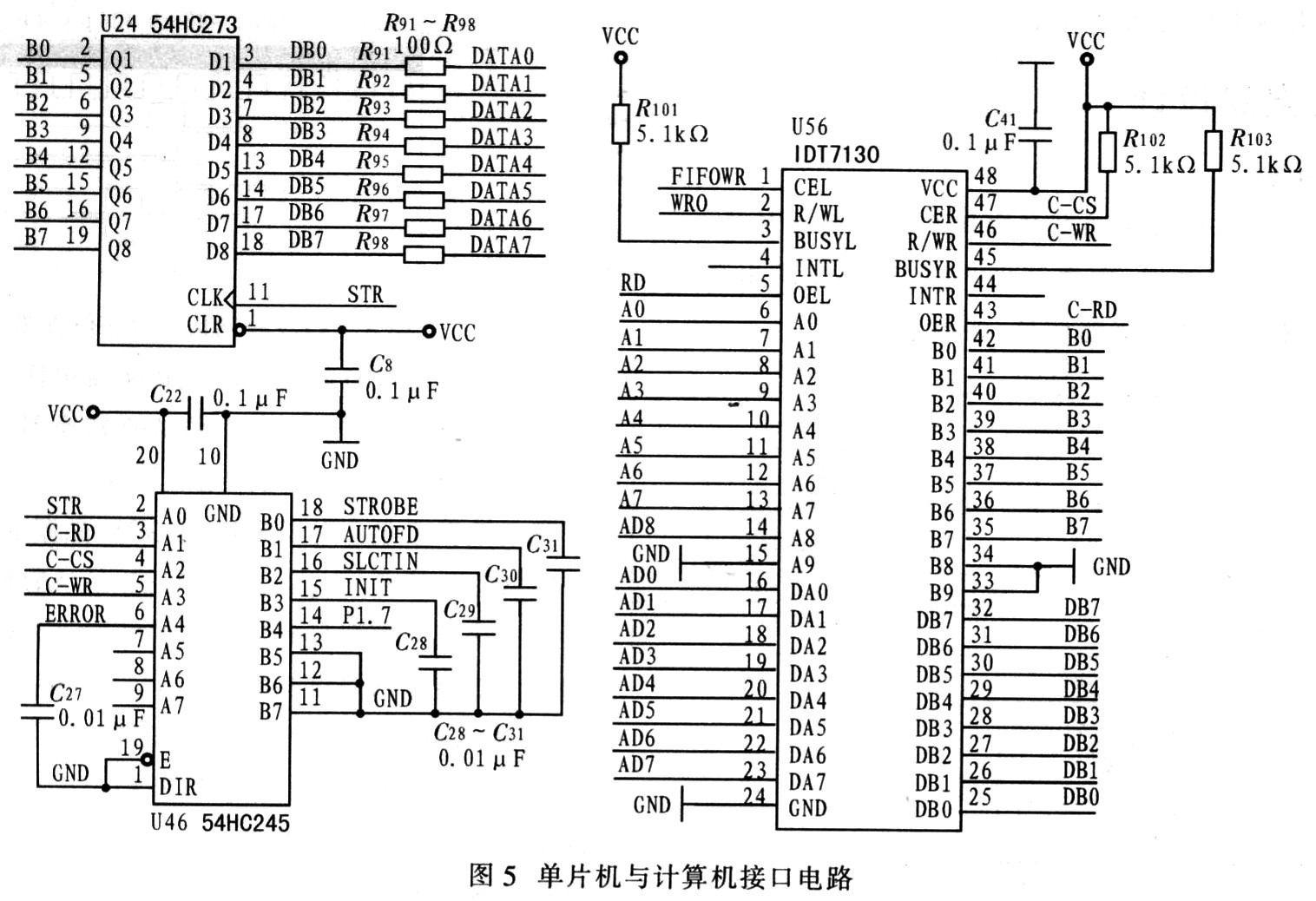

3 仿真和調試

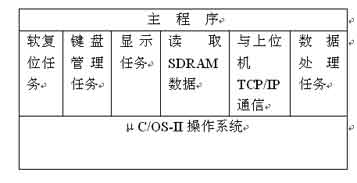

本系統的軟件開發主要包括兩部分,一是DSP讀取I/O口的程序,二是CPLD的時序控制程序。前一程序的開發采用的是TI公司的CCS開發環境,并且利用DSP內部的BOOTLOADER在起電時將存儲在外掛EPROM中的程序裝載進DSP的程序空間。而后一程序的開發采用的是ALTERA公司的MAXPLUSII,利用這個環境,完成了程序的編制、仿真以及時序分析,并在找出關鍵路徑的基礎上優化了整個芯片的內部延時。

在調試的過程中,利用DSP提供的JTAG接口實時地觀察采集進來的數據。當對32路模擬通道分別提供不同頻率的正弦信號時,可以看到相對應的通道的數字信號也按照固定的頻率來變化,并且各個通路不存在串擾的情況。經過測試獲得本系統的各種參數如下:

單路模擬信號采樣率:5kHz

系統模擬信號采樣率:50kHz×32=1.6MHz

單個采樣點讀取時間:80ns(受ADC芯片的限制)

DSP(5402)單指令周期:10ns

DSP讀取數據占用資源:((80÷10)×1.6×10 6)÷10 6=12.8mips

CPLD使用I/O口:48

CPLD使用Logic cells:80

由此說明這樣一個系統達到1.6MHz的采樣率時工作是穩定可靠的。

本系統的設計思想和方法不僅適用于多路數據采集,而且能有效地擴展DSP訪問外設的能力。實踐證明,這種系統在成本控制、可擴展性以及資源利用效率上都有非常大的提高。

電子發燒友App

電子發燒友App

評論