Cadence宣布業(yè)內(nèi)首個(gè)DDR4 Design IP解決方案在28納米級(jí)芯片上得到驗(yàn)證

2012-09-10 09:53:24 1403

1403 Cadence設(shè)計(jì)系統(tǒng)公司公布一個(gè)新版的尖端功能驗(yàn)證平臺(tái)與方法學(xué),擁有全套最新增強(qiáng)功能,與之前發(fā)布的版本相比,可將SoC驗(yàn)證效率提高一倍。 Incisive ?12.2提供了兩倍性能,全新Incisive調(diào)試分析器產(chǎn)品,全新低功耗建模,以及當(dāng)今復(fù)雜IP與SoC高效驗(yàn)證所需的數(shù)百種其他功能。

2013-01-27 10:44:38 1437

1437

全球電子設(shè)計(jì)創(chuàng)新領(lǐng)先企業(yè)Cadence設(shè)計(jì)系統(tǒng)公司(NASDAQ: CDNS),近日推出新版本Incisive Enterprise Simulator,該版本將復(fù)雜SoC的低功耗驗(yàn)證效率提高了30

2013-05-14 10:31:40 1832

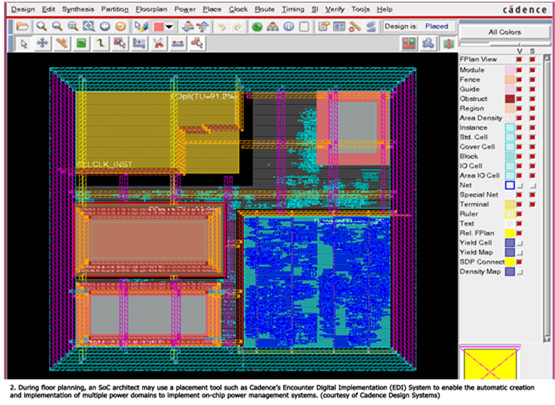

1832 楷登電子今日宣布,瑞昱半導(dǎo)體股份有限公司將 Cadence? Innovus? 設(shè)計(jì)實(shí)現(xiàn)系統(tǒng)用于其最新 28nm 數(shù)字電視(DTV)系統(tǒng)級(jí)芯片的研發(fā)并成功流片,同時(shí)成功縮小了芯片面積并降低了功耗

2018-05-07 13:11:28 4035

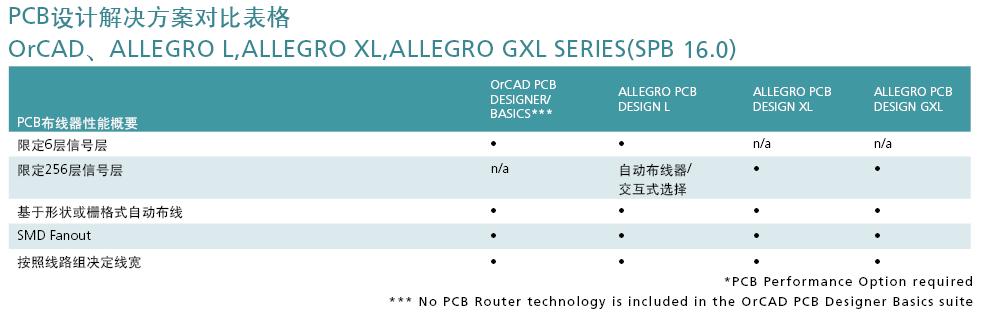

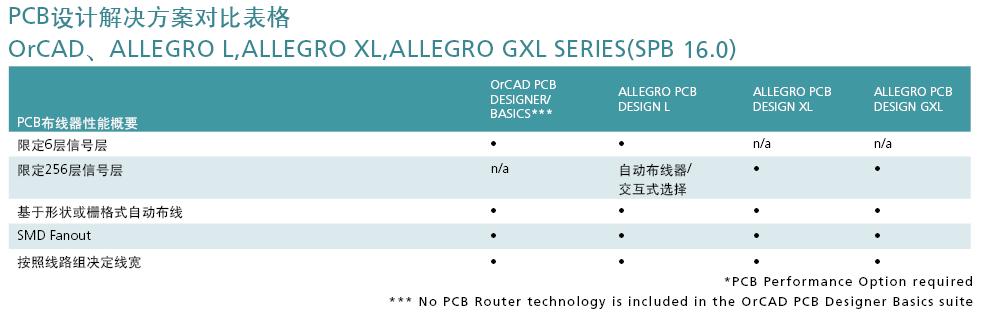

4035 CADENCE PCB設(shè)計(jì)解決方案能為解決與實(shí)現(xiàn)高難度的與制造密切相關(guān)的設(shè)計(jì)提供完整的設(shè)計(jì)環(huán)境,該設(shè)計(jì)解決方案集成了從設(shè)計(jì)構(gòu)想至最終產(chǎn)品所需要的一切設(shè)計(jì)流程,

2011-12-15 14:14:32 2074

2074 對(duì)5G毫米波系統(tǒng)的研發(fā),原型機(jī),驗(yàn)證,性能的測(cè)試解決方案;。系統(tǒng)的架構(gòu)高度模塊化,可支持不同的基帶調(diào)制解調(diào)器SoC(片上系統(tǒng))和調(diào)制解調(diào)器解決方案。另外設(shè)備所特有的對(duì)RF前端(Massive MIMO

2018-07-23 10:51:32

,以及至關(guān)重要的高速信號(hào),同時(shí),他們還要確保最終的PCB滿足傳統(tǒng)制造以及測(cè)試規(guī)格所能達(dá)到的性能目標(biāo)。 CADENCE PCB設(shè)計(jì)解決方案能為解決與實(shí)現(xiàn)高難度的與制造密切相關(guān)的設(shè)計(jì)提供完整的設(shè)計(jì)環(huán)境,該

2018-08-30 10:49:16

和靜態(tài)時(shí)序分析功能實(shí)現(xiàn)系統(tǒng)驅(qū)動(dòng)的功耗,性能和芯片面積(PPA,Power, Performance and Area)要求。Cadence 的第三代 三位3D-IC 解決方案支持廣泛的應(yīng)用領(lǐng)域,包括

2021-10-14 11:19:57

cadence公司于2012年9月25日發(fā)布了具有一系列新功能的Cadence® OrCAD® 16.6 PCB設(shè)計(jì)解決方案,用戶定制功能增強(qiáng),模擬性能提高20

2012-12-18 10:18:07

:“我們選擇Cadence作為我們RFSiP技術(shù)的合作伙伴,因?yàn)?b class="flag-6" style="color: red">Cadence有相應(yīng)的技術(shù)和能力,能夠和我們共同制定一套在FREESCALE能被廣泛采用的解決方案,從而顯著提升我們的RFSiP技術(shù)

2008-06-27 10:24:12

與FPGA架構(gòu)相集成,可以實(shí)現(xiàn)更大的設(shè)計(jì)靈活性和更快的上市時(shí)間。美高森美為電機(jī)控制算法開(kāi)發(fā)提供了具有多個(gè)多軸電機(jī)控制參考設(shè)計(jì)和IP的生態(tài)系統(tǒng),使由多處理器解決方案轉(zhuǎn)向單一器件解決方案(即SoC FPGA)更加容易。

2019-06-24 07:29:33

SoC芯片的規(guī)模一般遠(yuǎn)大于普通的ASIC,同時(shí)深亞微米工藝帶來(lái)的設(shè)計(jì)困難等使得SoC設(shè)計(jì)的復(fù)雜度大大提高。仿真與驗(yàn)證是SoC設(shè)計(jì)流程中最復(fù)雜、最耗時(shí)的環(huán)節(jié),約占整個(gè)芯片開(kāi)發(fā)周期的50%~80%,采用

2019-10-11 07:07:07

SoC內(nèi)ADC子系統(tǒng)集成驗(yàn)證挑戰(zhàn)

2021-04-02 06:03:24

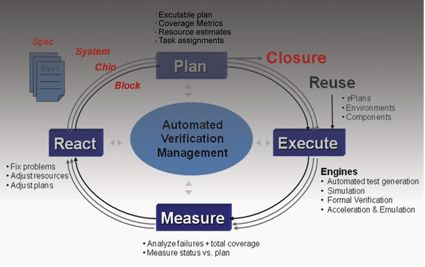

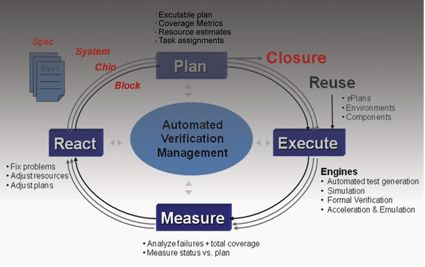

由于片上系統(tǒng)(SoC)設(shè)計(jì)變得越來(lái)越復(fù)雜,驗(yàn)證面臨著巨大的挑戰(zhàn)。大型團(tuán)隊(duì)不斷利用更多資源來(lái)尋求最高效的方法,從而將新的方法學(xué)與驗(yàn)證整合在一起,并最終將設(shè)計(jì)與驗(yàn)證整合在一起。雖然我們知道實(shí)現(xiàn)驗(yàn)證計(jì)劃

2019-07-11 07:35:58

客戶提供此系統(tǒng),從而成為首家部署老年人智能家居解決方案的大型健康保險(xiǎn)公司。憑借采用了全住宅傳感器系統(tǒng)的電子健康技術(shù),健康保險(xiǎn)公司和用戶能夠降低醫(yī)療保健成本,同時(shí)提高生活質(zhì)量。據(jù) Grand View

2020-11-02 08:43:58

解決方案。其中,EM1130內(nèi)部采用數(shù)字內(nèi)核實(shí)現(xiàn)控制環(huán)路,可以滿足極為嚴(yán)苛的瞬態(tài)要求,實(shí)現(xiàn)極低的紋波電壓(5mV峰峰值),以及在輸出電壓范圍(0.6V~1.5V)實(shí)現(xiàn)極高的精確穩(wěn)壓±0.5%。同時(shí)可以支持

2018-11-30 17:05:26

近年來(lái)變頻控制因其節(jié)能、靜音及低顫動(dòng)而得到廣泛的關(guān)注和應(yīng)用,基于ARM/DSP 的高性能驅(qū)動(dòng)方案為中大功率三相電機(jī)提供了高性能、多控制方式的解決方案,其主要應(yīng)用于對(duì)電機(jī)控制的性能、實(shí)時(shí)性方面要求比較

2019-07-09 08:24:02

SoC面臨的挑戰(zhàn)是什么采用FPGA方案進(jìn)行數(shù)字顯示系統(tǒng)設(shè)計(jì)有什么特性?

2021-04-29 06:24:26

隨著網(wǎng)絡(luò)和數(shù)據(jù)中心帶寬需求的日益提升,針對(duì)高性能內(nèi)存解決方案的需求也是水漲船高。對(duì)于超過(guò) 400 Gbps 的系統(tǒng)開(kāi)發(fā),以經(jīng)濟(jì)高效的方式實(shí)現(xiàn)內(nèi)存方案的性能和效率已經(jīng)成為項(xiàng)目中的重要挑戰(zhàn)之一。

2020-12-03 07:14:31

描述此設(shè)計(jì)采用 MSP430F6736 器件,實(shí)現(xiàn)了高度集成的單芯片電量計(jì)量(智能電表)解決方案。提供了硬件和軟件設(shè)計(jì)文件,以便計(jì)算單相電能計(jì)量的各種參數(shù),例如 RMS 電流和電壓、有功和無(wú)功功率

2018-08-23 14:22:38

`采用TI PurePath的音頻解決方案TI’s latest device in the family of PurePath? audio products is a wireless

2016-03-17 13:56:57

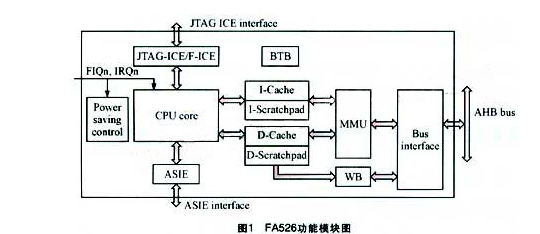

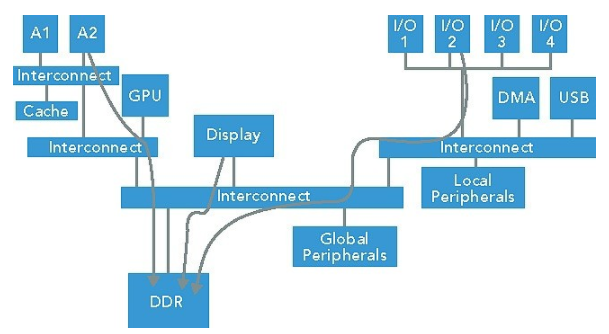

和ASIC中實(shí)現(xiàn)的硬核IP等。圖1即使如此,通用嵌入式系統(tǒng)也很難滿足現(xiàn)代設(shè)計(jì)需求。多芯片解決方案實(shí)現(xiàn)起來(lái)相對(duì)容易一些,但是成本高,缺乏設(shè)計(jì)人員所要求的靈活性以及性能/功耗指標(biāo)。采用了軟核處理器的單芯片

2021-07-14 08:00:00

產(chǎn)品落地。 方案簡(jiǎn)介 盈鵬飛智能數(shù)字班牌解決方案,采用高性能、高穩(wěn)定性的開(kāi)源行業(yè)主板,豐富的外部擴(kuò)展接口,適配市面上全尺寸的顯示屏/觸摸屏,增加產(chǎn)品的可能性,讓產(chǎn)品更靈活地適應(yīng)市場(chǎng)的需求變化。支持運(yùn)行

2018-06-13 18:39:23

。 Cadence數(shù)字和簽收部門(DSG)資深副總裁Anirudh Devgan表示:“使用Voltus-Fi定制型電源完整性解決方案,我們的客戶在Virtuoso環(huán)境下能實(shí)現(xiàn)從模擬IP模塊到嵌入式

2018-09-30 16:11:32

;至少經(jīng)歷過(guò)兩個(gè)以上完整地芯片開(kāi)發(fā)流程中的設(shè)計(jì)工作; 5、熟悉ARM體系架構(gòu),具備SOC設(shè)計(jì)實(shí)現(xiàn)經(jīng)驗(yàn)優(yōu)先 6、掌握數(shù)字電路結(jié)構(gòu)的功能和特性,有較強(qiáng)的理論分析和鉆研能力 7、有良好的團(tuán)隊(duì)精神,較強(qiáng)的溝通能力

2013-05-27 16:05:22

新慧物聯(lián)數(shù)字醫(yī)院整體解決方案通過(guò)應(yīng)用移動(dòng)計(jì)算、智能識(shí)別、數(shù)據(jù)融合、云計(jì)算、物聯(lián)網(wǎng)等先進(jìn)技術(shù)對(duì)醫(yī)院臨床業(yè)務(wù)和醫(yī)院管理兩個(gè)核心的應(yīng)用進(jìn)行數(shù)字化、交互式、智慧化管理,最終幫助醫(yī)院提升管理水平和病人

2019-09-16 06:38:09

傳感器性能如何支持狀態(tài)監(jiān)控解決方案?

2021-01-28 06:51:45

分享一款不錯(cuò)的高性能音頻解決方案

2021-06-08 06:18:44

分享一種高性能的FM內(nèi)置天線解決方案

2021-05-26 06:18:53

和ASIC中實(shí)現(xiàn)的硬核IP等。圖1即使如此,通用嵌入式系統(tǒng)也很難滿足現(xiàn)代設(shè)計(jì)需求。多芯片解決方案實(shí)現(xiàn)起來(lái)相對(duì)容易一些,但是成本高,缺乏設(shè)計(jì)人員所要求的靈活性以及性能/功耗指標(biāo)。采用了軟核處理器的單芯片

2021-07-12 08:00:00

如何實(shí)現(xiàn)高性能的射頻測(cè)試解決方案NI軟硬件的關(guān)鍵作用是什么

2021-05-06 07:24:55

兩個(gè)方面的性能,即電磁發(fā)射 / 干擾 EME 和電磁抗擾 EMS。EME 中包含傳導(dǎo)和輻射;而 EMS 中又包含靜電、脈沖群、浪涌等。為提升用戶系統(tǒng)穩(wěn)定性,接下來(lái)我們將為大家講述如何靈活應(yīng)用以上方法優(yōu)化電源 EMC,本文將從電源的設(shè)計(jì)與應(yīng)用等角度介紹 4 種常用解決方案:

2020-10-29 07:07:03

MentorGraphics委托的2012年功能驗(yàn)證調(diào)查,邏輯和數(shù)據(jù)路徑的門數(shù)在持續(xù)增加這些數(shù)字相當(dāng)值得深思,很顯然,僅在基于軟件的模擬器上驗(yàn)證設(shè)計(jì)時(shí),速度會(huì)慢下來(lái)。盡管包括Mentor在內(nèi)的大型EDA

2017-04-05 14:17:46

應(yīng)用之前,還需要消除功耗、性能以及成本阻礙。基站制造商傾向于重點(diǎn)關(guān)注小型蜂窩基帶片上系統(tǒng)(SoC)的性能特點(diǎn)。基帶SoC軟硬件確實(shí)能對(duì)小型蜂窩解決方案性能產(chǎn)生重大影響,但設(shè)計(jì)的數(shù)字無(wú)線電前端部分也同樣

2019-06-19 06:14:09

chip_agt 接管CPU出來(lái)的總線。總而言之做法就是通過(guò)UVM去接管系統(tǒng)的總線。這樣我們可以bypass boot的過(guò)程,并且還可以實(shí)現(xiàn)IP的驗(yàn)證環(huán)境在SOC驗(yàn)證環(huán)境中復(fù)用。如果我們對(duì)C代碼進(jìn)行一些封裝

2022-06-17 14:41:50

尋求AMD R系列與AMD SOC系列嵌入式高效能解決方案

2021-05-10 06:05:01

求一款Cadence的高級(jí)可制造性設(shè)計(jì)解決方案

2021-04-26 06:25:07

描述本汽車無(wú)線外反光鏡控制參考設(shè)計(jì)展示了一套面向汽車電動(dòng)側(cè)視鏡的概念驗(yàn)證解決方案,在這套解決方案中,電動(dòng)側(cè)視鏡可以無(wú)線方式與控制開(kāi)關(guān)通信。本參考設(shè)計(jì)棄用了厚重而昂貴的電纜束,轉(zhuǎn)而采用 TI 的汽車級(jí)

2018-11-19 11:46:02

SoC的20 V輸入解決方案該LTC7150S提出了用于工業(yè)和汽車電源,高性能的吧。它具有高效率,小外形和低EMI。集成的高性能MOSFET和熱管理功能可在高達(dá)20V的輸入電壓下實(shí)現(xiàn)高達(dá)20A的電流可靠

2019-03-09 11:46:55

。20用于SoC的20 V輸入解決方案該LTC7150S提出了用于工業(yè)和汽車電源,高性能的吧。它具有高效率,小外形和低EMI。集成的高性能MOSFET和熱管理功能可在高達(dá)20V的輸入電壓下實(shí)現(xiàn)高達(dá)20A

2018-09-13 14:28:48

的DDR3和LPDDR4,以及5V,3.3V和1.8V的外設(shè)和輔助組件。此外,先進(jìn)的SoC需要比傳統(tǒng)PWM控制器和MOSFET所能提供的更高的性能。因此,必要的解決方案必須更緊湊,具有更高的電流能力,更高

2018-12-26 09:17:59

:Arria 10 SoC 開(kāi)發(fā)套件板針對(duì)內(nèi)核、系統(tǒng)和 I/O 的電源管理謹(jǐn)慎地選擇高端 FPGA (包括 Arria 10) 的電源管理解決方案應(yīng)謹(jǐn)慎地選擇。經(jīng)過(guò)審慎考慮的電源管理設(shè)計(jì)可縮減 PCB

2018-10-29 17:01:56

。20用于SoC的20 V輸入解決方案該LTC7150S提出了用于工業(yè)和汽車電源,高性能的吧。它具有高效率,小外形和低EMI。集成的高性能MOSFET和熱管理功能可在高達(dá)20V的輸入電壓下實(shí)現(xiàn)高達(dá)20A

2018-09-25 09:34:50

ESL 設(shè)計(jì)和驗(yàn)證方法使設(shè)計(jì)工程師能夠?qū)W⒂谀切┙o產(chǎn)品及IP 帶來(lái)差異化和價(jià)值的系統(tǒng)設(shè)計(jì)屬性,即功能性和性能。本文討論電子系統(tǒng)級(jí)(ESL)設(shè)計(jì)和驗(yàn)證方法學(xué)在系統(tǒng)級(jí)芯片(SoC)設(shè)

2009-11-30 16:15:15 33

33 2009年3月4日,Cadence設(shè)計(jì)系統(tǒng)公司今天宣布生物指紋安全解決方案領(lǐng)先廠商UPEK®, Inc.已經(jīng)整合其設(shè)計(jì)流程,并選擇Cadence®作為其全芯片數(shù)字、模擬與混合信號(hào)設(shè)計(jì)的

2009-03-05 12:14:18 519

519 Cadence推出首個(gè)TLM驅(qū)動(dòng)式設(shè)計(jì)與驗(yàn)證解決方案

Cadence設(shè)計(jì)系統(tǒng)公司今天推出首個(gè)TLM驅(qū)動(dòng)式協(xié)同設(shè)計(jì)與驗(yàn)證解決方案和方法學(xué),使SoC設(shè)計(jì)師們可以盡享事務(wù)級(jí)建模(TLM)的好處。

2009-08-07 07:32:00 674

674 Cadence推出首個(gè)TLM驅(qū)動(dòng)式設(shè)計(jì)與驗(yàn)證解決方案提升基于RTL流程的開(kāi)發(fā)效率

Cadence設(shè)計(jì)系統(tǒng)公司推出首個(gè)TLM驅(qū)動(dòng)式協(xié)同設(shè)計(jì)與驗(yàn)證解決方案和方法學(xué),使SoC設(shè)計(jì)師們可以盡

2009-08-11 09:12:18 499

499 中芯國(guó)際采用Cadence DFM解決方案用于65和45納米 IP/庫(kù)開(kāi)發(fā)和全芯片生產(chǎn)

Cadence 模型化的 Litho Physical 和 Litho Electrical

2009-10-19 17:48:11 461

461 Cadence 模型化的 Litho Physical 和 Litho Electrical AnalyzerLitho Physical 與 Litho Electrical Analyzer 解決方案提供了快速、精確硅認(rèn)證的全芯片電氣 DFM 驗(yàn)證流程

2009-10-20 09:54:02 990

990 Cadence為PCI Express 3.0推出首款驗(yàn)證解決方案

Cadence設(shè)計(jì)系統(tǒng)公司宣布其已經(jīng)開(kāi)發(fā)了基于開(kāi)放驗(yàn)證方法學(xué)(OVM)的驗(yàn)證IP(VIP)幫助開(kāi)發(fā)者應(yīng)用最新的PCI Express Base Specification

2009-11-04 16:59:59 1142

1142 Magma推出面向大型SoC的增強(qiáng)版層次化設(shè)計(jì)規(guī)劃解決方案

微捷碼(Magma)日前發(fā)布了面向大型片上系統(tǒng)(SoC)的增強(qiáng)版層次化設(shè)計(jì)規(guī)劃解決方案Hydra 1.1。新版產(chǎn)品提供了通道

2009-12-09 08:31:53 888

888 TI推出最新多核SoC架構(gòu),實(shí)現(xiàn)5倍性能提升

日前,德州儀器(TI)宣布推出一款基于 TI 多核數(shù)字信號(hào)處理器(DSP)的新型片上系統(tǒng)(SoC)架構(gòu),該架構(gòu)在業(yè)界性能最高的CPU中同時(shí)

2010-02-26 08:38:16 562

562 芯邦采用Cadence Incisive Xtreme III系統(tǒng)提升SoC驗(yàn)證實(shí)效

全球電子設(shè)計(jì)創(chuàng)新領(lǐng)先企業(yè)Cadence設(shè)計(jì)系統(tǒng)公司今天宣布,位于中國(guó)深圳的、無(wú)晶圓廠集成電路設(shè)計(jì)領(lǐng)先企業(yè)芯邦科

2010-03-02 10:32:47 573

573 CADENCE PCB設(shè)計(jì)技術(shù)方案

CADENCE PCB設(shè)計(jì)解決方案能為解決與實(shí)現(xiàn)高難度的與制造密切相關(guān)的設(shè)計(jì)提供完整的設(shè)計(jì)環(huán)境,該設(shè)計(jì)解決方案集成了從設(shè)計(jì)構(gòu)

2010-04-29 08:53:19 3756

3756

全球電子設(shè)計(jì)創(chuàng)新領(lǐng)先企業(yè)Cadence設(shè)計(jì)系統(tǒng)公司,今天宣布了業(yè)界最全面的用于系統(tǒng)級(jí)芯片(SoC)驗(yàn)證的通用驗(yàn)證方法學(xué)(UVM)開(kāi)源參考流程。為了配合Cadence EDA360中SoC實(shí)現(xiàn)能力的策略,

2010-06-28 08:29:14 2240

2240 Cadence設(shè)計(jì)系統(tǒng)公司日前宣布已收購(gòu)Azuro公司,該公司是引領(lǐng)新一代系統(tǒng)級(jí)芯片優(yōu)化與數(shù)字實(shí)現(xiàn)轉(zhuǎn)型的先鋒企業(yè)。Azuro提供獨(dú)特的時(shí)鐘同步優(yōu)化技術(shù),又稱為ccopt技術(shù).

2011-07-22 09:15:25 575

575 Cadence 設(shè)計(jì)系統(tǒng)公司日前宣布,汽車零部件生產(chǎn)商Denso公司在改用了Cadence定制/模擬與數(shù)字流程之后,在低功耗混合信號(hào)IC設(shè)計(jì)方面實(shí)現(xiàn)了質(zhì)量與效率的大幅提升。將Cadence Encounter RTL-to-G

2012-09-04 09:31:59 811

811 電子發(fā)燒友網(wǎng)核心提示 :全球電子設(shè)計(jì)創(chuàng)新領(lǐng)先企業(yè)Cadence設(shè)計(jì)系統(tǒng)公司于日前發(fā)布了具有一系列新功能的Cadence OrCAD 16.6 PCB設(shè)計(jì)解決方案,用戶定制功能增強(qiáng),模擬性能提高20%, 使用戶

2012-10-16 08:44:25 1192

1192 全球電子設(shè)計(jì)創(chuàng)新領(lǐng)先企業(yè)Cadence設(shè)計(jì)系統(tǒng)公司日前宣布TSMC已選擇Cadence解決方案作為其20納米的設(shè)計(jì)架構(gòu)。Cadence解決方案包括Virtuoso定制/模擬以及Encounter RTL-to-Signoff平臺(tái)。

2012-10-22 16:48:03 909

909 電子設(shè)計(jì)創(chuàng)新企業(yè)Cadence設(shè)計(jì)系統(tǒng)公司,今天宣布使用ARM AMBA協(xié)議類型的Cadence驗(yàn)證IP(VIP)實(shí)現(xiàn)多個(gè)成功驗(yàn)證項(xiàng)目,這是業(yè)界最廣泛使用的AMBA協(xié)議系列驗(yàn)證解決方案之一。頂尖客戶,包括

2012-11-07 08:21:52 997

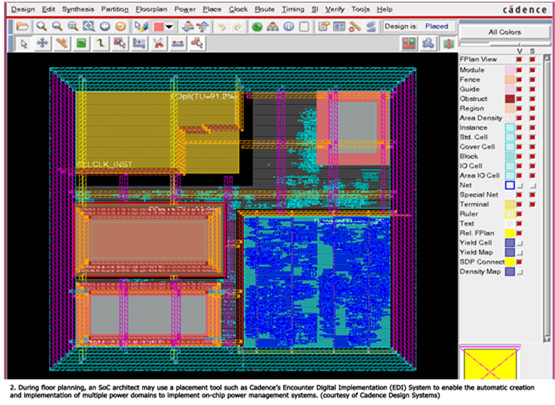

997 Cadence設(shè)計(jì)系統(tǒng)公司日前宣布Avago Technologies在大型28納米網(wǎng)絡(luò)芯片設(shè)計(jì)中使用其EDI系統(tǒng),大幅度加快設(shè)計(jì)進(jìn)度,提高了工程效率。Avago實(shí)現(xiàn)1GHz的性能,比之前所用軟件設(shè)計(jì)的芯片提高57%。

2013-02-04 09:17:00 1150

1150

光刻物理分析器成功完成20納米系統(tǒng)級(jí)芯片(SoC)測(cè)試芯片流片。雙方工程師通過(guò)緊密合作,運(yùn)用Cadence解決方案克服實(shí)施和可制造性設(shè)計(jì)(DFM)驗(yàn)證挑戰(zhàn),并最終完成設(shè)計(jì)。

2013-07-09 15:53:24 769

769 Workbench搭配Cadence Interconnect Validator,組成了一套完整的功能驗(yàn)證與性能檢驗(yàn)解決方案。

2013-11-07 09:34:14 1130

1130 )采用全新的Cadence? Voltus?集成電路電源完整性解決方案,在其旗艦產(chǎn)品上實(shí)現(xiàn)了運(yùn)行時(shí)間10倍的性能加速。

2013-11-14 16:45:29 1300

1300 全球電子設(shè)計(jì)創(chuàng)新領(lǐng)先企業(yè)Cadence設(shè)計(jì)系統(tǒng)公司(NASDAQ: CDNS)今天發(fā)布了新版 Incisive? 功能驗(yàn)證平臺(tái),再一次為整體驗(yàn)證性能和生產(chǎn)率設(shè)定新標(biāo)準(zhǔn)。

2014-01-16 17:36:13 1047

1047 全球電子設(shè)計(jì)創(chuàng)新領(lǐng)先企業(yè)Cadence設(shè)計(jì)系統(tǒng)公司(NASDAQ: CDNS)今天宣布,海思半導(dǎo)體(HiSilicon Semi)進(jìn)一步擴(kuò)大采用Cadence? Palladium? XP 驗(yàn)證運(yùn)算平臺(tái)作為其仿真方案,運(yùn)用于移動(dòng)和數(shù)字媒體System-on-Chip (SoC) 與 ASIC開(kāi)發(fā)。

2014-05-13 16:19:03 2137

2137 聯(lián)發(fā)科技宣布其高性能Wi-Fi SoC解決方案RT6856 已經(jīng)被全球無(wú)線網(wǎng)通領(lǐng)導(dǎo)品牌D-Link(友訊集團(tuán))所采用。D-Link繼而推出一系列內(nèi)置聯(lián)發(fā)科技Wi-Fi SoC解決方案的新一代無(wú)線云路由器,鞏固市場(chǎng)領(lǐng)先地位。

2014-06-25 16:03:00 1456

1456 全球知名電子設(shè)計(jì)創(chuàng)新領(lǐng)先公司Cadence設(shè)計(jì)系統(tǒng)公司 (NASDAQ: CDNS),今日宣布臺(tái)積電采用了Cadence?16納米FinFET單元庫(kù)特性分析解決方案。

2014-10-08 19:03:22 1594

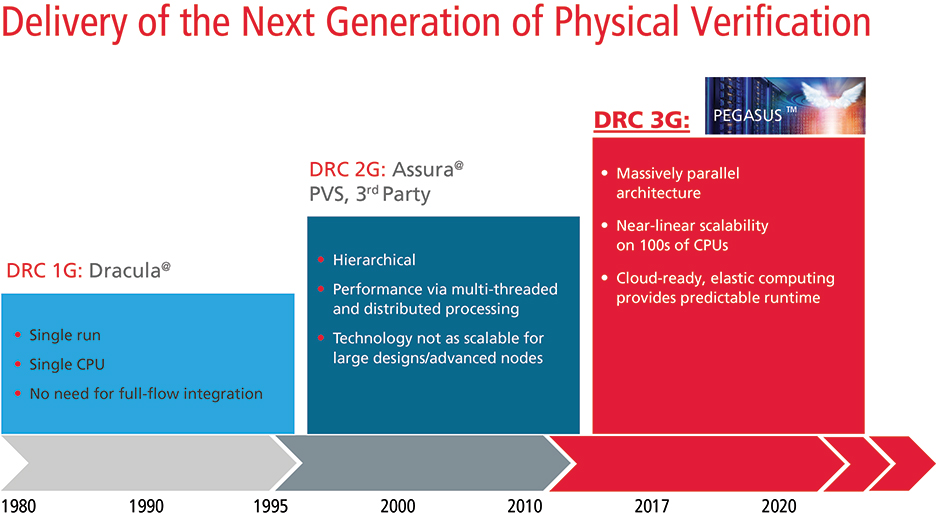

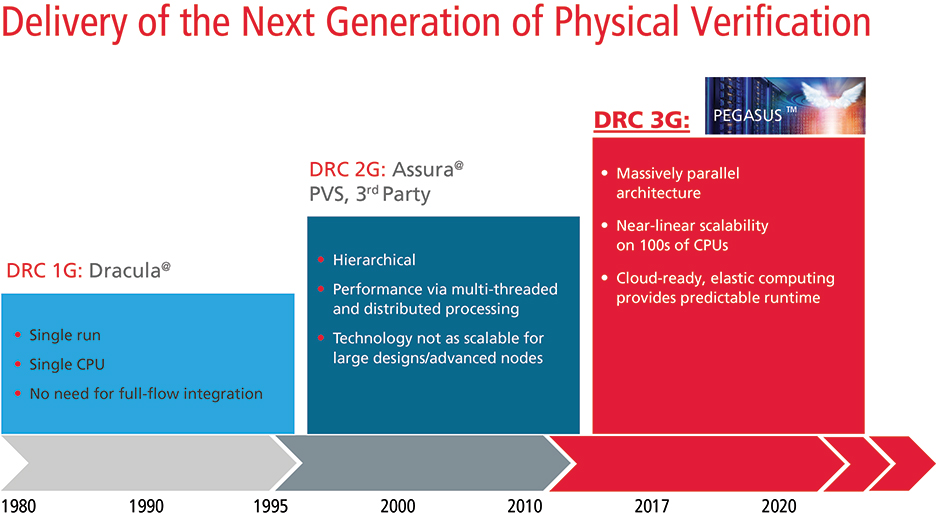

1594 將助工程師縮短先進(jìn)節(jié)點(diǎn)IC的上市時(shí)間。Pegasus?驗(yàn)證系統(tǒng)解決方案是全流程Cadence數(shù)字設(shè)計(jì)與簽核套件的新成員,可擴(kuò)展至數(shù)百CPU,設(shè)計(jì)規(guī)則檢查(DRC)性能最高可提升10倍,周轉(zhuǎn)時(shí)間較上一代Cadence? 解決方案由數(shù)日降至數(shù)小時(shí)。

2017-04-14 15:42:44 1294

1294

為了充分利用系統(tǒng)級(jí)芯片(SoC)設(shè)計(jì)帶來(lái)的優(yōu)點(diǎn),業(yè)界需要一種可以擴(kuò)展的驗(yàn)證解決方案,解決設(shè)計(jì)周期中各個(gè)階段的問(wèn)題,縮短驗(yàn)證鴻溝。本文將探討可擴(kuò)展驗(yàn)證解決方案為何能夠以及如何解決SoC設(shè)計(jì)目前面臨的功能方面的嚴(yán)峻挑戰(zhàn),以達(dá)到提高設(shè)計(jì)生產(chǎn)力、保證設(shè)計(jì)質(zhì)量、縮短產(chǎn)品上市時(shí)間以及提高投資回報(bào)率的目的。

2018-06-04 03:13:00 743

743

采用極紫外(EUV)光刻技術(shù)的Cadence 數(shù)字全流程解決方案已通過(guò)Samsung Foundry 5nm早期低功耗版(5LPE)工藝認(rèn)證。

2019-07-11 16:36:47 3436

3436 晶圓代工大廠聯(lián)電與臺(tái)灣地區(qū)知識(shí)產(chǎn)權(quán)大廠智原科技于18日宣布,推出基于聯(lián)電22納米超低功耗(ULP)與22納米超低漏電(ULL)制程的基礎(chǔ)元件IP解決方案。該22ULP/ULL基礎(chǔ)元件IP已成功通過(guò)

2019-11-19 16:08:11 3285

3285 NI 芯片功耗和性能驗(yàn)證解決方案具有高準(zhǔn)確度和高通道數(shù),有助于加快產(chǎn)品上市時(shí)間,您可以使用專用儀器和基于配置的軟件來(lái)快速設(shè)置、測(cè)量、記錄和可視化功耗測(cè)量數(shù)據(jù)。

2021-01-18 16:48:37 1784

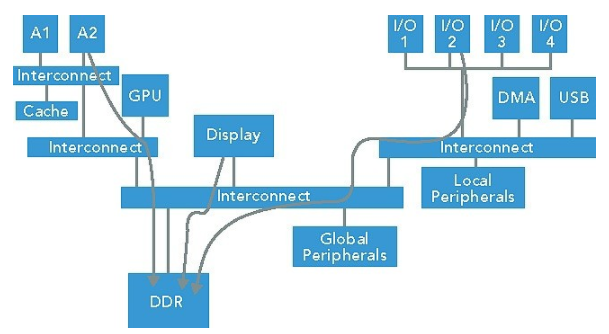

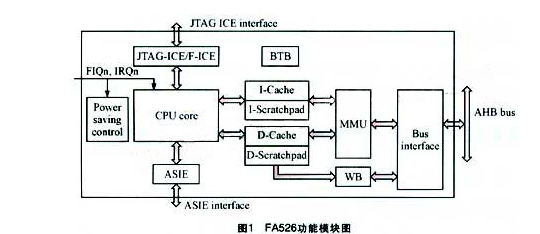

1784 智原科技的FIE8100 SoC平臺(tái)是一種低功耗、便攜式視頻相關(guān)應(yīng)用開(kāi)發(fā)SoC平臺(tái),也可用于基于FA526 CPU的SoC設(shè)計(jì)驗(yàn)證。基于

2021-03-24 14:39:39 2110

2110

Cadence擁有最完整的IP與SoC驗(yàn)證、硬件與軟件回歸測(cè)試及早期軟件開(kāi)發(fā)的全系列解決方案。

2021-04-06 13:48:53 2431

2431 沿的技術(shù)應(yīng)用到 TSMC 先進(jìn) FinFET 工藝上,為市場(chǎng)帶來(lái)一款極具競(jìng)爭(zhēng)力的低功耗解決方案,并采用業(yè)界最新的測(cè)試方案進(jìn)行測(cè)試。 這一 PCIe 系統(tǒng)解決方案由 Cadence PCIe 5.0

2021-05-14 10:33:55 1787

1787 Cadence Safety Solution 包括新的 Midas Safety Platform,為模擬和數(shù)字流程提供基于 FMEDA 功能安全設(shè)計(jì)和驗(yàn)證的統(tǒng)一方案 該安全流程方案為汽車、工業(yè)

2021-10-26 14:24:34 4050

4050 Liberate Characterization 和 Tempus 解決方案已經(jīng)通過(guò) Samsung Foundry 老化模型驗(yàn)證,使客戶能夠快速、安心地完成高可靠性的設(shè)計(jì)簽核 Tempus 解決方案的全新

2021-11-19 11:00:13 2967

2967 GlobalFoundries 在 AWS 上完成了對(duì) Cadence 數(shù)字解決方案的認(rèn)證,可用于其專有的差異化 22FDX 平臺(tái)。

2022-03-28 11:17:46 1812

1812 ASIC設(shè)計(jì)服務(wù)暨IP研發(fā)銷售廠商智原科技(Faraday Technology Corporation,TWSE:3035)今日發(fā)表Soteria!安全子系統(tǒng)。該解決方案針對(duì)SoC設(shè)計(jì)提供可靠的硬件信任根(Root of Trust,RoT),從芯片物理層來(lái)確保物聯(lián)網(wǎng)應(yīng)用產(chǎn)品的信息安全。

2022-06-01 15:47:25 1138

1138 楷登電子(美國(guó) Cadence 公司,NASDAQ:CDNS)今日宣布推出 15 種新的驗(yàn)證 IP(VIP)解決方案,助力工程師迅速有效地驗(yàn)證設(shè)計(jì),以滿足最新標(biāo)準(zhǔn)協(xié)議的要求。

2022-06-06 11:18:21 2665

2665 楷登電子(美國(guó) Cadence 公司,NASDAQ:CDNS)今日宣布,競(jìng)逐第 37 屆美洲杯帆船賽的三支參賽隊(duì)伍將借助 Cadence? 計(jì)算流體力學(xué)(CFD)解決方案,提升其賽船的性能及整體表現(xiàn)力。

2022-06-07 11:30:01 1153

1153 面對(duì)持續(xù)不斷的上市時(shí)間壓力和日益復(fù)雜的 SoC 設(shè)計(jì),很難找到不想從設(shè)計(jì)周期中縮短時(shí)間的工程師。特別是在高級(jí)節(jié)點(diǎn),驗(yàn)證 SoC 互連已成為一個(gè)耗時(shí)的步驟。但是,工具現(xiàn)在可以高效且有效地執(zhí)行周期精確的性能分析和互連驗(yàn)證。

2022-06-14 10:12:17 1692

1692

的驗(yàn)證 IP(VIP)和系統(tǒng)級(jí) VIP(系統(tǒng) VIP),以加速新技術(shù)的采用。Cadence CXL 3.0 VIP與 Cadence PCI Express(PCIe)6.0 VIP 集成,提供了從 IP 到系統(tǒng)級(jí)芯片(SoC)的完整解決方案,助力用戶成功設(shè)計(jì)高性能數(shù)據(jù)中心應(yīng)用。

2022-08-10 10:14:50 1781

1781 這一解決方案可實(shí)現(xiàn)對(duì)千億門超大規(guī)模集成電路的仿真驗(yàn)證,更具備比傳統(tǒng)仿真器速度更高的性能,能夠3小時(shí)完成原本需要7天的仿真驗(yàn)證任務(wù)。

2022-09-26 09:25:25 539

539 Cadence 射頻集成電路解決方案支持 Cadence 智能系統(tǒng)設(shè)計(jì)(Intelligent System Design)戰(zhàn)略,助力實(shí)現(xiàn)系統(tǒng)級(jí)芯片(SoC)的卓越設(shè)計(jì)。

2022-11-03 14:18:50 835

835 楷登電子(美國(guó) Cadence 公司,NASDAQ:CDNS)今日宣布,創(chuàng)意電子(GUC)借助 Cadence 數(shù)字解決方案成功完成先進(jìn)的高性能計(jì)算 (HPC)設(shè)計(jì)和 CPU 設(shè)計(jì)。其中,HPC

2023-02-06 15:02:48 1048

1048 思爾芯(S2C)近日宣布,公司的系統(tǒng)級(jí)驗(yàn)證原型驗(yàn)證解決方案獲得了較為全面的正向市場(chǎng)反饋,成功協(xié)助多家設(shè)計(jì)企業(yè)完成低功耗藍(lán)牙音頻(BLE Audio)領(lǐng)域的IP/藍(lán)牙SoC定制方案設(shè)計(jì)。

2023-05-30 15:52:52 402

402 了 Cadence 在面對(duì) SoC 設(shè)計(jì)驗(yàn)證挑戰(zhàn)下的應(yīng)對(duì)之法。 隨著 SoC 設(shè)計(jì)的發(fā)展,如何在有限的時(shí)間內(nèi)盡可能發(fā)現(xiàn)更多的 bug 和實(shí)現(xiàn)更多的溯源分析,讓項(xiàng)目各方面的投資都做到物盡其用,這是驗(yàn)證工作所面臨

2023-06-07 00:20:03 466

466

和混合信號(hào) IP,與現(xiàn)有流程相比,在達(dá)到所需精度的同時(shí),可幫助提升 2 倍性能。 Cadence 的這款解決方案助力 DB GlobalChip 加速了 IP 開(kāi)發(fā)和驗(yàn)證周期,可以更快將產(chǎn)品推向市場(chǎng)。 在客戶規(guī)定的時(shí)間內(nèi)滿足模擬和混

2023-06-25 12:25:02 512

512 移動(dòng)電話技術(shù)的進(jìn)步不斷挑戰(zhàn)極限,要求SoC在提供不斷提升的性能的同時(shí),還能保持較長(zhǎng)的電池續(xù)航時(shí)間。為了滿足這些需求,業(yè)界正在逐步采用更低的技術(shù)節(jié)點(diǎn),目前的設(shè)計(jì)都是在5納米或更低的工藝下完成的。在這

2023-07-17 10:12:18 433

433

雙方的共同客戶可獲取 Cadence 的全流程系統(tǒng)級(jí)設(shè)計(jì)驗(yàn)證和實(shí)現(xiàn)解決方案以及接口 IP,依托 Neoverse CSS 加速開(kāi)發(fā)基于 Arm 的定制 SoC 中國(guó)上海,2023 年 10 月 25

2023-10-25 10:40:02 197

197

內(nèi)容提要 ● Broadcom 多個(gè)業(yè)務(wù)部門采用了 AI 驅(qū)動(dòng)的 Cadence Cerebrus 解決方案,用于在先進(jìn)節(jié)點(diǎn)上設(shè)計(jì)多款復(fù)雜的尖端產(chǎn)品 ● Broadcom 的產(chǎn)品設(shè)計(jì)在性能、功率和面

2023-10-26 15:35:01 175

175 設(shè)計(jì)簽核,并取得了更好的 PPA 結(jié)果 2 首次部署 Cadence 簽核解決方案后,Samsung Foundry 實(shí)現(xiàn)了兩倍的生產(chǎn)力提升,加速了設(shè)計(jì)收斂 中國(guó)上海,2023 年 12

2023-12-04 10:15:01 243

243

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論