隨著通信技術的迅猛發展,電信號越來越復雜化和瞬態化,開發人員對測量領域必不可少的工具——數字示波器的性能提出了越來越高的要求。最大限度提高實時采樣率和波形捕獲能力成為了國內外眾多數字示波器生產廠商研究的重點,實時采樣率和波形捕獲率的提高又必然帶來大量高速波形數據的傳輸、保存和處理的問題。因此,作為數字示波器數據處理和系統控制的中樞,微處理器性能至關重要。本文選用TI公司的雙核 DSP OMAP-L138作為本設計的微處理器,并實現了一種數字示波器微處理器硬件設計。

數字示波器的基本架構

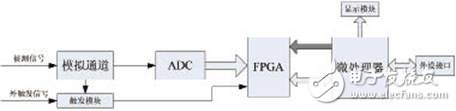

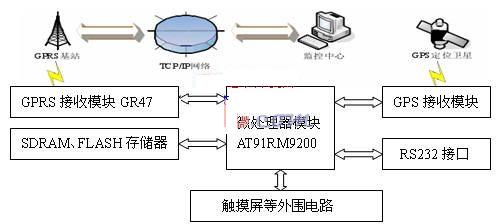

目前數字示波器多采用DSP、內嵌微處理器型FPGA或微處理器+FPGA架構。雖然內嵌微處理器型FPGA靈活性強,可以充分進行設計開發和驗證,便于系統升級且FPGA外圍電路簡單。但是該類型FPGA屬于高端FPGA,價高且供貨渠道難得,不適合低成本的數字示波器使用。若單獨使用 DSP,雖然其數據處理能力強大,運行速度較高,但DSP的控制能力不突出,且數字示波器的采樣率越來越高,DSP內部不能做數據流降速和緩存,當設計采用高實時采樣率的 ADC,就得選用頻率更高且內部存儲資源更豐富的DSP,而此類DSP一般都價格昂貴,同樣不適合低成本的數字示波器使用。因此,微處理器+FPGA架構的方案是本設計首選。微處理器+FPGA架構的數字示波器的系統結構圖如圖1所示:

圖1 微處理器+FPGA架構的數字示波器系統結構圖

被測信號經模擬通道運放調理后送到ADC器件;ADC轉換器將輸入端的信號轉換成相應的數字信號并經過FPGA緩存和預處理;微處理器對采樣得到的數字信號進行相關處理與運算;最后將波形送到屏幕上顯示,完成一次采集過程。同時采集過程中觸發電路不斷監測輸入信號,看是否出現觸發狀態,觸發條件決定了波形的起始位置,觸發系統能夠保證被測波形能夠穩定的顯示到屏幕上。

微處理器選型

本設計實時采樣率高達2Gsps,需要微處理器實時處理的波形數據量很大。同時微處理器要實現模擬通道控制、高速ADC采樣控制、波形數據存儲控制、LCD顯示控制等。因此兼具強大的數據處理能力和優異控制能力的微處理器成為本設計首選。

基于這些要求,本設計選擇了TI公司的OMAP- L138 DSP。此芯片是TI公司2009年推出的一款高性能處理器芯片。該芯片特點如下:

1、采用C6748 DSP內核與ARM9內核的雙核結構,可實現高達300 MHz的單位內核頻率。利用片上ARM9,開發人員可充分利用DSP內核支持高強度的實時處理計算,同時讓ARM負責非實時任務。

2、豐富的內部存儲器資源。其中ARM核內部有16KB的L1程序Cache和16KB的數據Cache;DSP核采用二級緩存結構,包括 32KB 的L1程序Cache、32KB 的數據Cache和256KB 的L2統一映射SRAM,該二級高速緩存結構可以為所有載入、存儲以及處理請求提供服務,可以為CPU提供高效、高速的數據共享;此外在ARM核與DSP 核之間還有高達128KB的片上RAM,可被ARM核、DSP核以及片外存儲器訪問。

3、豐富的外設資源。主要包括1個EMIFA口,可接16bit SDRAM或者NOR/NAND Flash;1個EMIFB口,可接16bit的DDR2(最高頻率150MHz)或16bit mDDR (最高頻率133MHz);3個UART接口;2個SPI接口;2個I2C接口;1個EMAC控制器;1個USB2.0接口和1個USB1.1接口;1個 LCD控制器;1個SATA控制器;1個uPP接口;1個VPIF接口;4個64位通用定時器。豐富的外設資源不僅可以為示波器提供與PC機、便攜式 USB接口設備通信的接口,而且極大減少DSP外圍電路的設計規模,

4、低功耗。采用1.2V內核電壓,1.8V或3.3V I/O接口電壓,在深度睡眠模式下功耗僅有6mW,正常工作模式下功耗約為420mW。

此外OMAP-L138為浮、定點兼容DSP,使用硬件來完成浮點運算,可以在單周期內完成,這一優點在實現高精度復雜算法時尤為突出,為復雜算法的實時處理提供了保證。OMAP-L138還可與C6748 DSP實現引腳對引腳兼容,從而使客戶可采用不同的處理器同時開發多種不同特性的產品。

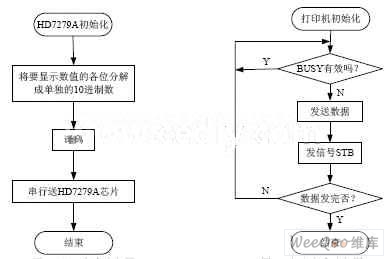

數字示波器系統硬件結構設計

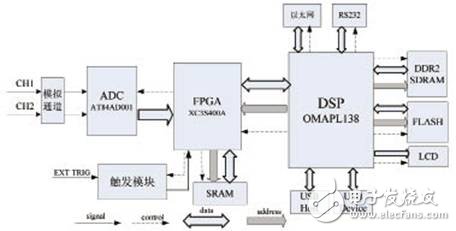

本設計ADC選用Atmel公司的AT84AD001,該芯片有兩個通道,每個通道采樣率高達1Gsps,拼合可實現2Gsps的實時采樣率;FPGA選用 Xilinx公司Spartan-3A系列的XC3S400A芯片,該芯片內有8064個邏輯單元,360Kbit塊RAM,56Kbit分布式 RAM,4個數字時鐘管理模塊(DCM),311個I/O口。300KB容量的SRAM芯片外掛在FPGA上作深存儲用,由于SRAM存儲器容量比 FPGA內部緩存FIFO大得多,能夠存儲更多的波形數據,因而能觀察到更多的波形細節。采用64Mbit容量的SPI Flash存儲示波器掉電需要保存的數據,例如程序代碼、Boot loader程序、中英文字庫、開機畫面等。

基于OMAP-L138的示波器硬件系統結構圖如圖2所示:

圖2 數字示波器系統結構圖

本設計中,被測信號進入模擬通道調理后送入ADC,ADC對模擬信號采樣、量化后,進入FPGA數據流降速和數據同步處理,然后根據存儲深度要求選擇存入 FPGA內部FIFO或者存入片外SRAM,待FPGA內部FIFO或者片外SRAM滿標志有效后,DSP讀取采樣數據存入DDR2 SDRAM,并完成一系列復雜的處理和運算,如FFT、插值和濾波等,再存入在DDR2內拓展的顯示存儲區,待需要顯示時再由DSP讀取顯存中的數據通過內部集成的LCD控制器采用DMA方式將數據送到LCD顯示,完成一次采集過程。

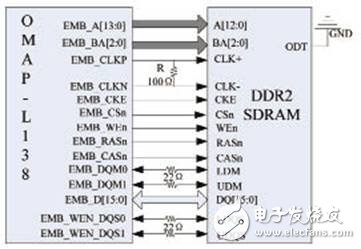

OMAP-L138與DDR2的接口電路設計

OMAP- L138內部集成的DDR2/Mobile DDR控制器可外接工作頻率150MHz的DDR2 SDRAM或者工作頻率133MHz的Mobile DDR。本設計采用DDR2 SDRAM作為系統后級波形數據緩存器。較之SDRAM,DDR2 SDRAM不僅讀寫速度可大幅提高,存儲容量更是得到極大擴展,示波器因而能夠存儲更多波形數據并觀察到更多的波形細節,提高示波器對復雜信號和瞬態信號的捕獲概率。本設計的DDR2 SDRAM選用鎂光公司的DDR2 800內存顆粒,型號為MT47H64M16,容量為1Gbit,核心工作電壓為1.8V,核心工作頻率為400MHz,由于OMAP-L138內部的 DDR2控制器最高工作頻率為150MHz,所以此系統中DDR2需要降頻使用。OMAP-L138與DDR2的接口連接示意圖如圖3所示:

圖3 OMAP-L38與DDR2的接口連接示意圖

DDR2 的信號線包括時鐘、數據和命令三部分。本設計由DDR2控制器提供差分時鐘CLK+和CLK-給DDR2,,差分時鐘之間并接一個100Ω的匹配電阻,用以消除時鐘的毛刺并限制驅動電流;數據部分主要完成數據傳輸工作,包括數據線DQ[15:0]、數據同步信號DQS(本設計LDQS對應數據線低八位,UDQS對應數據線高八位)、數據信號屏蔽線DM(在突發寫傳輸時屏蔽不存儲的數據,LDM對應數據位低八位DQ[7:0],UDM對應數據線高八位 DQ[15:8]),本設計在DQS信號和DM信號上串接一個22Ω的電阻,起抗干擾和濾波作用,提高信號質量;命令部分包括行地址選通信號RASn、列地址選通信號CASn、寫使能信號WEn、片選信號CSn、時鐘使能信號CKE以及芯片內部終端電阻使能ODT,主要完成尋址、組成各種控制命令以及內存初始化工作。本設計由于DDR2控制器內沒有終端電阻,因此將DDR2 SDRAM的ODT信號直接接地使DDR2芯片內的終端電阻無效。

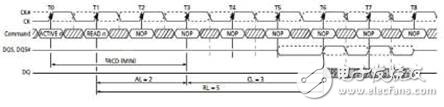

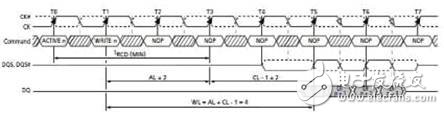

DDR2的讀、寫時序圖分別見圖4和圖5:

圖4 DDR2的讀數據時序圖

圖5 DDR2的寫數據時序圖

以太網的接口電路設計

用示波器測量電信號時,信息和測量結果便捷的保存和共享變得日益重要。若數字示波器提供以太網接口,開發人員就可以方便地將測量數據和結果通過網絡共享,實現遠程調試;也可以將波形數據通過網絡上傳到PC機上,在PC機上實現波形數據的處理、分析和顯示。

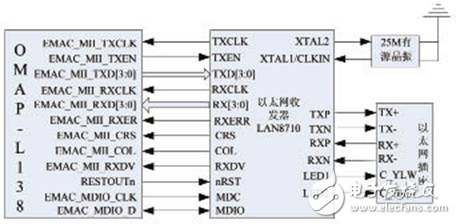

OMAP-L138內部集成的以太網控制器(EMAC)支持IEEE802.3標準,支持10Base-T和100Base-T兩種以太網標準,有全雙工和半雙工兩種工作模式可供選擇,提供了MII和RMII兩種以太網接口。

選用LAN8710以太網收發器,該以太網收發器提供MII和RMII兩種以太網接口。本設計采用MII接口實現LAN8710與EMAC的互聯。MII接口包括一個數據接口,一個MAC和PHY之間的管理接口。數據接口包括分別用于發送器和接收器的兩條獨立信道。每條信道有4根數據線、時鐘和控制信號,其中管理接口是雙信號接口:一個是時鐘信號,另一個是數據信號。通過管理接口,上層能監視和控制PHY。管理接口的時鐘MDC由EMAC提供,最高可達 8.3MHz;數據信號MDIO是雙向接口,與MDC同步,控制收發器并從收發器收集狀態信息。可收集的信息包括鏈接狀態、傳輸速度與選擇、斷電、低功率休眠狀態、TX/RX模式選擇、自動協商控制、環回模式控制等。

以太網接口連接示意圖如圖6所示:

圖6 以太網接口連接示意圖

結論

本設計有以下優點:數據處理與系統控制同步執行;微處理器內部存儲資源豐富,且采用二級緩存結構,系統響應速度快;外設資源豐富,提供了如 USB接口、RS232接口和以太網接口等與PC機互聯的接口,方便示波器上采集到的波形數據在PC機上實時處理和在線調試;外部存儲器資源豐富,采用 1Gbit 容量的DDR2 SDRAM作后級波形數據緩存區和顯示數據緩存區,能夠存儲更多波形數據,觀察到更多波形細節。由此可見,采用該示波器系統可大幅提高數字示波器的數據處理能力和波形捕獲率,整機的響應速度也將上一個臺階。

電子發燒友App

電子發燒友App

評論