這里概述的都是一些傳統意義上ARM處理器的一些方面,提醒自己看了之后會想起相關知識,或是對ARM有一個總體上的概念,其實都是些簡述性的總結,很多都來自網上資料或教學課件,貼在這里,方便以后隨時隨地的復習!

ARM微處理器包括ARM7、ARM9、ARM9E、ARM10E、SecurCore、以及Intel的StrongARM、XScale和其它廠商基于ARM體系結構的處理器,除了具有ARM體系結構的共同特點以外,每一個系列的ARM微處理器都有各自的特點和應用領域。

一、總的來說ARM處理器的一些特點:

1、采用RISC架構的ARM微處理器一般具有如下特點:

支持Thumb(16位)/ARM(32位)雙指令集,能很好的兼容8位/16位器件。Thumb指令集比通常的8位和16位CISC/RISC處理器具有更好的代碼密度;

●????????指令執行采用3級流水線/5級流水線技術;

●????????帶有指令Cache和數據Cache,大量使用寄存器,指令執行速度更快。大多數數據操作都在寄存器中完成。尋址方式靈活簡單,執行效率高。指令長度固定(在ARM狀態下是32位,在Thumb狀態下是16位);

●????????支持大端格式和小端格式兩種方法存儲字數據;

●????????支持Byte(字節,8位)、Halfword(半字,16位)和Word(字,32位)三種數據類型。

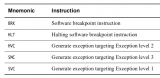

●????????支持用戶、快中斷、中斷、管理、中止、系統和未定義等7種處理器模式,除了用戶模式外,其余的均為特權模式;

●????????處理器芯片上都嵌入了在線仿真ICE-RT邏輯,便于通過JTAG來仿真調試ARM體系結構芯片,可以避免使用昂貴的在線仿真器。另外,在處理器核中還可以嵌入跟蹤宏單元ETM,用于監控內部總線,實時跟蹤指令和數據的執行;

●????????具有片上總線AMBA(Advanced Micro-controller Bus Architecture)。?AMBA定義了3組總線:先進高性能總線AHB(Advanced High performance Bus);先進系統總線ASB(Advanced System Bus);先進外圍總線APB(Advanced Peripheral Bus)。通過AMBA可以方便地擴充各種處理器及I/O,可以把DSP、其他處理器和I/O(如UART、定時器和接口等)都集成在一塊芯片中;

●????????采用存儲器映像I/O的方式,即把I/O端口地址作為特殊的存儲器地址;

●????????具有協處理器接口。ARM允許接16個協處理器,如CP15用于系統控制,CP14用于調試控制器;

●????????采用了降低電源電壓,可工作在3.0V以下;減少門的翻轉次數,當某個功能電路不需要時禁止門翻轉;減少門的數目,即降低芯片的集成度;降低時鐘頻率等一些措施降低功耗;

●????????體積小、低成本、高性能。

2、一個典型的ARM體系結構:

包含有32位ALU、31個32位通用寄存器及6位狀態寄存器、32×8位乘法器、32×32位桶形移位寄存器、指令譯碼及控制邏輯、指令流水線和數據/地址寄存器等。

1).ALU

ARM體系結構的ALU與常用的ALU邏輯結構基本相同,由兩個操作數鎖存器、加法器、邏輯功能、結果及零檢測邏輯構成。ALU的最小數據通路周期包含寄存器讀時間、移位器延遲、ALU延遲、寄存器寫建立時間、雙相時鐘間非重疊時間等幾部分。

2).桶形移位寄存器

ARM采用了32×32位桶形移位寄存器,左移/右移n位、環移n位和算術右移n位等都可以一次完成,可以有效的減少移位的延遲時間。在桶形移位寄存器中,所有的輸入端通過交叉開關(Crossbar)與所有的輸出端相連。交叉開關采用NMOS晶體管來實現。

3).高速乘法器

ARM為了提高運算速度,采用兩位乘法的方法,2位乘法可根據乘數的2位來實現“加-移位”運算。ARM的高速乘法器采用32×8位的結構,完成32×2位乘法也只需5個時鐘周期。

4).浮點部件

在ARM體系結構中,浮點部件作為選件可根據需要選用,FPA10浮點加速器以協處理器方式與ARM相連,并通過協處理器指令的解釋來執行。

浮點的Load/Store指令使用頻度要達到67%,故FPA10內部也采用Load/Store結構,有8個80位浮點寄存器組,指令執行也采用流水線結構。

5).控制器

ARM的控制器采用硬接線的可編程邏輯陣列PLA,其輸入端有14根、輸出端有40根,分散控制Load/Store多路、乘法器、協處理器以及地址、寄存器ALU和移位器。

6).寄存器

ARM內含37個寄存器,包括31個通用32位寄存器和6個狀態寄存器。

3、ARM7系列微處理器:

包括ARM7TDMI、ARM7TDMI-S、ARM720T、ARM7EJ幾種類型。其中,ARM7TDMI是目前使用最廣泛的32位嵌入式RISC處理器,主頻最高可達130MIPS,采用能夠提供0.9MIPS/MHz的三級流水線結構,內嵌硬件乘法器(Multiplier),支持16為壓縮指令集Thumb,嵌入式ICE,支持片上Debug,支持片上斷點和調試點。指令系統與ARM9系列、ARM9E系列和ARM10E系列兼容,支持Windows CE、Linux、Palm OS等操作系統。典型產品如Samsung公司的S< xmlnamespace prefix ="st1" ns ="urn:schemas-microsoft-com:office:smarttags" />3C4510B。

ARM7TDMI處理器內核:

n???????ARM7TDMI還提供了存儲器接口、MMU接口、協處理器接口和調試接口,以及時鐘與總線等控制信號,如圖2.2.2所示。

n???????存儲器接口包括了32位地址A[31:0]、雙向32位數據總線D[31:0]、單向32位數據總線DIN[31:0]與DOUT[31:0]、以及存儲器訪問請求MREQ、地址順序SEQ、存儲器訪問控制MAS[1:0和數據鎖存控制BL[3:0]等控制信號。

n???????ARM7TDMI處理器內核也可以ARM7TDMI-S軟核(Softcore)形式向用戶提供。同時,提供多種組合選擇,例如可以省去嵌入式ICE單元等。

n???????2.ARM720T/ARM740T處理器內核

n???????ARM720T處理器內核是在ARM7TDMI處理器內核基礎上,增加8KB的數據與指令Cache,支持段式和頁式存儲的MMU(Memory Management Unit)、寫緩沖器及AMBA(Advanced Microcontroller Bus Architecture)接口而構成,如圖2.2.3所示。

n???????ARM740T處理器內核與ARM720T處理器內核相比,結構基本相同,ARM740T處理器核沒有存儲器管理單元MMU,不支持虛擬存儲器尋址,而是用存儲器保護單元來提供基本保護和Cache的控制。合適低價格低功耗的嵌入式應用。

4、ARM9微處理器

ARM9系列微處理器包含ARM920T、ARM922T和ARM940T幾種類型,可以在高性能和低功耗特性方面提供最佳的性能。采用5級整數流水線,指令執行效率更高。提供1.1MIPS/MHz的哈佛結構。支持數據Cache和指令Cache,具有更高的指令和數據處理能力。?支持32位ARM指令集和16位Thumb指令集。支持32位的高速AMBA總線接口。全性能的MMU,支持Windows CE、Linux、Palm OS等多種主流嵌入式操作系統。MPU支持實時操作系統。

ARM920T處理器核在ARM9TDMI處理器內核基礎上,增加了分離式的指令Cache和數據Cache,并帶有相應的存儲器管理單元I-MMU和D-MMU、寫緩沖器及AMBA接口等。

ARM9系列微處理器主要應用于無線通信設備、儀器儀表、安全系統、機頂盒、高端打印機、數字照相機和數字攝像機等。典型產品如Samsung公司的S3C2410A。

二、ARM體系結構的五個方面:

ARM的體系結構或處理器結構主要體現在:ARM微處理器的寄存器結構、異常處理、存儲器結構、指令系統、接口等方面。

1、寄存器結構:

ARM處理器共有37個寄存器,被分為若干個組(BANK),這些寄器包括:

●??31個通用寄存器,包括程序計數器(PC指針),均為32位的寄存器。

●??6個狀態寄存器,用以標識CPU的工作狀態及程序的運行狀態,均為32位,目前只使用了其中的一部分。

(1)處理器運行模式:

ARM微處理器支持7種運行模式,分別為:

●??usr(用戶模式):ARM處理器正常程序執行模式。

●??fiq(快速中斷模式):用于高速數據傳輸或通道處理

●??irq(外部中斷模式):用于通用的中斷處理

●??svc(管理模式):操作系統使用的保護模式

●????????abt (數據訪問終止模式):?當數據或指令預取終止時進入該模式,可用于虛擬存儲及存儲保護。

●??sys(系統模式):?運行具有特權的操作系統任務。

●??und(未定義指令中止模式):當未定義的指令執行時進入該模式,可用于支持硬件協處理器的軟件仿真。

ARM微處理器的運行模式可以通過軟件改變,也可以通過外部中斷或異常處理改變。

大多數的應用程序運行在用戶模式下,當處理器運行在用戶模式下時,某些被保護的系統資源是不能被訪問的。

除用戶模式以外,其余的所有6種模式稱之為非用戶模式,或特權模式;其中除去用戶模式和系統模式以外的5種又稱為異常模式,常用于處理中斷或異常,以及需要訪問受保護的系統資源等情況。

電子發燒友App

電子發燒友App

評論