32位處理器可以裝64位系統嗎?從技術角度看,32位處理器是不能裝64位系統的,因為不支持,不確定的用戶可以使用下面的兩種方法來檢查32位處理器是否能裝64位系統。方法:通過計算機評分查看1、以

2020-06-28 09:57:16

32位處理器的開發與8位處理器的開發有哪些明顯的不同?開發一個32位的嵌入式系統需要哪些工具和環境呢?32位嵌入式系統的開發過程中存在哪些技術難點?有什么方法去應對呢?

2021-04-19 08:11:43

功能和額外的性能,使得整個嵌入式系統的升級只需通過軟件的升級即可實現。而8位處理器通常受到的64K軟件限制也不存在了,設計者幾乎可以任意選擇多任務操作系統,并將應用軟件設計得復雜龐大,真正體現“硬件軟件

2017-04-06 09:11:03

的性能,使得整個嵌入式系統的升級只需通過軟件的升級即可實現。而8位處理器通常受到的64K軟件限制也不存在了,設計者幾乎可以任意選擇多任務操作系統,并將應用軟件設計得復雜龐大,真正體現“硬件軟件化

2017-06-02 18:52:49

的性能,使得整個嵌入式系統的升級只需通過軟件的升級即可實現。而8位處理器通常受到的64K軟件限制也不存在了,設計者幾乎可以任意選擇多任務操作系統,并將應用軟件設計得復雜龐大,真正體現“硬件軟件化

2018-07-04 08:50:08

8086處理器有何功能?中斷系統的功能都有哪些呢?

2021-10-29 07:07:41

ADSP-TS201SABP-050 245PCS現貨

2019-01-07 10:27:12

PCS.預計春節后3月份到貨。ADSP-TS201SAPBZ-060 在途400只+公司庫存285只=685PCS ADSP-TS201SAPBZ050 2404 PCS ADSP-TS201SABP-050 245 PCS ADSP-TS201SYBPZ050873 PCS

2018-12-21 19:48:14

控制器,支持SDRAM協議。以下就是這兩種協議的應用。4.1 SDRAM接口ADSP-TS201處理器有一個專用的SDRAM接口.可以實現與標準SDRAM 6 Mb,64 Mb,128 Mb.256

2019-04-12 07:00:11

{:12:}{:12:}{:12:}{:12:}{:12:}報道:ADSP-TS201誰用過

2012-09-19 14:14:35

用于多處理TigerSHARC系統的集群總線通信的詳細信號完整性和時序分析。該系統由8個ADSP-TS101S器件,一個主處理器和SDRAM組成,其集群總線運行頻率為100MHz。包括仿真結果和物理

2019-08-30 09:24:28

4月7日,全球權威AI基準測試MLPerf發布最新榜單,在聚焦低功耗、高能效的IoT領域Tiny v0.7榜單中,基于平頭哥玄鐵RISC-V C906處理器的軟硬件聯合優化方案,取得了全部4個指標

2022-04-08 14:47:36

寫了個雷達信號檢測的程序,包括經典的處理方法,MTI,多普勒濾波器組,單元平均選大恒虛警門限檢測等。分享出來,請大神指點,多謝。

2014-04-29 21:31:03

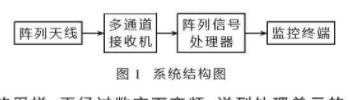

大,耗時長,精度低。隨著微電子技術和計算機技術的飛速發展,天線方向圖自動測試逐漸取代了手動測量,實現了信號錄取、數據處理以及方向圖繪制的自動化,大大提高了測量速度和精度。本文介紹了一種雷達天線方向圖的自動化測量系統,分析了軟硬件結構及原理。

2019-06-11 08:08:05

和 靜止 目 標對動 目 標檢測 的千擾 。4. 2 經典恒虛警 算法分析 圖 4-1 為雷達信 號處理流程 , 如 圖表示 回 波信 號經處理后在距離 維和速度維的能量分布情況。 若 當 前檢測

2018-02-28 09:19:59

和 靜止 目 標對動 目 標檢測 的千擾 。4. 2 經典恒虛警 算法分析圖 4-1 為雷達信 號處理流程 , 如 圖表示 回 波信 號經處理后在距離 維和速度維的能量分布情況。 若 當 前檢測 單元 為

2018-03-29 10:53:32

矢量中斷控制器(NVIC)與處理器核心緊密集成,以實現低延遲中斷處理。

?多個高性能總線接口。

?低成本調試解決方案,具有以下可選功能:

--實現斷點和代碼修補程序。

--實施監視點、跟蹤和系統分析

2023-08-08 07:18:05

解決方案。愛特公司通過擴大Core8051的支持范圍,使得開發便攜嵌入應用的設計人員能夠充分利用基于8051處理器的強大的開發生態系統和豐富的代碼資源,并全面發揮Actel FPGA的靈活性優勢。

2019-09-24 07:45:20

控制單元,調試系統以及標準的存儲映射。嵌套中斷向量控制器(Nested Vector Interrupt Controller,簡稱NVIC)是Cortex-M3處理器中一個比較關鍵的組件,它為基于Cort

2021-07-16 06:33:15

2.1STM32F103xx增強型LQFP48引腳分布2.2 STM32F103xx概述2.2.1ARM?的Cortex?-M3核心并內嵌閃存和SRAMARM的Cortex?-M3處理器是最新一代

2021-08-11 07:03:10

MSM8940處理器是什么?MSM8940處理器有哪些特點?

2021-11-09 07:09:11

什么是MT7628處理器呢?MT7628處理器有哪些特點呢?

2021-11-09 06:13:35

RK3188處理器有哪些特性呢?RK3168處理器具備哪幾大特點呢?RK3126處理器是什么?有何作用?

2022-02-18 07:21:37

RK3188處理器特征是什么?

2021-10-26 07:38:16

RK3399處理器與AR9201處理器有哪些不同之處呢?hi3559A處理器與RV1126處理器有哪些不同之處呢?

2022-02-21 07:29:27

S3C2410處理器通過GPD端口連接LED1-4四個燈,試著畫出其電路連接圖,并變成實現其逐一點亮功能。

2016-11-23 21:50:59

FPGA處理數據的時間,所以整個系統實現了流水線操作。1 系統的總體設計系統硬件主要由信號采集模塊、FIFO、FPGA和SEP3203處理器組成。信號采集模塊主要包括信號接收器和A/D轉換模塊。接收

2019-04-26 07:00:06

流水線操作。1系統的總體設計[1-2]系統硬件主要由信號采集模塊、FIFO、FPGA和SEP3203處理器組成。信號采集模塊主要包括信號接收器和A/D轉換模塊。接收到的信號首先要通過NE5534進行

2018-12-05 10:13:09

STM32處理器的啟動方式是什么?

2021-11-29 07:48:02

和預測性維護),有助于賦予HMI全新的意義,而不是僅限于實現人機交互的界面。AM62處理器能夠以低功耗實現邊緣器件的分析功能(掛起狀態功耗低至7mW且無需特殊考慮散熱設計),支持工程師靈活地在尺寸受限

2022-11-03 06:11:50

TMS320C6678處理器的性能怎么樣?怎么探討TMS320C6678處理器的VLFFT演示?

2021-04-19 10:53:46

飛思卡爾塔式系統是什么?TWR-P1025處理器模塊目標應用是什么?

2021-05-25 06:36:00

的處理器體系上。本文主要完成基于Cortex-M3處理器的μC/OS-III移植,通過本次移植,加深對嵌入式操作系統原理的理解。此外,在μC/OS-III移植成功的基礎上進行嵌入式應用程序開發,可以把

2020-03-31 08:19:15

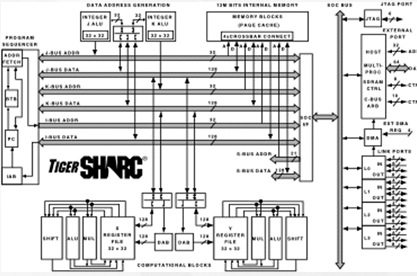

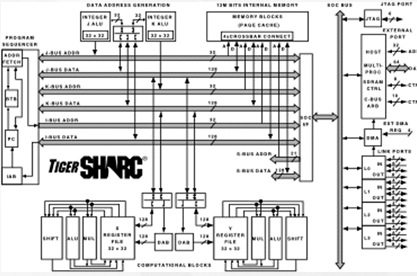

本文主要結合ADI公司的高性能ADSP-TS201的結構特點,討論了在系統設計的過程中應該重點注意的幾個問題和ADSP-TS201的外部接口技術,并給出了其與SDRAM,FPGA的連接實例,對基于TigerSHARC系列DSP的應用設計具有實用的參考價值。

2021-05-27 06:59:04

現經過測試的軟件部分將會正常工作,這會節省項目后期的大量時間及努力。軟硬件聯合仿真系統由一個硬件執行環境和一個軟件執行環境組成,通常軟件環境和硬件環境都有自己的除錯和控制界面,軟件通過一系列由處理器啟動

2008-07-17 08:56:46

類別:嵌入式系統處理器知識產權許可商ARMHoldingsplc已經成功開發出雙內核Cortex-A9處理器設計(被稱為Osprey)的兩個實現。Cortex-A9處理器能與其他Cortex系列

2021-12-13 06:03:17

摘要:簡要介紹了軟硬件協同仿真技術,指出了在大規模FPGA開發中軟硬件協同仿真的重要性和必要性,給出基于Altera FPGA的門級軟硬件協同仿真實例。 關鍵詞:系統級芯片設計;軟硬件協同仿真

2019-07-04 06:49:19

了該采集系統的性能。筆者認為該設計方法同樣適合于電力行業中其他一些實時性強、運算量大、功能復雜的多路采集分析裝置中,以該設計思路替代以往的CPU+DSP,CPU+FPGA等多處理器芯片的設計方法,可實現系統級優化設計。

2013-01-22 16:41:56

本文針對高精度波形發生器的開發,進行了以AD760為核心的波形發生器的軟硬件系統設計。

2021-04-12 06:54:00

如何使用KEIL進行軟硬件仿真

2012-08-20 14:14:51

什么是DSP流水線協議?如何利用FPGA與ADSP TS201去設計總線接口?

2021-04-28 06:31:06

在雷達信號處理、數字圖像處理等領域中,信號處理的實時性至關重要。由于FPGA芯片在大數據量的底層算法處理上的優勢及DSP芯片在復雜算法處理上的優勢,DSP+FPGA的實時信號處理系統的應用越來越廣泛。那么,我們該怎么利用FPGA與ADSP TS201設計總線接口呢?

2019-08-09 06:56:11

本文將詳細講解基于Inte1的PXA255處理器的Sitsang開發平臺紅外模塊的設計,其中包括Linux下的IrDA驅動程序的開發和基于MC68HC908AP64紅外發射器的軟硬件設計兩個部分。

2021-04-27 06:03:57

RCC時鐘樹是由哪些部分組成的?如何去實現RCC系統時鐘的軟硬件設計呢?

2021-11-10 07:20:39

什么是軟硬件協同設計呢?片上可編程系統SoPC是什么?如何去實現一種基于SoPC的軟硬件協同設計呢?基于SoPC的軟硬件協同設計有何功能呢?

2021-12-24 07:15:15

我們目前使用的是OMAPL138處理器,然后在處理器上運行嵌入式Linux系統;在這個平臺基礎上,我們希望使用藍牙+WiFi功能。

1、請問我們可以使用什么模塊進行操作?

2、考慮過WL1831mod模塊,但是這個模塊好像只支持AM335X系列,不支持OMAPL138處理器。

謝謝。

2018-06-21 03:55:06

新型車輛模擬駕駛訓練系統的組成及工作原理是什么怎么實現動感系統的總體構想及其軟硬件設計?

2021-05-12 06:15:16

介紹國家半導體公司(NS)的Geode TMGX1處理器及協同芯片,說明如何利用該芯片組進行嵌入式系統設計,并討論一些設計難點的處理。

2019-09-05 07:30:36

RK3328處理器主要有哪些功能呢?RK3328處理器有哪些基本參數呢?怎樣去搭建RK3328處理器的編譯環境呢?

2022-03-09 06:50:34

:JSJK.0.2010-04-037【正文快照】:1引言可重構片上系統上包含了執行軟件程序的微處理器核和實現硬件邏輯的可重構器件,因此設計人員需要通過軟硬件劃分來將應用所需完成的功能有效地映射到這兩種類型的運算

2010-05-28 13:40:38

瑞星微3288處理器的主要硬件指標有哪些?

2022-03-03 07:29:09

和額外的性能,使得整個嵌入式系統的升級只需通過軟件的升級即可實現。而8位處理器通常受到的 64K軟件限制也不存在了,設計者幾乎可以任意選擇多任務操作系統,并將應用軟件設計得復雜龐大,真正體現“硬件軟件化

2016-08-08 14:52:14

ADSP-TS201的鏈路口程序應怎么寫啊,毫無頭緒啊,寄存器也看不懂,ADI公司沒找到參考的鏈路口程序啊

2018-12-10 09:17:06

請問RISC處理器和ARM7處理器的區別在哪?求大神解答

2022-06-30 17:51:06

片上Nios Ⅱ嵌入式軟核多處理器系統具有哪些優勢?如何實現片上嵌入式Nios Ⅱ軟核六處理器系統的設計?

2021-04-19 08:17:09

在機載SAR 的實時成像處理器中,回波信號方位向帶寬以及方位向采樣率不能很好的滿足成像處理的要求,本文選擇ADSP-TS201 處理器芯片對回波信號在成像之前對其進行方位向預處

2009-08-05 09:45:52 18

18 總體描述:ADSP-TS201S TigerSHARC處理器是-款超高性能針對大信號優化的靜態超標量處理器性能處理任務和通信基礎設施。數字信號處理器結合了非常寬的內存寬度和雙重計塊一支持浮點

2023-05-10 15:53:12

摘 要 文主要介紹了一種采用軟硬件協同設計策略的用于生理信號處理的低功耗醫學集成芯片。軟硬件協同設計能達到性能和設計靈活性的最大化。系統硬件包括ARM7TDMI處理器,AHB兼

2010-06-19 10:29:54 24

24 描述ADSP-TS201S是TigerSHARC處理器系列中的最新款器件之一。ADI公司的TigerSHARC處理器面向眾多依靠多個處理器共同工作來執行計算密集型實時功能的信號處理應用,非常適合

2024-01-26 11:33:09

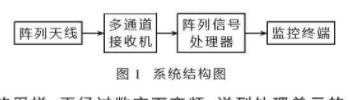

介紹了一種基于ADSP-TS201的無線電測向系統。給出了系統的總體結構和工作原理,研究了MUSIC測向算法及基于零點預處理的波束合成算法,介紹了DSP模塊的設計思想和程序流程圖。實

2010-11-22 14:52:42 39

39 FPGA與ADSP TS201的總線接口設計

在雷達信號處理、數字圖像處理等領域中,信號處理的實時性至關重要。由于FPGA芯片在大數據量的底層算法處理上的優勢及DSP芯片在復雜

2009-12-11 10:13:29 2356

2356 特征: 處理器: 每簇由兩個可以達到600MHz的ADSP-TS201 DSP處理器;整板共兩簇。每個DSP可以進行3.6 GFLOPS的浮點處理能力(每個板上有4個處理器,就可以進行14.4GFLOPS的處理能力)。每個DSP芯片內有24MbitsRAM哈佛超標量體系結構; 一個用于接口連接和協處

2011-02-25 15:49:54 75

75 針對數字信號處理器的不同仿真和驗證要求,提出了一種可測性軟硬件協同仿真和驗證平臺的設計. 采用可配置IP 模塊和總線結構,實現了硬件平臺可配置性和可重用性;采用在線仿真模塊

2011-06-09 17:54:21 39

39 為了解決 雷達信號處理 中的高速運算, 大容量存儲和高速數據傳輸的問題, 提出采用 TS201 芯片實現雷達信號處理機設計, 利用其超高性能的處理能力和易于構造多處理并行系統的特

2011-07-20 17:20:13 65

65 數字信號處理器DSP是一種具有特殊結構的微處理器,它專門為實現數字信號處理的各種算法而設計,因而在硬件結構上具有特殊性。TS201是ADI公司TigerSHARC系列中集成了定點和浮點計算功

2011-09-21 11:59:38 1964

1964 設計并實現了一種基于ADSP TS201的組網雷達數據融合實時處理系統。主要闡述了雙ADSP TS201并行處理系統的結構、算法量的估計與結果分析。系統可滿足集中式組網融合和分布式組網融合

2011-10-09 10:49:40 30

30 基于ADSP_TS201S的多DSP并行系統設計

2015-12-29 17:33:04 22

22 大規模集成電路技術的發展,作為數字信號處理的核心數字信號處理器(DSP)得到了快速的發展和應用。ADSP-TS201DSP是美國模擬器件(ADD公司繼TSl01之后推出的一款高性能處理器。此系列DSP性價比很高,兼有FPGA和ASIC信號處理性能和指令集處理器的高

2017-10-20 15:01:32 0

0 ,不利于硬件的開發進度。面對這一難題,文章從FPGA 的軟硬件協同測試角度出發,利用PC 機和測試硬件設備的特點,進行FPGA 的軟硬件協同測試的設計,努力實現FPGA 的軟硬件協調測試系統在軟硬件的測試和分析中的應用。

2017-11-18 05:46:28 1616

1616 現代雷達信號處理已成為雷達功能實現的關鍵,本文根據某型雷達信號處理機的系統需要,對其硬件結構及軟件設計做了系統優化。設計了1套以4片 TS201和1片FPGA為核心信號處理板,該系統僅用l副板卡

2017-12-11 02:21:07 1881

1881

TS201是ADI公司繼ADSP-TS101之后又推出的新一代高性能Tiger-SHARC處理器,它集成了更大容量的存儲器,性價比很高。它兼有ASIC和FPGA的信號處理性能和指令集處理器的高度可編程性與靈活性,適用于高性能、大存儲量的信號處理和圖像應用。其特點如下:

2020-08-27 09:05:59 2258

2258

模擬器件公司(Analog Devices)推出的下一代TigerSHARC處理器ADSP-TS201,ADSP-TS-202和ADSP-TS203。它的每瓦DSP性能是最高的。

2021-01-11 12:01:00 1803

1803

ADSP-TS201 EZ-KIT Lite電路板設計數據庫

2021-04-13 12:13:17 1

1 EE-201:ADSP-TS20x TigerSHARC?處理器片上SDRAM控制器

2021-04-13 18:00:50 6

6 EE-198:ADSP-TS201S TigerSHARC?處理器IBIS文件用戶指南

2021-04-13 18:10:30 8

8 ADSP-TS201S:TigerSHARC嵌入式處理器過時數據表

2021-04-15 18:45:56 6

6 EE-205:將代碼從ADSP-TS101S TigerSHARC?處理器移植到ADSP-TS201S TigerSHARC處理器的注意事項

2021-04-16 13:54:51 9

9 EE-170:評估ADSP-TS201S TigerSHARC?處理器的功耗

2021-04-21 10:41:30 6

6 EE-182:ADSP-TS201S TigerSHARC?處理器的散熱設計

2021-04-22 09:46:01 10

10 ADSP-TS201 TigerSHARC處理器編程參考

2021-05-18 09:21:19 1

1 ADSP-TS201 TigerSHARC處理器硬件參考

2021-05-18 15:46:19 1

1 ADSP-TS101 TigerSHARC處理器硬件參考

2021-05-22 10:59:30 4

4 EE-218:為ADSP-TS201 TigerSHARC?處理器編寫高效浮點FFT

2021-05-26 09:17:20 5

5 評估板上的兩個ADSP-TS201S處理器和基礎調試軟件,以便通過基于USB、可在PC中運行的工具集進行架構評估。 利用該EZ-KIT Lite,用戶可以了解有關ADI公司ADSP-TS201S硬件與軟

2021-06-09 08:59:50 4

4 ADSP-TS201 EZ-KIT Lite電路板設計數據庫

2021-06-17 16:05:58 0

0 EE-201 ADSP-TS20x TigerSHARC?處理器片上SDRAM控制器

2021-06-18 10:47:01 4

4 EE-198 ADSP-TS201S TigerSHARC?處理器IBIS文件用戶指南

2021-06-18 11:13:33 2

2 軟件和硬件需要定義好交互的“接口”,通過接口實現軟硬件的“解耦”。例如,對CPU來說,軟硬件的接口是指令集架構ISA:ISA之下的CPU處理器是硬件,指令集之上的各種程序、數據集、文件等是軟件。

2022-12-07 14:23:15 1852

1852 電子發燒友網站提供《基于ADSP-TS201的著陸雷達恒虛警電路實現.pdf》資料免費下載

2023-10-23 09:59:21 0

0 電子發燒友網站提供《TigerSHARC? ADSP-TS201S處理器的散熱設計要點.pdf》資料免費下載

2023-11-29 11:12:01 0

0

正在加载...

電子發燒友App

電子發燒友App

評論