隨著多媒體圖像處理應用的迅速發(fā)展,體積小、重量輕、結構靈活、處理能力強的嵌入式數(shù)字圖像處理系統(tǒng)在工業(yè)、醫(yī)學等方面都有越來越廣泛的需求。實時性高、計算復雜、數(shù)據(jù)量大是圖像處理系統(tǒng)面臨的重大挑戰(zhàn)。并行計算是提高處理速度最有效的技術之一,圖像并行處理技術為提高圖像處理效率提供了廣闊的空間。圖像并行處理包括并行算法和多處理器并行硬件系統(tǒng),圖像處理并行算法的執(zhí)行效率依賴于多處理器系統(tǒng)的硬件結構。通常,一種并行結構只適合于一類并行算法的映射。

20世紀90年代至今,圖像并行處理技術一直是圖像處理領域研究的熱點之一。參考文獻分別對并行處理結構及其實現(xiàn)方法進行了探討,提出了流水結構、分列并行等很有價值的硬件并行結構框架。目前,圖像并行處理結構設計面臨的主要問題可以概括為兩個方面:

①圖像并行處理硬件結構復雜,在實際應用中圖像處理結構的開發(fā)周期長、成本高;

②面向圖像處理算法的硬件結構針對性設計方法導致圖像處理平臺的可重用性差,調整、擴展和升級困難。

本文構建的可重構并行計算系統(tǒng)可以通過配置可重構處理單元來滿足不同應用的計算要求。這樣的系統(tǒng)使圖像處理結構設計與圖像處理的算法設計分離,具有很高的性能并且結構靈活,能大大提高圖像處理并行算法的執(zhí)行效率和加速比。

1 傳統(tǒng)圖像并行處理技術

1.1 圖像并行處理系統(tǒng)概述

目前,用于嵌入式圖像處理系統(tǒng)的高速器件主要是DSP和FPGA。處理核心的合理選用是影響并行系統(tǒng)處理能力的一個關鍵因素。

并行處理的目的是通過采用多個處理單元同時處理輸入信息來縮短任務的執(zhí)行時間。在任務和算法確定的情況下,Amdahl定律可表明:加速比與任務并行度和處理單元個數(shù)密切相關。在任務并行度一定的情況下,增加處理單元所獲得的加速比有一個極限值,任務的并行度制約著并行處理機的性能。

在實際應用中,還必須考慮各個處理單元之間的數(shù)據(jù)交換和同步時間。由于比串行程序執(zhí)行增加了數(shù)據(jù)通信和同步等待等開銷,因此當加速比Sp

如圖1所示,在增加處理單元和任務細粒度化的同時將帶來總通信量的增加,影響了Sp的增加并導致Eff呈下降趨勢。

1.2 并行計算硬件體系結構

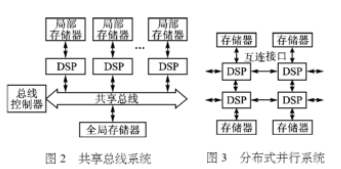

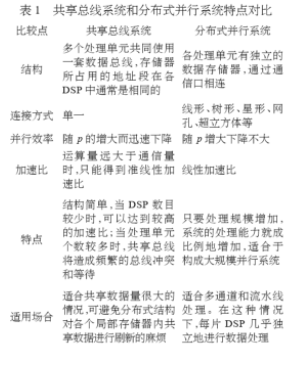

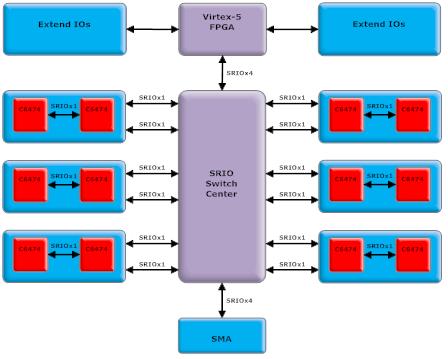

并行計算處理單元之間的網(wǎng)絡結構大致可分為2種:一種是共享總線或共享存儲器系統(tǒng),稱為“緊耦合式并行系統(tǒng)”,如圖2所示;另一種是各處理單元有獨立的數(shù)據(jù)存儲器而通過通信口相連的分布式并行系統(tǒng),稱為“松耦合式系統(tǒng)”,如圖3所示。

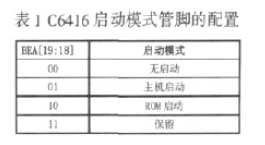

兩種并行計算體系結構的比較如表1所列。

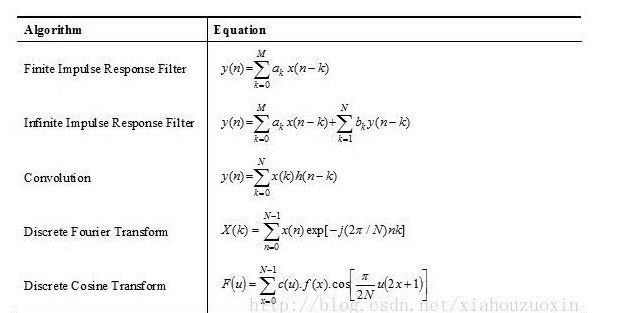

1.3 并行算法到并行結構的映射

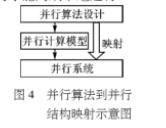

一個任務要在多處理機系統(tǒng)上得到處理,首先必須將其分解成一些子任務,再由多處理系統(tǒng)中的各處理機分別處理這些子任務,協(xié)同完成該任務。如圖4所示,并行算法在并行硬件系統(tǒng)上的應用是一個映射過程。一類并行算法依賴于適合的并行網(wǎng)絡結構才能高效率地運行。

導致并行算法與并行結構不匹配的原因主要有2個:一是欲把一個系統(tǒng)上開發(fā)的并行算法用于另一個系統(tǒng)上;二是由于問題內在的并行性,使并行算法與并行結構不匹配。

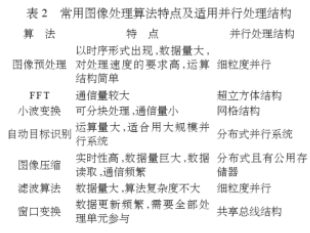

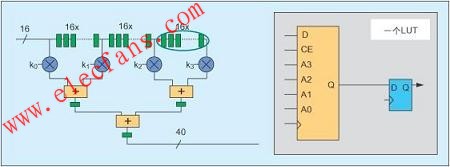

常用圖像處理算法的特點及適用的并行處理結構分析如表2所列。

綜上所述,傳統(tǒng)的共享總線系統(tǒng)與分布式并行系統(tǒng)分別適用于不同的圖像并行處理算法。分布式并行系統(tǒng)的不同連接方式之間也有較大的差異。并行算法的高效率運行依賴于并行硬件拓撲結構的支持,某種硬件結構只適合一類并行算法。一般情況,一個圖像處理任務是多個算法的集合,并行系統(tǒng)單靠某種固定結構無法適應所有的并行算法,這就給圖像處理系統(tǒng)帶來了問題。當并行硬件拓撲結構不適合并行算法時,系統(tǒng)的性能和算法執(zhí)行效率都會受到影響,需要對并行硬件結構做出改進和完善。

2 可重構數(shù)字圖像并行處理系統(tǒng)

2.1 可重構處理系統(tǒng)的組成

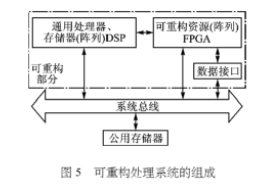

可重構計算是指基于可改變(可動態(tài)改變)的硬件,以硬件適應算法(即可重構特性)、硬件定制和硬件并行的方式實現(xiàn)計算。可重構處理系統(tǒng)結合了可重構硬件處理單元和軟件可編程處理器,系統(tǒng)允許對可重構處理單元進行配置以滿足不同應用的具體計算要求。

如圖5所示,可重構處理系統(tǒng)的組成基本相同,即通用處理器(陣列)、可重構資源(陣列)、存儲器(陣列)、公用存儲器、系統(tǒng)接口等。面向圖像處理的可重構系統(tǒng)在器件選用上通用處理器可采用適合圖像處理的高性能DSP陣列。

2.2 可重構數(shù)字圖像并行處理系統(tǒng)的優(yōu)點

可重構數(shù)字圖像并行處理系統(tǒng)有以下優(yōu)點:

①FPGA內部的邏輯功能可以在系統(tǒng)運行過程中動態(tài)重載,使系統(tǒng)可以實現(xiàn)多DSP之間拓撲的靈活改變以適應各種并行算法的需求,使算法執(zhí)行效率達到最高。靜態(tài)重構和動態(tài)重構使系統(tǒng)相比傳統(tǒng)固定系統(tǒng)具有很強的通用性和適應性。

②系統(tǒng)的“多DSP+FPGA”結構能將系統(tǒng)任務劃分成適合FPGA處理的低層信號處理和圖像預處理部分及適合DSP處理的算法,便于發(fā)揮兩者的優(yōu)勢;且FPGA可通過軟件適應不同時序格式的數(shù)字圖像,使得系統(tǒng)具有很高的性能和靈活性。

3 系統(tǒng)設計實例

3.1 系統(tǒng)硬件結構

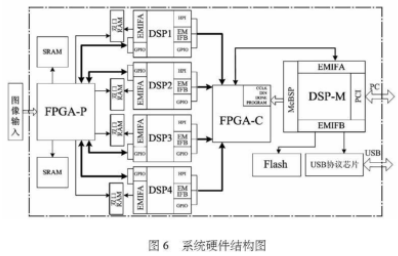

基于TI公司C6000系列DSP和Xilinx公司Spartan一3系列FPGA,構建基于圖像的點源目標識別系統(tǒng),對在線可重構數(shù)字圖像并行處理系統(tǒng)的可實現(xiàn)性和性能進行驗證。

硬件結構如圖6所示。圖像輸入FPGA—P,各DSP分別外擴一片雙口RAM,且將總線EMIFA接到FPGA—P。FPGA—P可用來完成圖像時序處理、圖像數(shù)據(jù)的轉換、圖像濾波等預處理工作,且可以靈活地將處理后的圖像數(shù)據(jù)保存到大容量公用數(shù)據(jù)存儲器SRAM中,并將各DSP訪問的仲裁邏輯或分配保存到各DSP外擴的雙口RAM中。這種結構使系統(tǒng)可以輕松地適應多路圖像輸入。

DSP陣列可以并行完成各種圖像處理算法。FPGA-C建立起DSP間的通信鏈路且暫存各DSP的處理結果。構建通信鏈路的方法有:用FPGA—C在兩 DSP之間構造FIF0或小容量雙口RAM,構建EMIF—HPI通路等。DSP-M可以根據(jù)算法需求通過McBSP在線配置FPGA—C,F(xiàn)PGA—C 的配置文件存放在DSP—M外擴的Flash中,這樣就實現(xiàn)了DSP對FPGA的在線可重構。同時,DSP-M擴展了USB、PCI、McBSP等多種接口用來輸出圖像處理結果。

3.2 實驗及結果分析

系統(tǒng)用于實現(xiàn)4路分辨率為256×256、幀頻為50 Hz的8位圖像(如圖7所示)的移動點源目標識別。

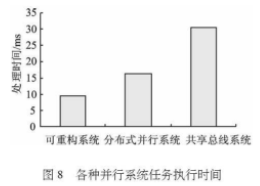

處理過程包括圖像時序采集、轉換,圖像濾波,去除噪聲,姿態(tài)融合和目標識別等環(huán)節(jié)。圖像分配和算法執(zhí)行所需平均時間僅為9.5 ms。

若用共享總線系統(tǒng)來實現(xiàn),則多路圖像數(shù)據(jù)的存儲和分配以及處理器之間的通信將消耗大量時間,大大降低系統(tǒng)效率。若用分布式并行系統(tǒng)來實現(xiàn),則姿態(tài)和多路圖像的綜合處理會給某一個處理器帶來很大的通信量和運算量。將實驗中的圖像處理任務在同等規(guī)模的3種系統(tǒng)上分別實現(xiàn),執(zhí)行時間如圖8所示。

如圖9所示,這些不同形式的計算系統(tǒng)是性能和通用性的不同折衷。可重構算系統(tǒng)代表了介于ASIC和通用處理器之間的計算途徑,在通用性和性能上都優(yōu)于傳統(tǒng)的硬件系統(tǒng)。圖像處理中數(shù)據(jù)量大、算法復雜,與其他計算技術相比,可重構計算能充分發(fā)揮出效率優(yōu)勢。可重構系統(tǒng)具有很多優(yōu)點,但重構延遲和軟硬件劃分問題是應用中需要重點考慮的問題。

結 語

傳統(tǒng)固定結構并行圖像處理系統(tǒng)不能適應多種圖像處理并行算法。而可重構數(shù)字圖像并行處理系統(tǒng)數(shù)據(jù)流和結構組織靈活,適于模塊化設計,能大大提高并行算法的執(zhí)行效率;有較強的通用性,同時其開發(fā)周期較短,易于維護和擴展。可重構數(shù)字圖像并行處理系統(tǒng)為多媒體圖像處理提供了一個非常有價值的發(fā)展方向。

責任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評論