DSP(Digital Signal Processor)是一種獨特的微處理器,是以數字信號來處理大量信息的器件。它強大的數據處理能力和高運行速度,是最值得稱道的兩大特色。隨著網絡技術的發展,在工業控制、智能儀器、智能家庭等領域,越來越多的DSP設備要求具有以太網通信功能,以便與外部網絡設備進行數據通信。以太網控制芯片是以太網接口的核心器件,其性能是影響網絡性能的關鍵因素之一,如何正確使用網絡控制器是設計以太網接口的關鍵。本文采用處理器+以太網控制芯片+TCP/IP協議的DSP以太網接入方式,設計并實現了基于DSP的精簡TCP /IP協議棧,并固化在DSP內,無需操作系統也可運行。

1 總體設計

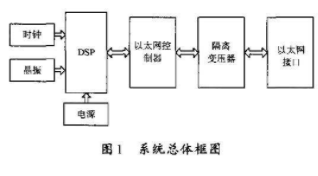

本系統使用32位DSP處理器TMS320F28335和以太網控制芯片DM9000A為核心,DSP控制整個系統的運行,DM9000A實現網絡傳輸的底層功能。并對TCP/IP協議棧自行裁剪,構成了DSP的以太網接口,實現了網絡通信。其系統總體框圖如圖1所示。

2 系統硬件設計

2.1 DM9000A功能結構

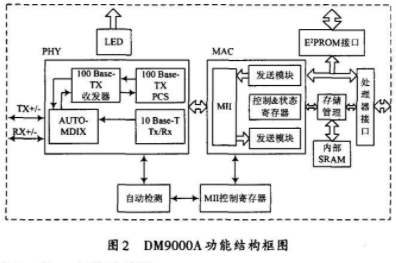

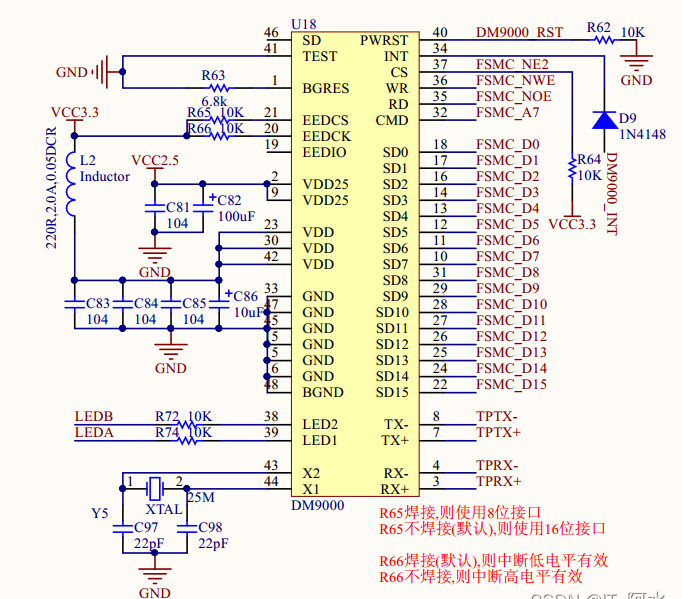

DM9000A是DAVICOM公司推出的一款高度集成、低成本的快速以太網控制器,實現以太網媒體介質訪問層(MAC)和物理層(PHY)的功能。該芯片具有通用的處理器接口,片內集成了10/100M自適應的PHY,內部含有16 KB SRAM用于接收/發送的FIFO緩存,3.3 V供電,并且支持IEEE 802.3以太網傳輸和8/16接口的兩種主機工作模式協議。功能結構如圖2所示。

2.2 接口電路的連接

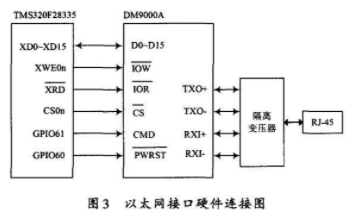

接口電路主要由DSP、以太網控制芯片DM9000A、隔離變壓器和RJ-45構成。DSP控制整個系統的運行,DM9000A實現以太網數據的底層傳輸。隔離變壓器的主要作用:其一,可以增強信號,使其傳輸距離更遠;其二,使芯片端與外部隔離,增強抗干擾能力,并對芯片端起保護作用;其三,當接到不同電平(如有的PHY芯片是2.5 V,有的PHY芯片是3.3 V)的網口時,不會對彼此設備造成影響。RJ-45接口可用于連接RJ-45接頭,適用于由雙絞線構建的網絡,這種是最常見的以太網接口。DM9000A采用16位接口模式,數據地址復用總線D0~D15與DSP總線XD0~XD15相連;DM9000A的寫信號引腳與DSP的XWE0n相連;讀信號引腳與DSP的讀引腳相連;DM9000A的片選信號引腳與DSP的CS0n相連;DM9000A的訪問類型引腳CMD與DSP的普通I/O口GPIO61相連,高電平訪問DM9000A的數據端口,低電平訪問地址端口;DM9000A的復位引腳與DSP的GPIO 60相連;DM9000A的物理層接口TX+,TX-,RX+,RX-通過隔離變壓器連接RJ-45至以太網。其以太網接口硬件連接如圖3所示。

3 系統軟件設計

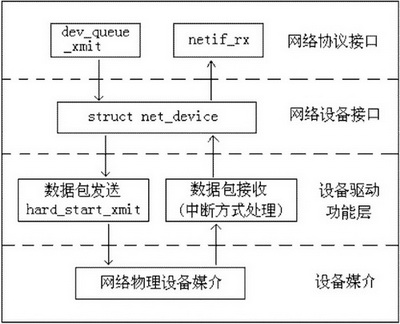

網絡接口的軟件主要有DM9000A驅動程序設計和上層通信協議程序設計兩個部分。DM9000A驅動程序設計主要是通過TMS320F28335控制總線配置DM9000A內部寄存器,完成對DM9000A初始化、以太網數據幀的發送和以太網數據幀的接收三部分。上層通信協議程序設計是對TCP/IP棧裁剪移植,主要完成對接收到的以太網數據幀進行解析并處理,并把要發送的數據封裝成以太網數據,然后發送。

3.1 DM9000A驅動程序設計

3.1.1 DM9000A初始化

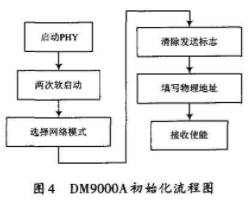

DM9000A正常工作需要在上電后對內部寄存器進行初始化,具體流程如下:

(1)啟動PHY。設置通用寄存器GPR(1FH)的GEPIO0=0。

(2)進行兩次軟啟動。設置網絡控制寄存器NCR(00H)的RST=1,10μs后RST=0,同樣的操作進行兩次。

(3)選擇網絡模式。設置NCR的LBK=00,設置網絡工作模式為正常模式。

(4)清除發送標志。設置網絡狀態寄存器NSR(01H)WAKEST=1,TX2END=1,TX1END=1。

(5)寫6 B的以太網節點地址到物理地址寄存器PAR(10H~15H)中。

(6)設置中斷屏蔽寄存器IMR(FFH)的PAR=1,使能指針自動跳回,當SRAM讀/寫指針超過SRAM的大小時,指針自動跳回起始位置;PRI=1,使能數據包接收中斷。

(7)設置接收控制寄存器RCR(05H)的WTDIS=1,看門狗定時禁止;DSI_LONG=1,丟棄長數據包;DIS_CRC=1丟棄CRC校驗錯誤的數據包;RXEN=1,使能接收功能。

初始化流程如圖4所示。

完成上述初始化步驟后,DM9000A就處于正常工作狀態,可以收發數據包。若有異常發生,就需要重復上述步驟,重啟DM9000A以使芯片恢復到正常狀態。

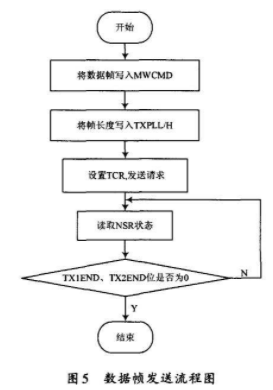

3.1.2 數據幀發送

DM9000A內部有16 KB的SRAM作為接收/發送數據的緩存區,其中前3 KB的空間,地址從0x0000H~0x0BFFH,用來緩存需要發送的數據。

數據發送的具體步驟如下:

(1)利用寫操作寄存器MWCMD(F8H),將需要發送的數據幀寫入DM9000A的發送緩存區。

(2)將數據幀長度寫入長度寄存器TXPLL(FCH)和TXPLH(FDH)。

(3)設置發送控制寄存器TCR(02H),TXREQ=1,數據幀開始發送。

(4)檢查網絡狀態寄存器NSR(01H)的TX2END和TX1END位,判斷此幀數據是否發送完。

數據幀發送流程圖如圖5所示。

3.1.3 數據幀接收

當DM9000A數據接收使能后,DM9000A就會自動接收數據。DM9000A接收到的數據先保存在地址從0x0C00~0x3FFF的13 KB內部SRAM緩存空間中,它是一個環形結構。

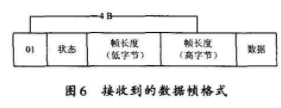

利用寄存器MRCMDX(FOH)和寄存器MRCMD(F2H)可獲取緩存中的數據幀信息。接收到的數據幀格式如圖6所示。

其中第1個字節是接收數據標志字節,表征接收到數據幀是否有效。第2個字節是接收數據幀的狀態字節,其中的內容與接收狀態寄存器RSR中的內容相同,可以用來判斷所接收的數據幀是否正常。第3,4個字節是接收到數據的長度字節,其中低位在前,高位在后。從第5個字節開始的數據才是真正數據幀內容。

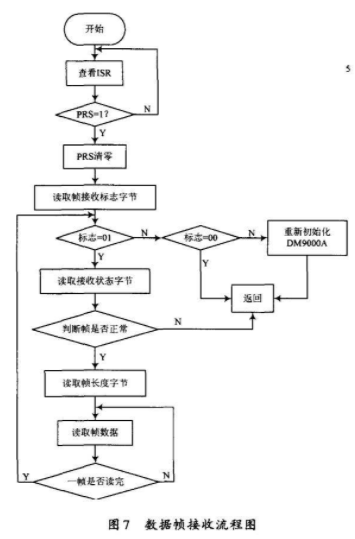

數據接收過程如下:

(1)檢查中斷狀態寄存器:ISR(FEH),若PRS位為1,說明有新的數據幀接收,寫1清除PRS位;若為0,說明無數據,直接返回。

(2)讀取第1個字節,即接收數據標志字節。如果該字節為01,則表示接收下來的是有效數據幀;如果該位為00則表示沒有數據到達,或數據已經接收完成;如果既不是01又不是00,則認為有異常發生,這時就要將DM9000A芯片重啟以使芯片恢復到正常狀態。

(3)讀取第2個字節,即接收狀態字節。根據接收狀態字節判斷所接收的數據幀是否正常。

(4)讀取第3,4字節,即數據幀長度字節。

(5)讀取真正的數據幀內容。

(6)根據獲取的長度信息,判斷是否讀完一幀。如果讀完,接著讀下一幀,直到遇到首字節是00H的幀,說明接收數據已讀完。

數據幀接收流程如圖7所示。

3.2 上層通信協議程序設計

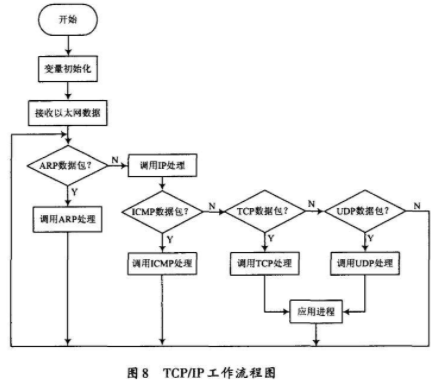

TCP/IP協議模型可以分為四個層次,從下到上依次為:鏈路層、網絡層、傳輸層和應用層。每一層都有不同的功能,低一層為高一層提供服務。

標準的TCP/IP協議棧對處理器的計算、存儲要求比較高,然而,DSP系統的計算資源和存儲資源通常是非常有限,在DSP中實現標準的TCP/IP協議棧將占用大量系統資源,不利于DSP其他方面的應用,因此必須對它進行簡化并優化,盡可能做到代碼精簡,降低存儲開銷。本系統設計和實現了TCP/IP通信協議的必要部分,包括:ARP,IP,ICMP,TCP,UDP等協議。

ARP(地址解析協議)為IP地址到對應的硬件地址之間提供動態映射。IP協議是TCP/IP協議的核心,所有的TCP,UDP,ICMP的數據都是以IP數據格式傳輸的。ICMP(網絡控制報文)是用來傳遞差錯報文以及其他需要注意的信息,有各種類型的ICMP報文,本文只用到ICMP的請求回顯(類型字段為8、代碼字段為0)。TCP提供一種面向連接的、可靠的字節流服務,交換數據之前必須先建立一個TCP連接,即“三次握手”UDP是一個簡單的面向數據報的傳輸層協議,它把應用程序傳給IP層的數據發送出去,但是并不保證他們能到達目的地。在鏈路層,當DM9000A完成一個以太網數據幀接收后,將其讀入暫存數組,檢查以太網幀類型字段,該字段值為0x0806,表示數據幀為ARP幀;該字段的值為0x0800,表示數據幀為IP幀。接著,分別交由ARP協議處理模塊或IP協議處理模塊。編程時使用框架如下:

if(完成以太網數據幀接收)

{ if(以太網類型字段==0x0806)

{ARP處理模塊}

if(以太網類型字段==0x0800)

{IP處理模塊}

}

網絡層收到的為ARP數據報,ARP根據操作字段(ARP請求為1,ARP應答為2),或者發送ARP應答或者更新ARP地址映射表。若為IP數據報,IP協議處理模塊對數據包解析后,IP首部協議字段若為1就將數據交給ICMP協議處理模塊,若為6則交給TCP處理模塊,若為17則交給UDP處理模塊。傳輸層得到UDP的報文后,按照UDP協議中的端口,分別送給不同的應用層序。若傳輸層得到的是TCP報文,則要根據TCP的狀態轉換圖進行處理。在TCP或UDP的處理模塊中,根據目的端口號,分別將數據送往不同的用戶應用程序。其工作流程如圖8所示。

4 結語

本文把高度集成、低成本的快速以太網控制器DM9000A與數據處理能力強大、高運行速度的DSP(TMS320F28335)相結合,設計出了一種DSP的以太網接口。實驗結果表明,DSP系統可以通過該接口實現以太網數據通信,經自行裁剪的TCP/IP協議棧,不僅實現了IP,ARP,ICM P,TCP和UDP協議,而且提高了數據傳輸效率。該接口具有硬件接口簡單、外圍器件少、運行穩定可靠、性價比高等特點,同時也能夠滿足測試、采集等高速數據傳輸系統的要求,符合當今DSP設備趨于網絡化發展的方向。

責任編輯:gt

電子發燒友App

電子發燒友App

評論