作者:齊崠清,趙加祥,袁鑫

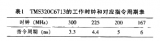

本系統使用TI公司浮點型DSP TMS320C6713實現G.723.1等語音編解碼,為G.723.1、G.729等常用的低碼率語音壓縮標準提供運行及測試硬件平臺。有別于大多數編解碼系統,本設計采用了性能更好的浮點型處理器和20位以上的數模模數轉換器,總線帶寬提高為16位,并采用主控性更強的HPI 接口。系統設計具有以下優勢:(1)數據的傳輸通過USB口完成,完全支持速度在5.3 Kb/s或6.3 Kb/s的多路編碼輸出,方便用戶使用,并可使用USB獨立供電。(2)利用USB控制芯片的GPIF模式與DSP連接,程序簡單、修改靈活。采用主頻300 MHz、處理速度2 400 MIPS/1 800 MFLOPS的TMS320C6713,可以使每幀數據的處理時間小于37 ms的幀延遲,滿足系統運行的實時性。(4)數據的傳送工作交由USB控制芯片68013完成,可使DSP從繁瑣的數據搬運及USB協議處理工作中獨立出來,使更多的資源用于數據處理。(5)采用由主機加載固件的方法,節省數據處理端的硬件與軟件資源,而且便于固件的更新升級。(6)采用DSP中的外設接口HPI與主機相連,由主機掌握主控權,既能夠使數據訪問得到簡化還可以通過HPI實現DSP自舉。

1 基本概念介紹

1.1 CY7C68013性能特點

CY7C68013(EZ-USB FX2)是Cypress半導體公司的新一代高速USB系列,可以用USB2.0最大數據傳輸率傳輸數據。該芯片基于EZ-USB FX芯片開發,集成有發送器、SIE、8051微控制器、存儲器和可編程IO接口,是一種完全集成的USB2.0方案。

1.2 G.723.1簡介

G.723.1是一種低碼率語音壓縮標準,是H.324標準系列的一部分,也是VoIP的常用解決方案之一,可在低比特率通信終端(PSTN和無線網絡)上進行多媒體通信。使用G.723.1標準能夠將8 kHz采樣l6 bit的線性PCM語音信號壓縮成6.3 Kb/s或5.3 Kb/s的比特流,其壓縮比例較高,占用帶寬較低,而且具有很好的音質。

2 硬件設計

2.1 TMS320C6713外設接口HPI

TMS320C6713是一款高性能的32位浮點DSP,適用于專業音頻信號處理。HPI即主機接口,是TMS320C6713片上集成的外設接口之一。通過HPI 可以方便地實現多處理器系統,外部處理器作為主處理器,DSP作為從處理器。通過HPI 接口,外部主機可以訪問DSP除L2控制寄存器、中斷選擇寄存器、仿真邏輯之外的全部存儲器映射空間。

2.2 讀寫時序

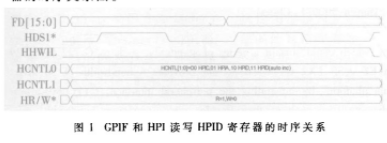

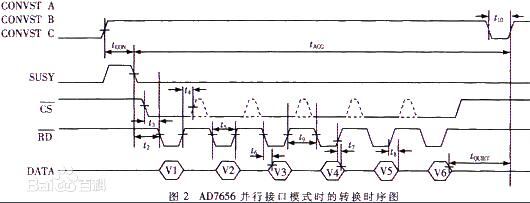

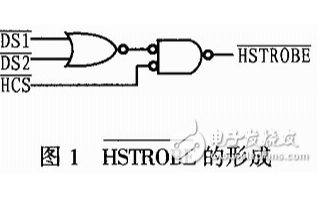

本實驗采用CY7C68013和TMS320C6713芯片。在GPIF接口部分,IFCLK設置為48 MHz內部時鐘,使用16位寬的數據總線(設置WORDWIDE=1),分配CTL[2:0]控制HPI的時序。使用GPIF Tool生成波形描述符,分別用于HPIC/HPIA/HPID的讀寫控制。值得注意的是:由于HDS1*/HDS2*/HCS*相關,可以使HCS*有效,HDS2*置“1”,并通過HDS1*控制選通;HHWIL控制傳輸的是第一半字還是第二半字;HCNTL[1:0]決定哪個寄存器正被訪問。由于采用DIN連接器,其傳輸速率最高可達幾十兆赫茲,這也是其傳輸瓶頸。如果采用手工單獨裝配的SMA硬件連接器,其硬件連接的速度完全可以滿足GPIF和HPI的要求。當然,前者每個引腳的成本不到后者的百分之一。圖1為GPIF和HPI讀寫HPID寄存器的時序關系圖。

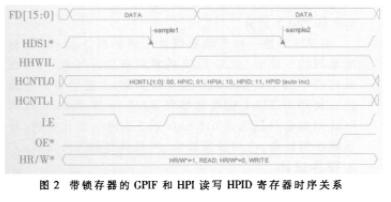

通過FX2固件、利用非GPIF I/O信號引腳可實現更多的信號輸出。使用DM74LS573N鎖存器,采用數據鎖存的辦法可以減小由布局布線等原因帶來的互感、串聯電感、寄生電容等減緩信號傳播的影響,在硬件測試階段能夠有效解決傳輸誤碼的問題。由于74LS573的傳輸延遲,系統的可靠性建立在犧牲系統帶寬的基礎上。改用74LVC16245雙向緩沖器,可以實現GPIF主控的數據讀、寫功能。圖2為帶鎖存器的GPIF和HPI讀寫HPID寄存器的時序關系圖。

2.3 硬件連線

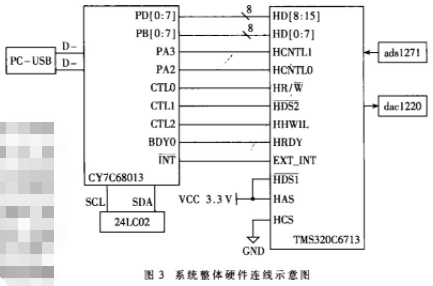

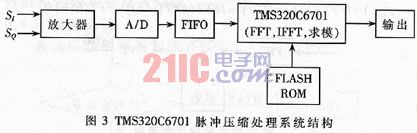

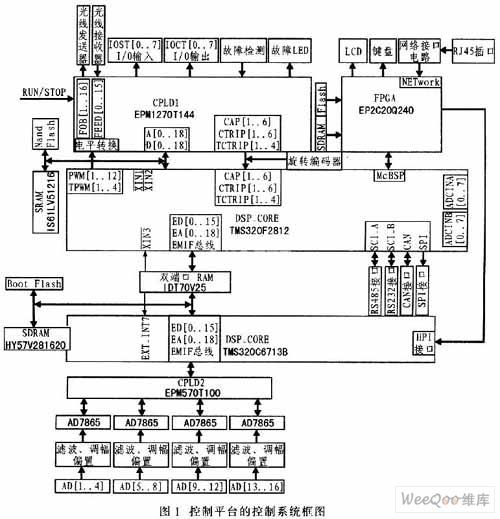

系統整體硬件連線示意圖如圖3。

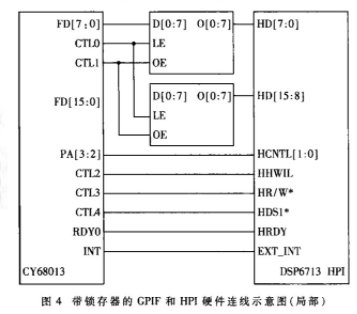

圖4為帶鎖存器的GPIF和HPI硬件連線示意圖。

3 軟件設計

此方案包括4個方面的程序設計:固件程序、驅動程序、主機應用程序和DSP數據處理程序。

3.1 固件程序

固件程序是指運行在CY7C68013 51內核中的程序,主要包括設備描述符信息、設備功能代碼和USB同DSP處理器間的通信控制功能代碼。對于使用GPIF的FX2系統,固件還應能夠分配FIFO讀和寫波形到4個FIFO中的任何一個。

3.1.1 固件程序設計

固件程序開發基于KEIL C51,使用Cypress公司提供的固件函數庫Ezusb.lib和固件框架以提高開發效率。固件函數庫提供了一系列與USB協議有關的函數,固件框架已經實現了初始化、重枚舉、電源管理等功能。

固件程序由以下文件組成:

FX2.h 共同的FX2常數、宏、數據類型以及函 數庫內庫函數的原型框架。

FX2regs.h FX2寄存器的聲明及位屏蔽常數

Fw.c 框架源代碼

Ti6713HPI2cy13.c 用戶函數掛鉤的相關定義

Gpif.c 由GPIF_Designer生成,用以匹配HPIC、HPIA、HPID時序

Dscr.a51 USB 描述符表的范例

Ezusb.lib EZ-USB 函數庫目標代碼

USBJmpTb.OBJ USB中斷向量表和GPIF中斷源

其中Fw.c、Ti6713HPI2cy13.c和Gpif.c是固件程序的核心內容。

在Fw.c中主要包括任務分配器(TD)函數和設備請求(DR)函數。Ti6713HPI2cy13.c中定義這些關鍵函數。Gpif.c由GPIF_Designer生成,本設計將GPIF_Designer的4組波形分別定義為:第一半字寫、第二半字寫、FIFO寫和FIFO讀。其中前兩組波形配合任務分配器函數TD_Poll()完成DSP中寄存器HPIC和HPIA的寫,后兩組波形配合TD_Poll()完成自增模式下HPID的讀寫。波形的設計要嚴格遵守HPI總線訪問時序。

在TD_Init()中設置整體狀態變量的初始值并規定各種端點資源的使用(包含中斷)以及配置外圍接口的輸入輸出。為匹配HPI通信所需數據總線寬度,寄存器EPxFIFOCFG中 WORDWIDE位置1。PORTB配置為FD[7:0],PORTD配置為FD[15:8]。為了達到最大的USB2.0帶寬,設計中將AUTOOUT/AUTOIN位置1。主機與主控制器被直接連接,CPU被旁路,OUT FIFO自動從主機提交到FIFO。

TD_Init()定義中的程序片段:

……

EP2CFG=0xA0; //端點2可用、輸出、數據流、512 B、

//4倍緩沖模式

SYNCDELAY;

EP4CFG=0x00; //端點4不可用

SYNCDELAY;

EP6CFG=0xE0; //端點2可用、輸入、數據流、512 B、4倍緩沖模式

SYNCDELAY;

EP8CFG=0x00; //端點8不可用

SYNCDELAY;

FIFORESET=0x80; //暫不接受主機請求

SYNCDELAY;

FIFORESET=0x02; //將EP2 FIFO恢復為缺省狀態

SYNCDELAY;

FIFORESET=0x06; //將EP6 FIFO恢復為缺省狀態

SYNCDELAY;

FIFORESET=0x00; //重新開放主機請求

SYNCDELAY;

EP2FIFOCFG=0x01; //

SYNCDELAY;

EP2FIFOCFG=0x11; //數據寬度16 bit、AUTOOUT模式

SYNCDELAY;

EP6FIFOCFG=0x09; //數據寬度16 bit、AUTOIN模式

SYNCDELAY;

……

TD_Poll()中最核心部分在于完成寫HPIC寄存器、寫HPIA寄存器、以自增模式讀寫HPID。

(1)寫HPIC寄存器。

EP0BCL=0; //激活EP0緩沖器以接收主機的下一個請求

while(EP01STAT & bmEP0BSY);//等待EP0空閑可用

while(!HPI_RDY); //等待HPI準備好接收數據

IOA=bmHPIC; //PA2、PA3選通HPIC

GPIFWFSELECT=0xB9; //選擇寫入第一個半字的GPIF波形

GPIF_SingleByteWrite(EP0BUF[0],EP0BUF[1]);

//寫入一個16 bit半字

其中GPIF_SingleByteWrite()定義為:

void GPIF_SingleByteWrite(BYTE gdatah,BYTE gdatal)

{

while( !(GPIFTRIG & 0x80) ) {;} //輪詢GPIFTRIG.7

//Done位查看上一次事務是否完成

XGPIFSGLDATLX=gdatal; //高8位寫入XGPIFSGLDATLX

XGPIFSGLDATH=gdatah; //低8位寫入XGPIFSGLDATH

}

對于16位模式,把高8位寫入XGPIFSGLDATLX,低8位寫入XGPIFSGLDATH就可以自動啟動一個單向寫事務。當這個事務完成時,GPIFTRIG.7 Done置1,觸發GPIFdone中斷,68013使XGPIFSGLDATLX和XGPIFSGLDATH中的數據出現在16位數據總線FD[15:0]上。

(2)寫HPIA寄存器。

與寫HPIC基本相同,只是將IOA=bmHPIA,使PA2、PA3選通HPIA。

(3)自增模式下寫HPID。

if(GPIFTRIG & 0x80) //檢查當前GIPF是否空閑

{

if (!(EP24FIFOFLGS & 0x02 ) ) //檢查外圍是否有

//數據等待傳入EP2,EP2非空

{

IOA=bmHPID_AUTO; //PA2、PA3選通自增模式HPID

while(!HPI_RDY); //等待HPI準備好傳輸數據

SYNCDELAY;

GPIFTCB1=EP2FIFOBCH;

SYNCDELAY;

GPIFTCB0=EP2FIFOBCL; //將EP2FIFO中字節數設置為TC的值

SYNCDELAY;

GPIFTRIG=GPIF_EP2; //寫寄存器GPIFTRIG觸發 EP2 OUT事務

SYNCDELAY;

while( !( GPIFTRIG & 0x80 ) ); //等待本次事務處理完畢

SYNCDELAY;

}

}

(4)自增模式下讀HPID。

與自增模式下寫HPID寫過程基本相同。不同點在于:事務計數器的值不是端點6中字節的個數,而是應當由主機方通過控制端點EP0告知FX2;讀EP6前要檢查EP6 FIFO非滿,觸發時將GPIFTRIG設置成EP6IN。

3.1.2 固件代碼的存儲位置

本設計將固件代碼存在主機中,設備上電以后由下面要介紹的驅動程序將固件下載到FX2片內RAM后執行,這一過程也就是重枚舉。這種方法便于系統的調試和升級,用戶可以根據自己的需要將相應驅動下載到PC上,從而使設備呈現出不同的屬性功能,并可以進行適當的軟升級。這種方法對片外EEPROM或ROM的存儲空間要求很低,便于實現,使用靈活。

另外還可以把固件代碼固化到一片EEPROM中,上電后FX2通過I2C總線下載到片內RAM后執行;或者把程序固化到一片ROM中充當外部程序存儲器,連接到FX2總線上。

3.2 設備驅動程序

設備驅動程序提供用戶訪問設備的接口。EZ-USB系列芯片都具有通過下載固件和重枚舉的方式來動態改變設備特性的能力,這就需要一個特殊的具有下載固件并完成設備重枚舉功能的設備驅動程序,也可以叫做固件下載驅動程序。Cypress公司發布的EZ-USB軟件開發包中提供了一個固件下載驅動程序的模版,即EZ-LoaderDriver。通過它可以方便地將自己的固件程序嵌入固件下載驅動程序。主要步驟包括:(1)設定固件下載前后兩次枚舉的不同VID和PID;(2)修改ezloader中source文件的目標名稱;(3)修改Dscr.a51中的VID、PID;(4)利用ezloader提供的工具將用Keil編寫固件所生成的.hex文件轉換成.sys文件;(5)編寫與.sys文件相對應的安裝信息文件(.inf);(6)修改EEPROM,將VID、PID寫入,并設置成C0引導加載模式。

3.3 主機應用程序

為提高開發速度,本設計的主機應用程序在Cypress公司提供的USB Control Pane的基礎上加以修改,增添了讀取存儲和分析音頻文件(主要是.wav文件)的功能。

3.4 DSP數據處理程序

將G.723.1公布的低碼率語音壓縮算法以C與匯編混合編程的方法移植到TMS320C6713,并加以調整優化。

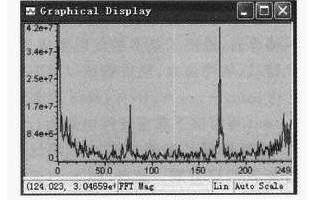

本系統開發旨在為G.723.1以及G.729等常用的低碼率語音壓縮標準提供運行及測試的硬件平臺。DSP系統中的程序采用C與匯編混合編程的方法。實驗表明,USB的數據帶寬完全可以滿足多路音頻數據實時處理的要求,并具有良好的穩定性和適應性,能夠達到所要求的通信質量,實現較為完善的語音編解碼系統。

責任編輯:gt

電子發燒友App

電子發燒友App

評論