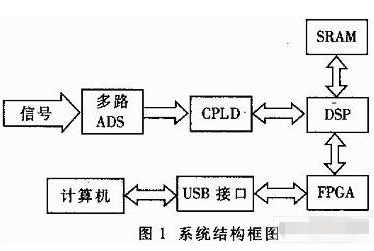

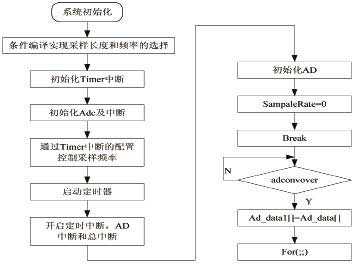

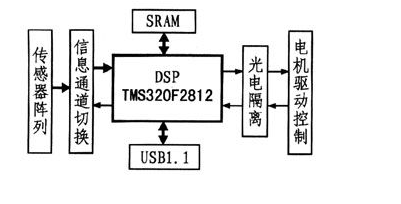

隨著DSP芯片功能越來越強(qiáng),速度越來越快,性價(jià)比的不斷提高以及開發(fā)工具的日趨完善,廣泛用于通信、雷達(dá)、聲納、遙感、生物醫(yī)學(xué)、機(jī)器人、控制、精密機(jī)械、語音和圖像處理等領(lǐng)域。作為計(jì)算機(jī)接口之一的USB(Universal Serial Bus)口具有勢插拔、速度快(包括低、中、高模式)和外設(shè)容量大(理論上可掛接127個(gè)設(shè)備)的特性,使其成為PC機(jī)的外圍設(shè)備擴(kuò)展中應(yīng)用日益廣泛的接口標(biāo)準(zhǔn)。本文設(shè)計(jì)并實(shí)現(xiàn)了基于DSP的USB口數(shù)據(jù)采集分析系統(tǒng),該系統(tǒng)的DSP負(fù)責(zé)數(shù)據(jù)的采集和運(yùn)算處理,處理結(jié)果通過USB口送計(jì)算機(jī)顯示分析,其結(jié)構(gòu)如圖1所示。

該結(jié)構(gòu)圖中,CPLD和FPGA實(shí)現(xiàn)模塊接口,包括串并轉(zhuǎn)換、8位和32位數(shù)據(jù)總線間的轉(zhuǎn)換、SRAM等功能。采樣結(jié)果經(jīng)過CPLD送至DSP運(yùn)算處理(FFT變換、相關(guān)分析、功率譜分析等)后,由FPGA和USB接口送至主控計(jì)算機(jī)存儲(chǔ)和顯示。計(jì)算機(jī)應(yīng)用程序易于實(shí)現(xiàn)豐富的圖形界面,具有良好的人機(jī)接口。

1 模數(shù)模塊

本系統(tǒng)主要用于振動(dòng)信號(hào)和噪聲分析,要求采樣精度高,采樣頻率不超過100kHz。根據(jù)要求選用CRYSTAL公司的CS5396。該芯片原本用于立體聲采樣,基于∑-Δ結(jié)構(gòu),采樣精度高,24位分辨率,120dB的動(dòng)態(tài)范圍;采樣頻率32kHz、44.1kHz、48kHz、96kHz可選;內(nèi)部集成采樣保持器、模擬低通濾波器、數(shù)字濾波器,同時(shí)還具有時(shí)采樣功能;兩路同時(shí)采樣,串行輸出,串行數(shù)據(jù)由CPLD轉(zhuǎn)換成24位并行數(shù)據(jù);由于該芯片量程是4V,差分輸入,所以模擬部分只需再加上簡單量程放大電路即可。這樣模擬電路十分簡單,抗干擾能力強(qiáng)、精度高。

2 DSP處理器

選擇DSP處理器時(shí)主要考慮其運(yùn)算速度、總線寬度和性價(jià)比。本系統(tǒng)采樣結(jié)構(gòu)24位,最好選用32位DSP;系統(tǒng)要進(jìn)行實(shí)時(shí)信號(hào)分析、模態(tài)分析等,要求有較高運(yùn)算速度,所以選用TI公司的32位浮點(diǎn)DSP——TMS320VC33。該芯片采用哈佛結(jié)構(gòu),6級(jí)流水線操作,指令執(zhí)行周期7ns,外設(shè)包括一個(gè)DMA控制器和一個(gè)緩沖串口。

N點(diǎn)復(fù)數(shù)FFT變換約做2N×Log2N次實(shí)數(shù)乘法運(yùn)算和3N×Log2N實(shí)時(shí)加法運(yùn)算。TMS320VC33的乘法、加法都是單周期指令,取N=1024,不計(jì)內(nèi)存訪問和其它時(shí)間,則一次FFT所需時(shí)間為:10×5120×17ns約0.9ms。而按96KSPS的采樣頻率計(jì)算,1024點(diǎn)的采樣時(shí)間約10ms,可見該DSP速度足以滿足要求。

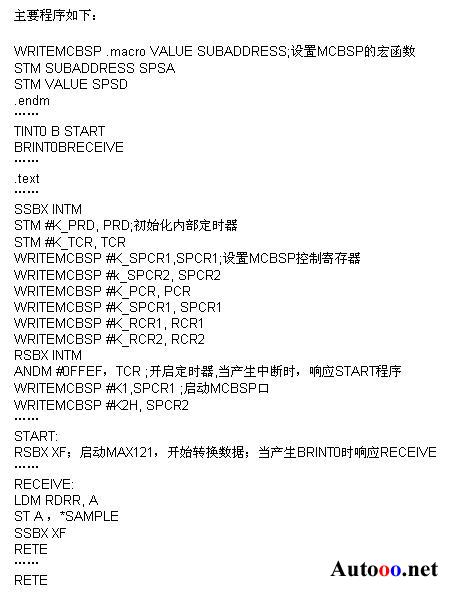

該DSP啟動(dòng)模式可選,上電后執(zhí)行駐留在低地址空間的BOOTLOADER;然后根據(jù)4個(gè)中斷輸入信號(hào)的狀態(tài)判斷啟動(dòng)模式,可以從RAM、ROM或串行口啟動(dòng)。本系統(tǒng)選擇串行口方式。這樣,DSP程序可以直接從PC下載送至DSP接口,做到在系統(tǒng)調(diào)試,具有極大的靈活性。

3 USB接口

USB協(xié)議的實(shí)現(xiàn)基于網(wǎng)絡(luò)的思想,是一種共享式的總線,在總線上數(shù)據(jù)以包(Packet)的形式發(fā)送。USB的數(shù)據(jù)傳送有4種模式:塊傳輸(Bulk Transfers)、中斷傳輸(Interrupt Transfers)、同步傳輸(Isochronous Transfers)、控制傳輸(Control Transfers)。當(dāng)需要快速傳輸大批量的準(zhǔn)確數(shù)據(jù)時(shí),一般采用塊傳輸模式;當(dāng)傳輸實(shí)時(shí)性較強(qiáng)的數(shù)據(jù)時(shí),采用中斷傳輸模式。

當(dāng)USB設(shè)備插入計(jì)算機(jī)時(shí),計(jì)算機(jī)和USB設(shè)備之間產(chǎn)生一個(gè)枚舉過程。計(jì)算機(jī)檢測到有設(shè)備插入,自動(dòng)發(fā)出查詢請求;USB設(shè)備回應(yīng)這個(gè)請求,送出設(shè)備的Verdor ID和Product ID;計(jì)算機(jī)根據(jù)這兩個(gè)ID裝載相應(yīng)的設(shè)備驅(qū)動(dòng)程序,完成枚舉過程。

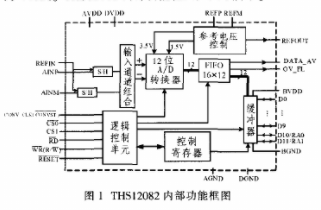

由于USB協(xié)議非常復(fù)雜,開發(fā)者不可能在底層基礎(chǔ)上進(jìn)行開發(fā)。目前,市場上對(duì)USB協(xié)議進(jìn)行封裝的接口芯片,如:National Semiconductor公司的USBN9602、Plilips公司的PDIUSBD12等。本系統(tǒng)選用CYPRESS公司的帶單片機(jī)內(nèi)核的EZ-USB系列的AN2131QC.該芯片遵從USB1.0規(guī)范(12Mbps),將8051單片機(jī)內(nèi)核、智能USB接口引擎、USB收發(fā)模塊、存儲(chǔ)器、串行口等集成一起,從而減少芯片接口時(shí)序。其內(nèi)部結(jié)構(gòu)如圖2(虛線內(nèi)是芯片部分)。

EZ-USB的8051代碼(Firmware)可以固化在ROM內(nèi);更好的方案是通過USB口從主機(jī)下載到內(nèi)部RAM,這樣,易于修改、調(diào)試和更新。之所以能下載代碼是因?yàn)樾酒簧想娡耆?a target="_blank">硬件上自動(dòng)完成枚舉過程,不需要Firmware。完成枚舉后便可作為一個(gè)USB設(shè)備(叫做缺省USB設(shè)備)與計(jì)算機(jī)通訊,此時(shí)即可進(jìn)行Firmware下載。下載完后,8051內(nèi)核脫離RESET狀態(tài)開始執(zhí)行代碼。可以通過Firmware對(duì)USB設(shè)備重新配置,這個(gè)重新配置過程叫做再枚舉。

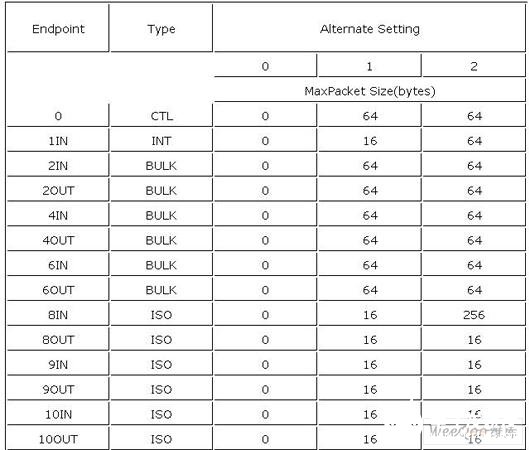

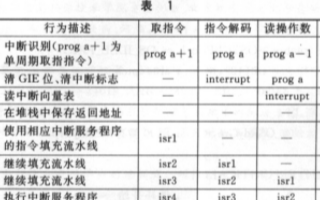

在EZ-USB中,缺省USB設(shè)備的接口中包括14個(gè)Endpoints,如表1所示。

表1 缺省USB端點(diǎn)(Endpoint)

計(jì)算機(jī)與USB設(shè)備的數(shù)據(jù)通信主要包括兩個(gè)方面:一是讀取采樣數(shù)據(jù);二是給USB設(shè)備發(fā)送控制命令。發(fā)送控制命令先發(fā)送一個(gè)命令包(消息),然后根據(jù)情況發(fā)送后續(xù)數(shù)據(jù)或從設(shè)備讀取響應(yīng)數(shù)據(jù)。因此,根據(jù)EZ-USB芯片的功能,直接使用缺省配置中的6個(gè)Endpoint。

Endpoit OUT2 BULK:用來發(fā)送控制命令包。

Endpoint IN2 BULK:接收從USB設(shè)備發(fā)來的DSP消息。

Endpoint IN4 BULK:用來從USB設(shè)備讀取數(shù)據(jù),如讀取采樣數(shù)據(jù)、配置參數(shù)等。

Endpoint OUT4 BULK:用來向USB設(shè)備發(fā)送數(shù)據(jù),如下載8051程序、下載FPGA程序等。

Endpoint OUT6 BULK:作輔助判斷用,當(dāng)PC傳送完大量數(shù)據(jù)至USB設(shè)備時(shí),向該端口寫任意數(shù)據(jù)以起到通知USB設(shè)備的作用。

Endpoint IN1 INT:用來從USB設(shè)備讀取響應(yīng)信號(hào),如下載FPGA程序是否成功的標(biāo)志等。

在缺省配置基礎(chǔ)上可以編寫適合需要的代碼,如果對(duì)8051編程經(jīng)驗(yàn)豐的話,完全可以在不需要調(diào)試工具的情況下編寫Firmware。

本系統(tǒng)Firmware結(jié)構(gòu)建立在對(duì)消息隊(duì)列不斷服務(wù)基礎(chǔ)上,即構(gòu)建一個(gè)消息隊(duì)列,當(dāng)接收到任何一方(DSP或計(jì)算機(jī))的消息時(shí),將其放入消息隊(duì)列。消息的接收是通過中斷服務(wù)程序來實(shí)現(xiàn)的。當(dāng)處理完一個(gè)消息時(shí),從消息隊(duì)列取出下一個(gè)消息進(jìn)行處理。這種軟件結(jié)構(gòu)非常簡單,思路清晰,對(duì)調(diào)試十分有利。

USB設(shè)備驅(qū)動(dòng)程序基于WDM。WDM型驅(qū)動(dòng)程序是內(nèi)核程序,與標(biāo)準(zhǔn)的Win32用戶態(tài)程序不同。采用了分層處理的方法。通過它,用戶不需要直接與硬件打它道(在USB驅(qū)動(dòng)程序中尤為明顯),只需通過下層驅(qū)動(dòng)程序提供的接口號(hào)訪問硬件。因此,USB設(shè)備驅(qū)動(dòng)程序不必具體對(duì)硬件編程,所有的USB命令、讀寫操作通過總線驅(qū)動(dòng)程序轉(zhuǎn)給USB設(shè)備。但是,USB設(shè)備驅(qū)動(dòng)程序必須定義與外部設(shè)備的通訊接口和通訊的數(shù)據(jù)格式,也必須定義與應(yīng)用程序的接口。

本系統(tǒng)的驅(qū)動(dòng)程序是在Compuware Numega Driver-Works的基礎(chǔ)上采用面向?qū)ο笳Z言C++開發(fā)的。Driver-Works可以很快構(gòu)造出驅(qū)動(dòng)程序的框架。主要構(gòu)造了兩個(gè)類:Class USBDAC和class USBDACDevice。Class USBDAC繼承了class Kdriver,負(fù)責(zé)裝載驅(qū)動(dòng)程序和創(chuàng)建功能設(shè)備對(duì)象時(shí)要做的一些操作。Class USBDACDevice繼承了class KpnpDevice,是驅(qū)動(dòng)程序的主要部分,負(fù)責(zé)設(shè)備啟動(dòng)、停止的操作以及與設(shè)備的數(shù)據(jù)通訊。API函數(shù)調(diào)用和CreateFile ()、ReadFile ()、WriteFile ()、DeviceIO-Control ()、CloseFile()等的實(shí)現(xiàn)也在class USBDACDevice中完成。

Class USBDAC的定義如下:

class USBDAC : public Kdriver

{

SAFE_DESTRUCTORS

public:

/*Driver Entry (),

在系統(tǒng)引導(dǎo)或I/O管理器裝入驅(qū)動(dòng)程序時(shí),調(diào)用這個(gè)例程。執(zhí)行大量的初始化函數(shù),包括建立到其它驅(qū)動(dòng)程序的指針、查找和定位由驅(qū)動(dòng)程序使用的任何硬件資源等,不過,這部分工作大多由基類Kdriver完成。*/

virtual NTSTATUS DriverEntry(PUNICODE_STRING RegistryPath);

/*AddDevice(),創(chuàng)建一個(gè)Device對(duì)象。調(diào)用其構(gòu)造函數(shù)對(duì)設(shè)備初始化,創(chuàng)建設(shè)備的名稱等。*/

virtual NTSTATUS AddDevice(PDEVICE_OBJECT Pdo);

Int m_Unit;

};

Class USBDACDevice的定義如下:

Class USBDACDevice : public KpnpDevice

{

// Constructors

public:

SAFE_DESTRUCTORS

USBDACDevice(PDEVICE_OBJECT Pdo,ULONG Unit);

~USBDACDevice ();

// Member Functions

public:

…

//添加自己的成員函數(shù)

NTSTATUS USBDAC_GetACK(int &);

NTSTATUS USBDAC_StartADConversion(void);

NTSTATUS USBDAC_StopADConversion(void);

NTSTATUS USBDAC_DownloadFPGA(KIrp);

NTSTATUS USBDAC_Download8051(KIrp);

NTSTATUS USBDAC_SetChannelParameter(PUCHAR,ULONG,int);

…

};

4 FPGA

FPGA模塊主要實(shí)現(xiàn)單片機(jī)與DSP間的數(shù)據(jù)緩沖、8位數(shù)據(jù)線與32位數(shù)據(jù)線間的轉(zhuǎn)換、單片機(jī)同步串口和DSP緩沖串口的切換。要求FPGA能實(shí)現(xiàn)豐富的內(nèi)部RAM和準(zhǔn)確的時(shí)鐘控制。根據(jù)需要選用XILINX公司的XCV50TQ144。該器件采用SRAM 查找表結(jié)構(gòu),具有系統(tǒng)內(nèi)可再編程(ISP)和運(yùn)行間可再配置等特性。系統(tǒng)初始化時(shí)由USB口下載FPGA程序,通過單片機(jī)串口對(duì)其進(jìn)行線配置。

本系統(tǒng)可廣泛用于振動(dòng)、噪聲測試分析。可以在WINDOWS95/98/NT下開發(fā)各類動(dòng)態(tài)測試與信號(hào)處理的應(yīng)用程序,根據(jù)需要加載已經(jīng)編制的各種DSP算法,使其具有信號(hào)分析、模態(tài)分析、聲學(xué)分析、環(huán)境測試、長時(shí)間記錄等功能。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論