譯者? 君謙? 在此特別鳴謝!

本文摘自《開源處理器內部—RISC-V簡介》一書,其經過格式化和輕編輯,內容和頁面布局達到Elektor期刊的標準。FPGA技術與(V)HDL的結合在電子專家中很受歡迎,RISC-V為專業應用增加了開源途徑。在本文中,我們測試了一些在Elektor的“Alchitry”系列的Lattice和 Xilinx FPGA板上運行的示例應用程序的并行比較以及結果。

過去,在 FPGA工具流中設置項目是一項艱巨的任務。隨著技術趨于成熟,這種設置變得簡單許多。在這里的例子中大部分工作已經完成。值得注意的是,大型項目或最大限度利用FPGA功能的項目不可避免地會變得復雜得多。

具體到Lattice和 Xilinx,除了為項目選擇合適的FPGA目標之外,只需要在工具中鏈接到3個文件。在這種簡化的方法中,所有的項目文件都需要在同一個目錄中。建議讀者閱讀FPGA的Alchitry教程軟件安裝和項目設置,這里僅僅涉及基本的細節。

1??Lattice( Alchitry Cu)注意事項 ? ?

該開發板使用的FPGA需要 Lattice iCEcube2軟件。這是一款成熟的產品,沒有太多花哨的功能,但有幾點需要注意:

①?確保使用正確的設備選項設置項目。Alchitry Cu使用CB132封裝中的 iCE4O系列HX8K器件,所有I/O組都使用3.3V電源。

②?只有yrv_alchitry.v文件需要作為設計文件輸入,因為所有其他設計文件將自動以正確的順序包含在內。

③?對于合成工具﹐需確保選擇Lattice LSE合成。邏輯綜合期間不需要約束文件。

④綜合完成后,在運行其余工具之前,yrv_ alchitry.pc/pin約束文件和 timing. sdc時序約束文件需要被鏈接。各種日志文件中會有許多警告,但是它們都沒有重要到需要采取任何措施。

2??Xilinx ( Alchitry Au和Au+)注意事項 ? ?

在這些開發板上使用的FPGA需要Xilinx Vivado軟件。這是一個非常復雜的產品,本項目僅使用這個軟件的一小部分功能。這里有一些要記住的事情:

①?只有yrv_alchitry.v文件需要作為設計文件輸入。

②?只有yrv_alchitry.mdc約束文件是必需的。該文件包含引腳約束、時序約束以及編程電壓規格。

③?正確的器件選項是用于Au板的xc7a35tftg256 -i和用于Au+板的xc7aiootftgzS6 -i。

在這些設備的日志文件中有更多的警告﹐同樣,它們都沒有重要到需要采取任何措施。

3??FPGA結果 ? ?

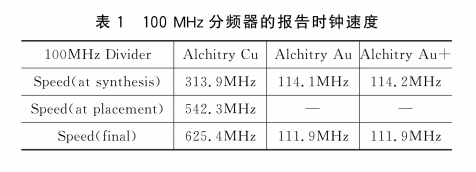

該示例項目已在所有3種目標FPGA開發板上實施,具體結果將在以下部分介紹。在對一些結果進行并列比較時是很有趣的。表1顯示了100 MHz分頻器的報告時鐘速度。

100 MHz分頻器設計用于最大速度,觸發器之間只有一級邏輯,這意味著這個結果應該代表技術的能力。如果報道屬實﹐點陣設備的速度令人印象深刻。最有趣的是,隨著邏輯綜合到邏輯布局再到最終布線結果,報告的速度變得更快,而且可能更準確。雖然最終的性能比最初的預期值要好,但是相差兩倍是不理想的,因為這可能導致錯誤地將其作為一個不可行的項目而放棄。

Xilinx工具不會在邏輯布局時給出單獨的速度估計,但邏輯綜合和最終結果之間報告的速度幾乎相同。從設計師的角度來看,這是首選。

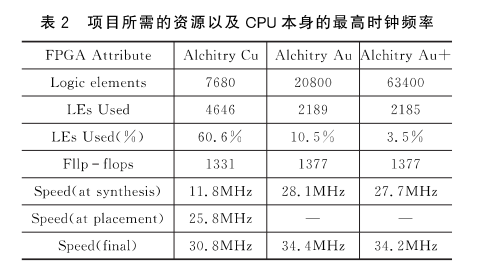

表2顯示了項目所需的資源以及CPU本身的最大時鐘頻率。這些結果不包括RISC-V特權架構中的任何64位計數器。

表2的第二行說明了為什么比較FPGA結果會很復雜。從表中可以看出,Xilinx實現所需的資源不到1attice實現所需資源的一半﹐但是Xilinx邏輯無件包含的邏輯比點陣邏輯元件多得多。此外,Xilinx設計使用了 Lattice設備所沒有的專用DSP模塊。

查看所用邏輯元件的百分比,可以發現3種FPGA之間的尺寸差異。yrv_mcu設計需要一半多一點的 Lattice器件,是大約1/10的中端Xilinx器件,不到大型Xilinx 的1/20。這種用法符合不同開發板的成本要求。

正如預期的那樣,設計所需的觸發器數量在3種FPGA中是相似的,確切地說,數量更多的是邏輯綜合工具的功能而不是其他。邏輯綜合工具將復制觸發器以提高性能或簡化布線。

速度行顯示3種 FPGA提供大致相同的性能,這有點令人驚訝,因為Lattice FPGA 不包含Xilinx實施中使用的專用DSP模塊。

4??關于Alchitry Cu ? ?

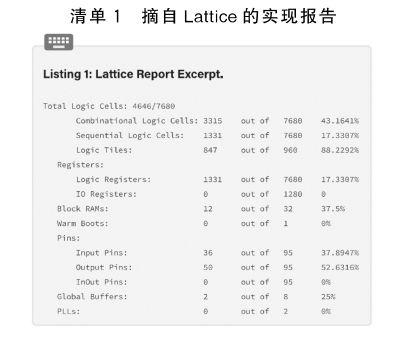

清單1直接摘自 Lattice 的實現報告,顯示了資源利用的細節。圖1取自Lattice Floorplanner工具的屏幕截圖﹐顯示了分布在器件中的邏輯元件的使用情況。這種分布在整個設備中相當均勻,盡管總體使用率只有60%左右。

5? 關于Alchitry Au ? ?

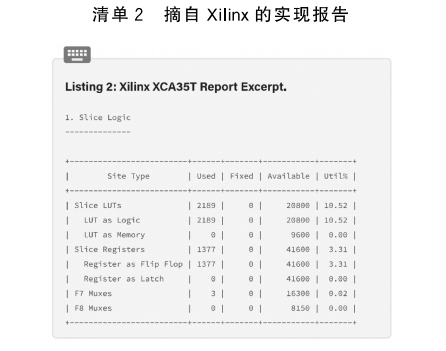

清單2直接摘自Xilinx實現報告,顯示了資源利用的細節。完整的Xilinx報告要大得多,涵蓋了FPGA中所有可用的專用硬件。

圖2為Xilinx Floorplanner 工具的屏幕截圖,顯示了分布在整個器件中的邏輯元件的使用情況,以及專用邏輯模塊如何分布在整個器件中。放置工具似乎總是從設備的左下角開始。

6? 關于Alchitry Au+ ? ?

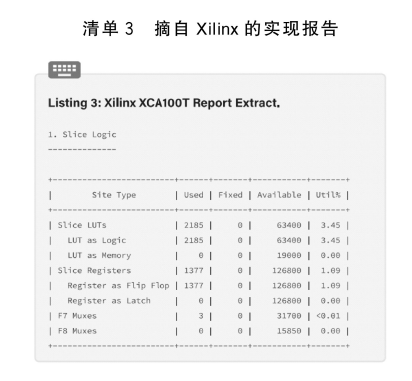

清單3也直接摘自Xilinx的實現報告﹐顯示了資源利用的細節。請注意,兩臺Xilinx設備使用的資源數量幾乎相同。圖3也取自Xilinx Floorplanner工具的屏幕截圖。有趣的是,盡管該FPGA包含3倍數量的邏輯元件,但本例所需的總面積與第一個 Xilinx實施中幾乎相同。

7? 硬件編程 ? ?

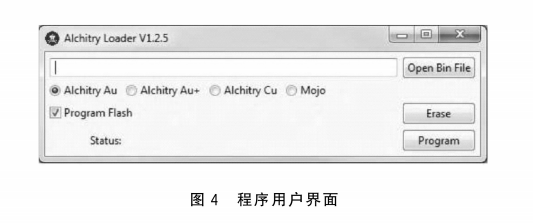

使用Alchitry Loader 程序時,將 FPGA 比特流下載到Alchitry開發板非常簡單。該獨立程序作為Alchitry的一部分,自動安裝Alchitry提供的實驗室軟件。圖4顯示了這個程序的用戶界面。

對用于加載FPGA的開發板上的閃存器件進行編程也很簡單,只需指定位流文件、選擇目標板,然后單擊“編程”按鈕。

默認情況下,程序會查找.bin類型的比特流文件,這是iCEcube2軟件使用的默認設置。Vivado 軟件生成. bit類型的比特流文件。因此,在加載Xilinx 比特流文件時要記住這一點。

編輯:黃飛

電子發燒友App

電子發燒友App

評論