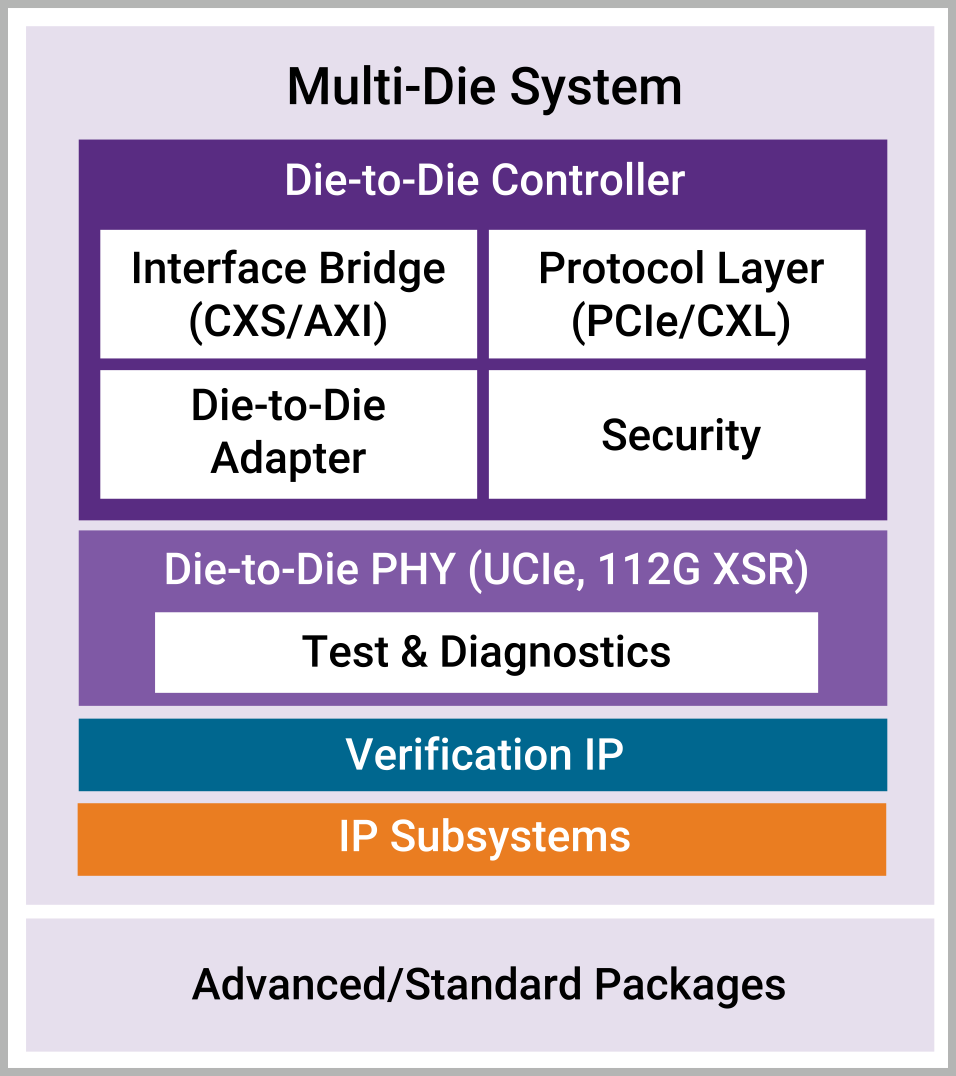

針對(duì)Chiplet技術(shù),去年英特爾、日月光半導(dǎo)體(ASE)、AMD、Arm、谷歌云、Meta、微軟、高通、三星和臺(tái)積電為了統(tǒng)一相關(guān)的技術(shù)標(biāo)準(zhǔn)組建了UCIe(通用芯粒高速互連)聯(lián)盟。該聯(lián)盟推出的UCIe標(biāo)準(zhǔn)對(duì)封裝內(nèi)芯粒(Chiplet)之間的互連進(jìn)行了規(guī)范和約束,以實(shí)現(xiàn)封裝層級(jí)的開(kāi)放芯粒生態(tài)系統(tǒng)和普遍的互連。 其中UCIe聯(lián)盟成員共分為三個(gè)級(jí)別分別是發(fā)起人、貢獻(xiàn)者、采用者。發(fā)起人由董事會(huì)組成并具有領(lǐng)導(dǎo)作用,貢獻(xiàn)者和發(fā)起者公司可以參與工作組,而采用者只能看到最終規(guī)范并獲得知識(shí)產(chǎn)權(quán)保護(hù)。 目前UCIe聯(lián)盟已經(jīng)擁有了超過(guò)100名成員,阿里巴巴、芯耀輝、芯動(dòng)科技、芯云凌、長(zhǎng)鑫存儲(chǔ)、長(zhǎng)電科技等多家國(guó)內(nèi)企業(yè)也加入了該聯(lián)盟,***正式進(jìn)入到了Chiplet時(shí)代。那么Chiplet能否成為***彎道超車的希望? ?

01?“***”

說(shuō)起***彎道超車,我想起了最近的一個(gè)新聞。

?

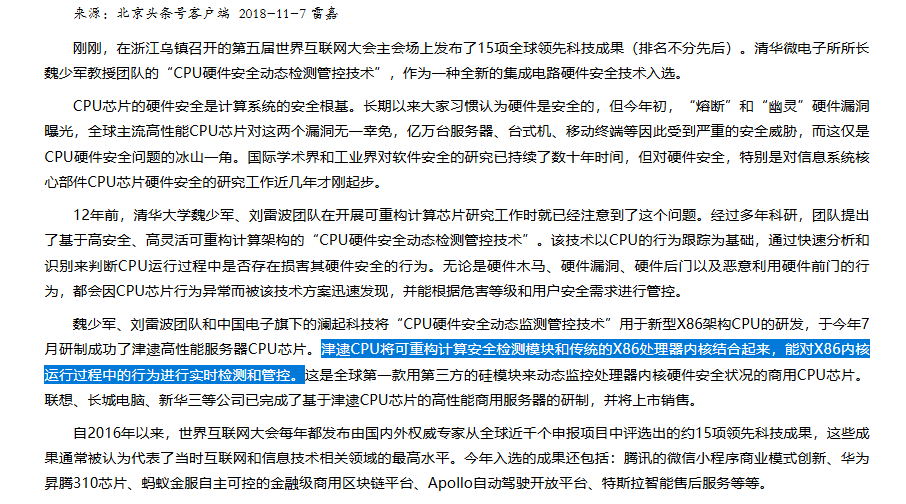

今年1月12日,瀾起科技發(fā)布了第四代津逮CPU。隨后有一些分析文章認(rèn)為國(guó)產(chǎn)處理器追上了英特爾x86處理器。如果單看這個(gè)新聞可能有些人會(huì)認(rèn)為我們的***或者說(shuō)國(guó)產(chǎn)CPU“達(dá)到了國(guó)際先進(jìn)水平”。但是這其中有很多事情是需要說(shuō)明的。瀾起科技官方是這樣描述第四代津逮CPU的: “瀾起科技第四代津逮CPU,以英特爾第四代至強(qiáng)可擴(kuò)展處理器(代號(hào):Sapphire Rapids)為內(nèi)核,通過(guò)了瀾起科技安全預(yù)檢測(cè)(PrC)測(cè)試,是面向本土市場(chǎng)的x86架構(gòu)服務(wù)器處理器。相較上一代產(chǎn)品,第四代津逮CPU采用先進(jìn)的Intel 7制程工藝,其最大核心數(shù)為48核,最高睿頻頻率為4.2GHz,最大共享緩存為105MB,關(guān)鍵性能指標(biāo)大幅提升。” 可能有些讀者不太理解“以英特爾處理器為內(nèi)核,通過(guò)了PrC測(cè)試”是什么意思。這里我們可以結(jié)合清華大學(xué)官網(wǎng)上的一篇文章一起分析一下。

這篇文章中指出“津逮CPU將可重構(gòu)計(jì)算安全檢測(cè)模塊和傳統(tǒng)的X86處理器內(nèi)核結(jié)合起來(lái),能對(duì)X86內(nèi)核運(yùn)行過(guò)程中的行為進(jìn)行實(shí)時(shí)檢測(cè)和管控。”

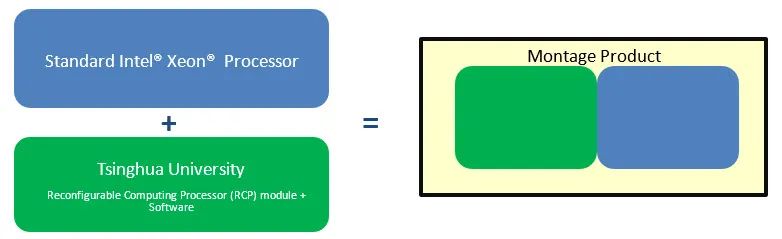

圖片來(lái)源:英特爾 也就是說(shuō)第四代津逮CPU可以分成兩個(gè)部分,一部分是安全模塊,另一部分是英特爾X86處理器內(nèi)核。

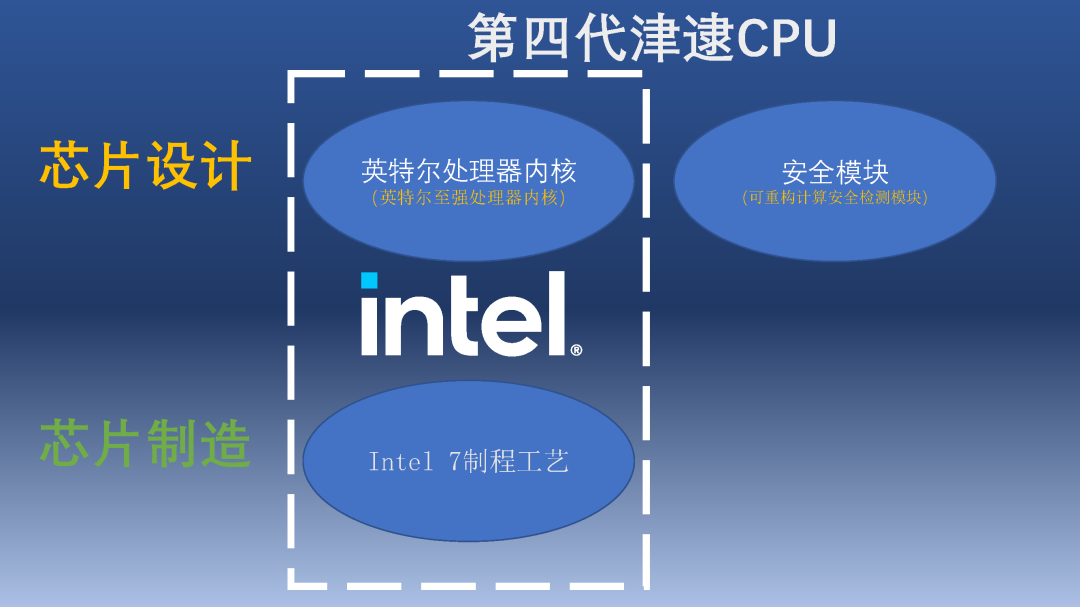

而在性能方面,瀾起科技官方宣傳中有這樣的描述“津逮CPU基于英特爾至強(qiáng)處理器內(nèi)核,其功能、性能及可靠性與至強(qiáng)處理器一致”。所以四代津逮CPU追上了英特爾x86處理器或者說(shuō)達(dá)到了國(guó)際領(lǐng)先水平是沒(méi)問(wèn)題的。只是這種說(shuō)法有些奇怪,畢竟津逮CPU的性能部分來(lái)自于英特爾處理器內(nèi)核。也就是說(shuō):英特爾處理器內(nèi)核在性能方面追趕上了英特爾處理器。 另外一個(gè)問(wèn)題就是第四代津逮CPU算不算***了。目前國(guó)內(nèi)“造芯片”可以分成大致兩種: 一種是字面意義上的制造芯片,擁有晶圓廠,可以直接生產(chǎn)芯片。 另一種是指像海思那樣的Fabless公司,只負(fù)責(zé)設(shè)計(jì)芯片,制造部分交給臺(tái)積電等晶圓廠進(jìn)行。這種設(shè)計(jì)芯片的公司在一些情況下也可以算是“造”芯片。

具體到第四代津逮CPU呢?芯片的安全模塊是由中國(guó)公司設(shè)計(jì)的,英特爾處理器內(nèi)核是由英特爾設(shè)計(jì)的。整個(gè)芯片最終是由Intel 7制程工藝制造的。至于第四代津逮CPU到底算不算***,相信不同的讀者會(huì)有自己的見(jiàn)解。 那么假設(shè)我們將“第四代津逮CPU”認(rèn)定為“***”,那么會(huì)是什么情況呢? 2023年1月,英特爾正式發(fā)布第四代至強(qiáng)可擴(kuò)展處理器(代號(hào):Sapphire Rapids),而就在同一月,某***廠商發(fā)布了具備“同等性能、功能及可靠性”的“***”。國(guó)產(chǎn)CPU完全追上國(guó)際大廠水平,***完成了彎道超車。如果作為一篇“沸騰文章”寫到這里其實(shí)就足夠了,如果是一篇“技術(shù)分析文章”往往會(huì)在這之后告訴你,這個(gè)所謂的“國(guó)產(chǎn)CPU”里面哪些是國(guó)產(chǎn)的,哪些又是進(jìn)口的。但是從另一個(gè)角度看,這樣的商業(yè)合作確實(shí)為***的發(fā)展打開(kāi)了思路。就比如說(shuō)今天我們?cè)趪?guó)外原有CPU的基礎(chǔ)上加進(jìn)去了一個(gè)安全模塊,明天我們可以加入另一個(gè)模塊。并且我們可以逐漸替換芯片中的非國(guó)產(chǎn)部分,這樣一來(lái)總有一天我們能造出完整的***。 而Chiplet技術(shù)恰好可以實(shí)現(xiàn)這種發(fā)展方式,Chiplet技術(shù)的出現(xiàn)允許我們?cè)凇霸煨酒钡臅r(shí)候由淺入深地提高芯片內(nèi)部使用的“國(guó)產(chǎn)成分”比例。 ?

02?Chiplet

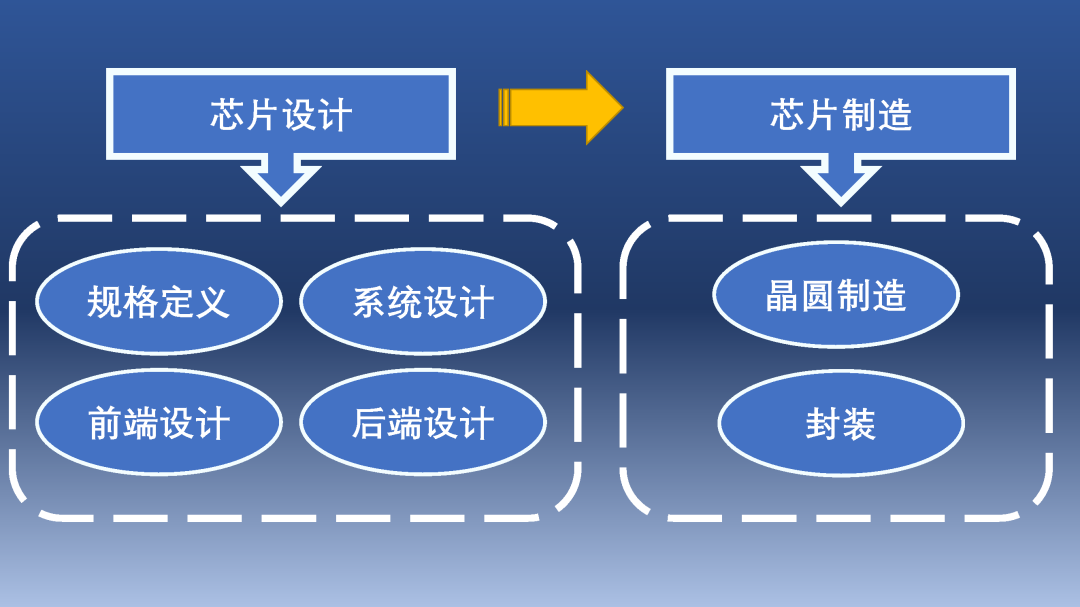

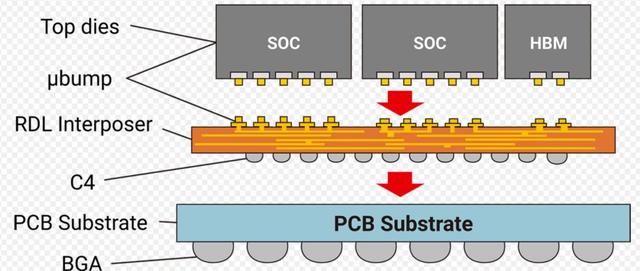

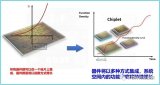

目前不同廠商對(duì)于Chiplet都有自己的定義和解釋,但大致可以分為兩種: 1、Chiplet就是把多個(gè)芯片(2個(gè)或2個(gè)以上)通過(guò)封裝的方式“整”到一個(gè)芯片中。 2、Chiplet就是把多個(gè)芯片(2個(gè)或2個(gè)以上)通過(guò)先進(jìn)封裝的方式“整”到一個(gè)芯片中。 第一種定義其實(shí)和“合封芯片”相同,多個(gè)芯片封裝到一起就算,第二種定義強(qiáng)調(diào)了封裝方式必須是“先進(jìn)封裝”才算,例如2.5D封裝、3D封裝。 一款Chiplet芯片的設(shè)計(jì)制造流程可以大致分成兩個(gè)階段,第一個(gè)階段主要是制造出芯片的Die(裸片),第二個(gè)階段是將多個(gè)Die(裸片)進(jìn)行封裝。 (以下對(duì)于設(shè)計(jì)制造流程的描述只是進(jìn)行粗略的大致描述,且描述過(guò)程中可能會(huì)以數(shù)字邏輯芯片的設(shè)計(jì)制造流程為主,模擬芯片、存儲(chǔ)芯片等其它芯片的相關(guān)流程可能不盡相同。) 第一階段——從圖紙到Die: 1、規(guī)格定義:我們準(zhǔn)備要搞一個(gè)芯片了。這個(gè)芯片干什么用的?需要實(shí)現(xiàn)哪些功能?性能要達(dá)到什么程度?成本控制在什么水平?例如這些是這個(gè)階段要確定下來(lái)的問(wèn)題,或者簡(jiǎn)單來(lái)說(shuō)就是要明確芯片的用途、性能、規(guī)格、成本等指標(biāo)。 2、系統(tǒng)設(shè)計(jì):基于前期規(guī)劃那些指標(biāo),這個(gè)階段要明確芯片架構(gòu),確定芯片中都包含哪些模塊,并且設(shè)計(jì)好它們之間的連接關(guān)系、交互關(guān)系。 3、前端設(shè)計(jì):基于前面的那些工作,這一步將針對(duì)各模塊開(kāi)展具體的電路設(shè)計(jì)。將會(huì)使用硬件描述語(yǔ)言(Verilog或VHDL),對(duì)具體的電路實(shí)現(xiàn)進(jìn)行RTL(Register Transfer Level)級(jí)別的代碼描述。之后用邏輯綜合工具,把硬件描述語(yǔ)言寫成的RTL級(jí)的代碼轉(zhuǎn)成門級(jí)網(wǎng)表(NetList)。邏輯綜合完成后需要進(jìn)行靜態(tài)時(shí)序分析,需要確保電路在面積、時(shí)序等目標(biāo)參數(shù)上達(dá)到預(yù)設(shè)的標(biāo)準(zhǔn)。 在完成前端設(shè)計(jì)中每一個(gè)小步驟時(shí)基本都需要經(jīng)過(guò)仿真驗(yàn)證來(lái)檢驗(yàn)相關(guān)設(shè)計(jì)的正確性。仿真驗(yàn)證如果通過(guò)不了,那可能就需要修改設(shè)計(jì)甚至重新設(shè)計(jì)。 4、后端設(shè)計(jì):基于前面的那些工作,并且結(jié)合晶圓廠提供的工藝文件,最終生成用于芯片生產(chǎn)的GDS(Geometry Data Standard)版圖。同樣在這個(gè)階段也需要進(jìn)行多次仿真驗(yàn)證。 5、芯片制造/從沙子到Die(裸片):從這個(gè)步驟開(kāi)始,主要就是晶圓廠的工作了。這個(gè)步驟大致包括制造晶棒、生產(chǎn)晶圓、對(duì)晶圓進(jìn)行一系列處理(比如薄膜工藝;光刻、刻蝕、去膠等圖形化工藝;摻雜工藝;熱處理工藝),完成這些之后,需要測(cè)試完成處理的晶圓。

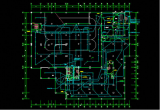

舉個(gè)例子來(lái)說(shuō),這是一塊英特爾至強(qiáng)處理器的晶圓,經(jīng)過(guò)處理后的晶圓大概就是這個(gè)樣子。我們可以看到這塊晶圓上有無(wú)數(shù)個(gè)小的方形塊。經(jīng)過(guò)測(cè)試之后會(huì)將這些小的方形塊從晶圓上切下來(lái),切下來(lái)的小方形塊就是芯片的Die(裸片),Die經(jīng)過(guò)封裝之后就是完整的芯片產(chǎn)品了。? ? ?? 第二階段——從Die到芯片產(chǎn)品:這一階段主要就是芯片封裝,由于芯片的Die是十分脆弱的,所以通常需要用“外殼”包裹一層之后才能作為芯片產(chǎn)品出售。這一階段也是Chiplet芯片和一般芯片的最大區(qū)別,Chiplet芯片會(huì)使用1個(gè)外殼包裝至少2顆Die,而一般芯片往往是1個(gè)外殼包裝1顆Die。? ? ? ?

03?國(guó)產(chǎn)與自研

在前文中提到了,Chiplet技術(shù)的出現(xiàn)允許我們?cè)凇霸煨酒钡臅r(shí)候由淺入深地提高芯片內(nèi)部使用的“國(guó)產(chǎn)成分”比例。對(duì)于企業(yè)來(lái)說(shuō),就是“自研”的比例。那么這個(gè)比例是如何提高的呢?

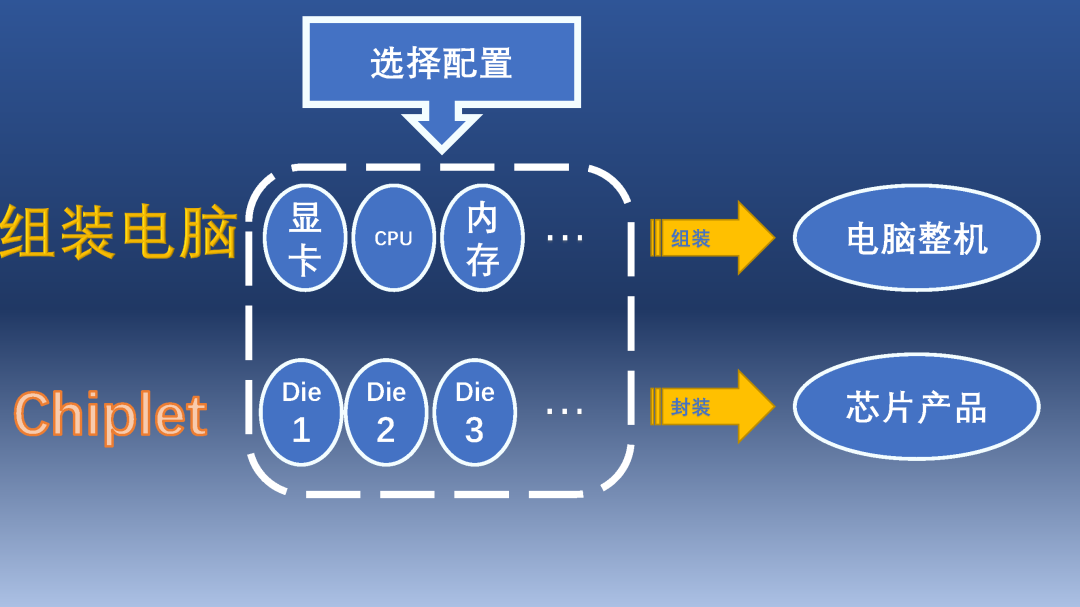

從芯片的制作流程上看,如果一家芯片公司只管芯片設(shè)計(jì),那它就是一家Fabless公司,如果一家芯片公司只管芯片制造,那它可能是晶圓廠或者封測(cè)廠,如果一家芯片公司既管設(shè)計(jì)又管制造,那它就是一家IDM公司。但是以上這些公司門檻其實(shí)都很高。 但Chiplet技術(shù)則不然,它對(duì)于公司的技術(shù)積累幾乎是無(wú)最低要求的,甚至說(shuō)出個(gè)主意就可以成為Chiplet芯片公司。當(dāng)然這個(gè)主意肯定不是說(shuō),把別人先進(jìn)芯片上的logo用砂紙打磨掉,印上自己公司的logo。 這里就不得不提到Chiplet技術(shù)與UCIe聯(lián)盟了,如果說(shuō)未來(lái)某個(gè)Chiplet技術(shù)聯(lián)盟(例如UCIe聯(lián)盟)實(shí)現(xiàn)并且推廣了不同廠商芯片間的“統(tǒng)一接口標(biāo)準(zhǔn)”,那么發(fā)布自己品牌的Chiplet芯片就會(huì)和組裝電腦一樣簡(jiǎn)單。

如果我們要組裝一臺(tái)電腦,那么就需要寫一個(gè)配置單,具體來(lái)說(shuō)就是決定用什么品牌、什么型號(hào)的顯卡、CPU、內(nèi)存等配件。由于這些配件之間連接所使用的接口通用性很強(qiáng),所以選擇的靈活性很高。例如主板上的內(nèi)存插槽是DDR5的,那么只需要選擇任意品牌的任意規(guī)格的DRR5內(nèi)存條一般都能使用。(極少數(shù)會(huì)出現(xiàn)不兼容的情況)在確定好配置之后購(gòu)買相應(yīng)配件進(jìn)行組裝就可以了,自己組裝或者委托其它人/其它平臺(tái)代為組裝都可以。如果是電腦公司的話,經(jīng)過(guò)這樣流程組裝好的電腦可以貼上自己公司的logo并作為“整機(jī)”出售。 而Chiplet芯片未來(lái)也有可能是類似的流程,先寫一個(gè)類似芯片配置單的東西,決定用什么品牌、什么型號(hào)的Die(裸片),最終將這些Die封裝到一起,成為一個(gè)獨(dú)立的芯片產(chǎn)品。如果Chiplet芯片最終發(fā)布公司不具備芯片封裝能力,還可以委托其它具備封裝能力的公司代為封裝。 如果再進(jìn)一步說(shuō),有些想要組裝電腦的人其實(shí)并沒(méi)有太多組裝和硬件搭配的相關(guān)知識(shí)。他們可以告知商家自己的需求,出售電腦配件的商家往往也樂(lè)于根據(jù)這些需求提供配置單。這對(duì)于Chiplet芯片也許也是一樣的,一家公司即使不懂不同Die(裸片)之間應(yīng)該如何搭配,他們也可以通過(guò)Die的出品廠商或者封裝廠獲得他們需要的“芯片配置單”。所以未來(lái)對(duì)于Chiplet芯片公司來(lái)說(shuō),可能真的只需要一個(gè)主意就能完成這一切。不過(guò)這是Chiplet芯片公司下限而并非上限。 同樣是拿組裝電腦舉例,有很多活躍在電商平臺(tái)上小規(guī)模的“整機(jī)”公司,在他們的整機(jī)產(chǎn)品中使用的所有配件都可以在零售市場(chǎng)上買到。例如英特爾的CPU、英偉達(dá)的顯卡,華碩的主板。而大規(guī)模的“品牌電腦”公司往往會(huì)在一些配件中使用一部分自己的東西,例如自己的主板、自己品牌的內(nèi)存條。這樣使用自己的配件一方面可以形成差異化競(jìng)爭(zhēng)(這點(diǎn)在筆記本電腦領(lǐng)域尤其凸顯),另外一方面可以節(jié)約成本,賺取更多的利潤(rùn)。 而對(duì)于Chiplet芯片公司也是這樣,在規(guī)模小的時(shí)候可以全部使用別人的Die(裸片),別人的封裝技術(shù)。不過(guò)在公司發(fā)展起來(lái)之后可以逐漸加入自己東西,比如自己設(shè)計(jì)一個(gè)ISP芯片(圖像信號(hào)處理器)的Die,然后和其它廠商的Die封裝在一起,組成一個(gè)SOC芯片。這樣這枚SOC芯片里面一部分比例的技術(shù)是自己提供的,而且融合了其它廠商的Die,最終芯片產(chǎn)品的綜合性能并不差。這樣我們?cè)凇霸煨酒钡臅r(shí)候就可以由淺入深地提高芯片內(nèi)部使用的“自研”比例。 ?

04?Chiplet的其它優(yōu)勢(shì)

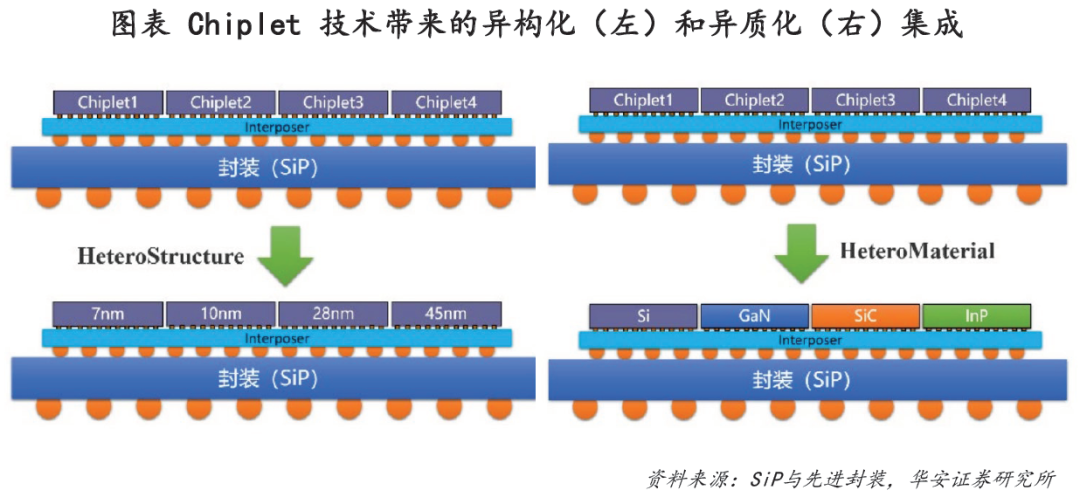

除了上文中提到的,Chiplet可以一定程度上自由組合不同廠商的Die。除此之外Chiplet還具備一些其它方面的優(yōu)勢(shì)。 靈活性高:Chiplet本質(zhì)上是將不同的Die(裸片)整合到一起,只要每個(gè)Die之間的接口兼容,那就可以完成整合。因此除了接口以外對(duì)于每個(gè)Die其實(shí)不會(huì)有太多的要求。? ? ?

如圖所示,Chiplet不光可以使用不同廠商的Die,還可以使用不同工藝甚至不同材質(zhì)的Die。這樣可以使企業(yè)在成本和定制化需求方面有更好的選擇。例如部分不需要先進(jìn)工藝的電路可以使用成熟制程制造,這樣可以節(jié)約成本。 更高的良率:當(dāng)其它條件相同時(shí),Die的面積越大,良率就會(huì)越低。

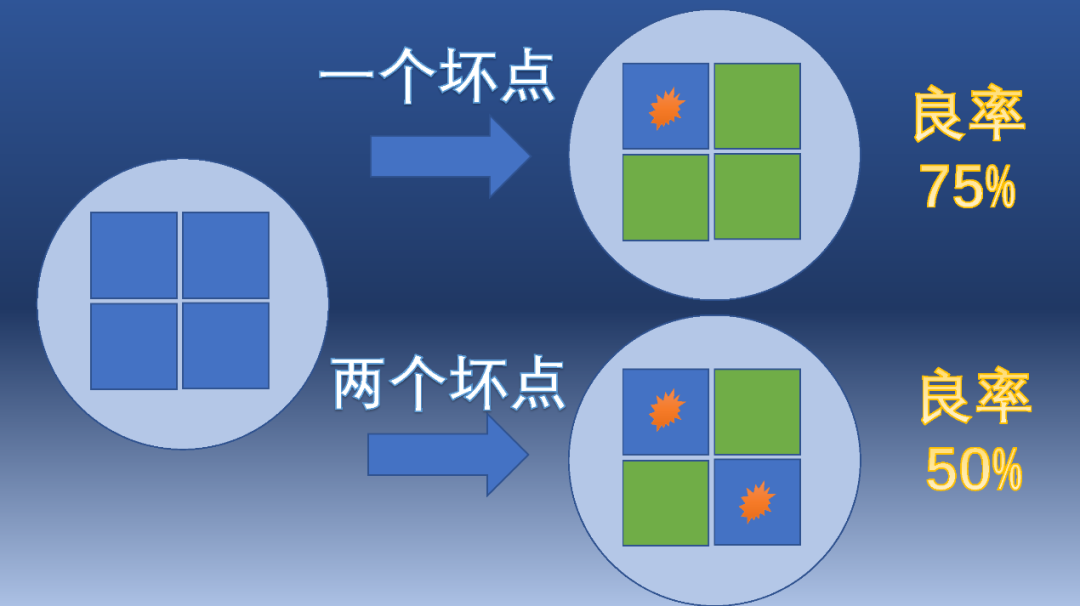

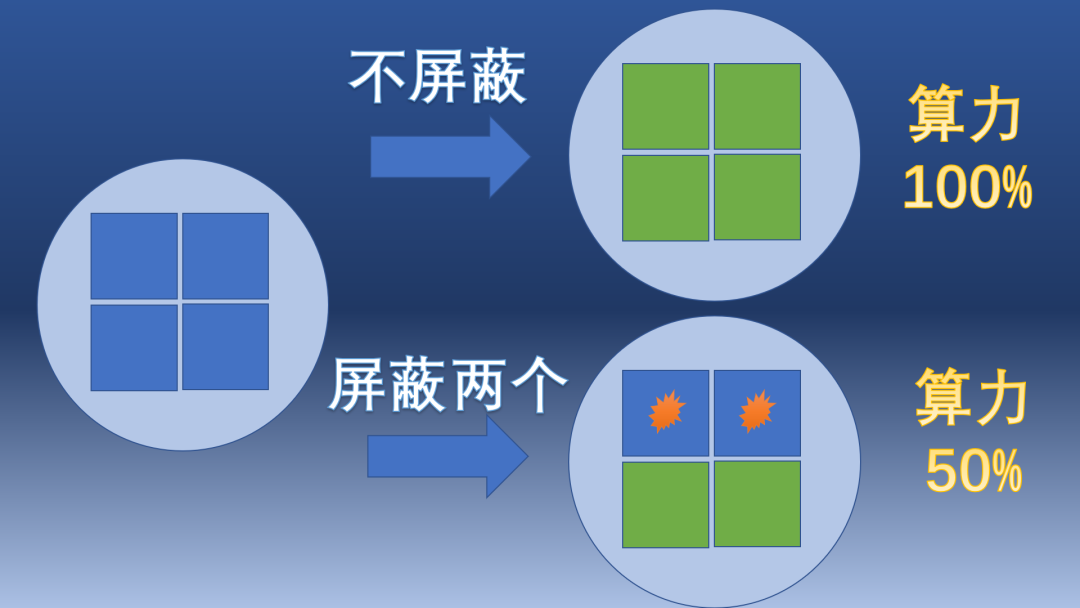

舉個(gè)例子來(lái)說(shuō),假設(shè)一塊小晶圓上面最多可以生產(chǎn)4塊Die,如圖所示當(dāng)晶圓上出現(xiàn)一個(gè)“壞點(diǎn)”時(shí),最終就只能生產(chǎn)出3塊Die,這時(shí)良率是75%。而當(dāng)出現(xiàn)兩個(gè)“壞點(diǎn)”時(shí),最終就只能生產(chǎn)出2塊Die,這時(shí)良率是50%。但如果要生產(chǎn)面積比現(xiàn)在大一倍的Die會(huì)發(fā)生什么呢?

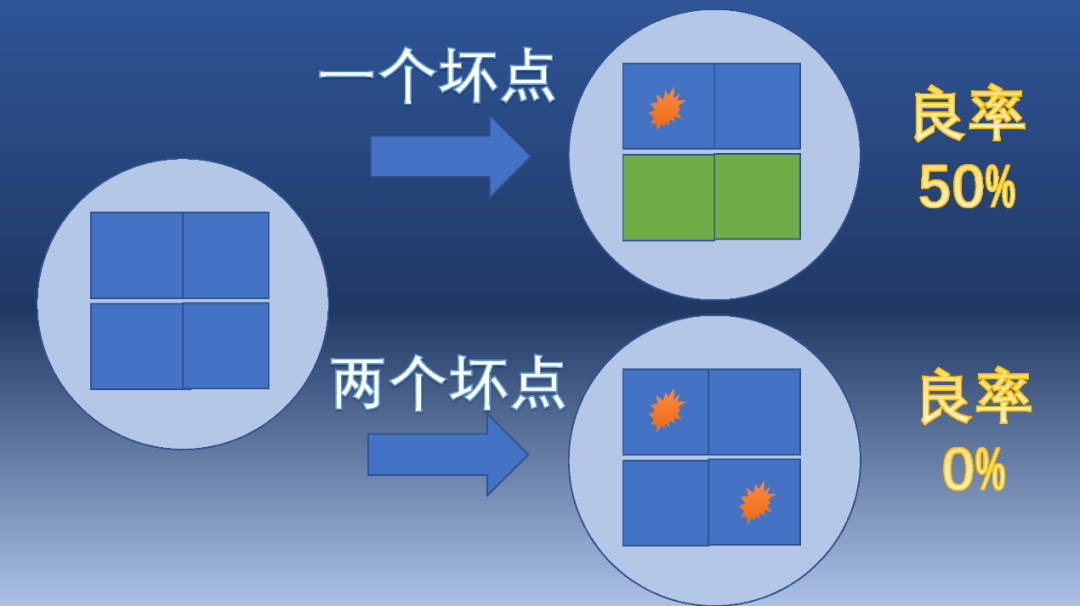

我們姑且將面積大一倍的Die稱為大Die。同樣尺寸的一個(gè)晶圓上最多可以生產(chǎn)2塊大Die。如圖所示當(dāng)晶圓上出現(xiàn)一個(gè)“壞點(diǎn)”時(shí),最終就只能生產(chǎn)出1塊大Die,這時(shí)良率是50%。而當(dāng)出現(xiàn)兩個(gè)“壞點(diǎn)”時(shí),最終就只能生產(chǎn)出0塊大Die,這時(shí)良率是0%。 因此可以這樣說(shuō),同等條件下,Die的面積越小,良率就會(huì)越高。Chiplet允許我們通過(guò)生產(chǎn)多個(gè)小面積的Die最終封裝成一個(gè)大芯片。但是需要特別說(shuō)明的是,這個(gè)結(jié)論必須在“同等條件”下才有效,現(xiàn)實(shí)情況下,其它條件往往是不同的,工藝、布局布線、溫度等因素對(duì)于良率的影響往往才是大頭。 產(chǎn)品復(fù)用:很多芯片其實(shí)需要比較頻繁地迭代,比如像手機(jī)芯片可能兩三年就會(huì)出一個(gè)新的。但是新一代的芯片內(nèi)部并不是每一個(gè)地方都是新的,有一部分會(huì)沿用舊的設(shè)計(jì)。而在Chiplet技術(shù)的影響下,我們可以模塊化地設(shè)計(jì)/制造芯片,那么可以復(fù)用的部分可以單獨(dú)做出一個(gè)模塊最終封裝到新款芯片中,這樣就可以大大節(jié)約相關(guān)的制造成本。 “性能變強(qiáng)”:“性能變強(qiáng)”這個(gè)優(yōu)勢(shì)實(shí)際上是內(nèi)行和外行之間打口水仗最多的地方,因?yàn)殡p方對(duì)于“性能”的定義往往是不一樣。從本質(zhì)上說(shuō),Chiplet技術(shù)的實(shí)際作用是突破芯片Die面積的上限。 比如說(shuō),原來(lái)是1塊面積為5的Die,如果使用Chiplet技術(shù),那就可以做成5塊面積為1的Die,然后封裝到一起就可以了。但如果順著這個(gè)思路想,我既然可以做面積為5的Die,那我能不能把5塊面積為5的Die封裝到一起呢?這樣我最終的芯片面積就是25了。我們能制造的單顆Die最大面積是有限制的。比如現(xiàn)在商用的最大晶圓尺寸一般是12英寸,那么即使說(shuō)破天,你最大也就造一塊12英寸的Die。當(dāng)然由于良品率、成本、散熱等因素的限制,實(shí)際造不了這么大。但在多方因素的影響下總歸是有一個(gè)最大尺寸限制的,而Chiplet可以通過(guò)多顆Die封裝在一起“一定程度”上繞開(kāi)這個(gè)限制。而在使用同種制造工藝的條件下,面積越大,就可以放下更多數(shù)量的晶體管,芯片的功能就越多。 那么晶體管數(shù)量越多,性能就越強(qiáng)嗎?這里開(kāi)始其實(shí)就是一個(gè)分歧點(diǎn)了,一些人認(rèn)為性能就是芯片的“總體算力”,而另一些人則認(rèn)為性能是,在其它條件大致相同的時(shí)候表現(xiàn)出的性能,這個(gè)性能的定義更接近于我們?nèi)粘I钪械摹靶省薄?/p>

比如我們手頭有兩顆同樣的4核CPU,每個(gè)核心都采用同樣的設(shè)計(jì),而且沒(méi)有“大小核”的區(qū)別。現(xiàn)在我們通過(guò)軟件屏蔽其中一顆CPU中的兩顆核心,另一顆則不作處理。這時(shí)候不作處理的CPU的算力(或者說(shuō)跑分)顯然是另一個(gè)的兩倍。但效率上,因?yàn)槊款w核心采用了同樣的設(shè)計(jì),所以兩者效率其實(shí)是一樣的。 這其實(shí)引出了一個(gè)實(shí)際問(wèn)題,如果我要跑算力(或者跑分),相關(guān)軟件多核心性能能吃滿的情況下,算力就是實(shí)際性能。但如果軟件只支持雙核CPU,那么屏蔽與不屏蔽,性能表現(xiàn)其實(shí)是一樣的。所以說(shuō),Chiplet在服務(wù)器那邊的應(yīng)用可以切實(shí)提高芯片算力,但在消費(fèi)級(jí)這邊,意義就沒(méi)有那么大了。 ?

05?Chiplet真有那么美好嗎?

首先需要鄭重說(shuō)明一點(diǎn)是,前文中提到的“Chiplet可以自由組合不同廠商的Die”屬于“前瞻性陳述”。或者換句話說(shuō),自由組合這個(gè)事至少在最近幾年沒(méi)有那么“自由”。本質(zhì)上的原因在于,目前不同Die之間的連接接口還屬于百家爭(zhēng)鳴的階段,這種高度不統(tǒng)一讓他們彼此之間難以兼容。 ? 相信有不少年紀(jì)不小的小伙伴應(yīng)該見(jiàn)過(guò)這種一拖十的充電線,由于當(dāng)時(shí)手機(jī)等數(shù)碼產(chǎn)品沒(méi)有統(tǒng)一的充電標(biāo)準(zhǔn),所以基本上就是一家一個(gè)標(biāo)準(zhǔn),一家一個(gè)接頭。直到后來(lái)才逐漸統(tǒng)一成:Type-c、Micro USB和Lightning接口。 現(xiàn)在的Chiplet也面臨類似的問(wèn)題,各家芯片的接口拋開(kāi)物理尺寸不說(shuō),在功耗、延遲、帶寬等方面差異極大。至少在現(xiàn)階段實(shí)現(xiàn)自由互聯(lián)是十分困難的。 為了讓大家團(tuán)結(jié)起來(lái),搞一個(gè)統(tǒng)一的標(biāo)準(zhǔn),UCIe聯(lián)盟出現(xiàn)了。 但是UCIe聯(lián)盟的出現(xiàn)似乎并沒(méi)有促成業(yè)界達(dá)成真的一致。

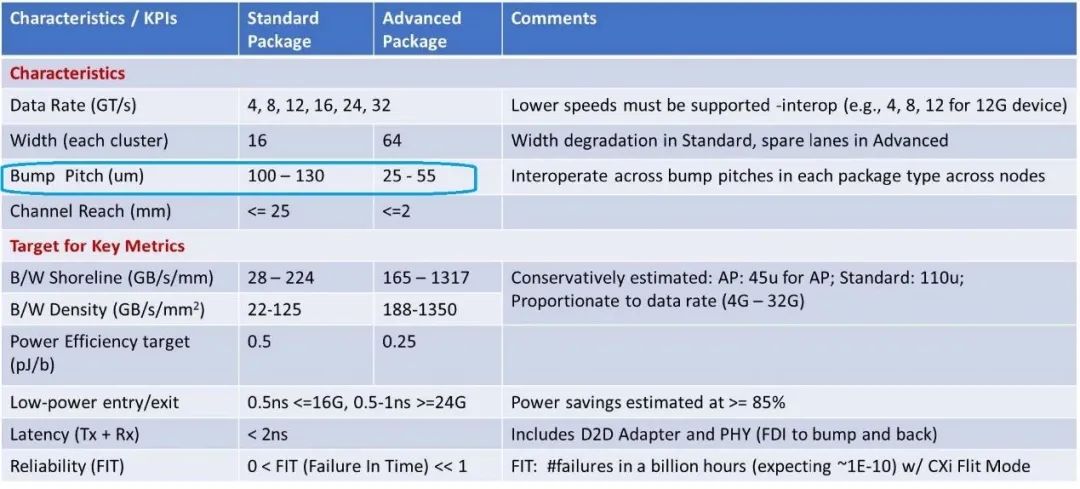

在UCIe發(fā)布的白皮書(shū)中,我們可以看到Bump間距(pitch)這一欄被分成了兩個(gè)部分,Standard Package (2D) 主要用于低成本、長(zhǎng)距離(小于等于25mm)的互連,其Bump間距要求為100um-130um。Advanced Package (2.5D) 主要用于高性能、短距離(小于等于2mm)互連,其Bump間距要求為25um-55um。 好消息是,UCIe支持較寬范圍的bump pitch。壞消息是,這個(gè)“較寬范圍”有點(diǎn)太寬了。以Advanced Package的bump pitch要求(25um-55um)為例,在這個(gè)標(biāo)準(zhǔn)下,未來(lái)可能至少衍生出4種符合這個(gè)標(biāo)準(zhǔn)的接口。也就是說(shuō)在UCIe成立之前,大家的標(biāo)準(zhǔn)百花齊放。UCIe成立之后,大家在UCIe的框架下百花齊放。雖然說(shuō)在一定程度上收緊了標(biāo)準(zhǔn),但離“真正能自由組合”的統(tǒng)一標(biāo)準(zhǔn)還有距離。不過(guò)話說(shuō)回來(lái),現(xiàn)在各家芯片接口的發(fā)展方向本質(zhì)上不一樣的,想讓他們統(tǒng)一,很難的啦。但是如果只是圍繞幾個(gè)大廠實(shí)現(xiàn)小范圍統(tǒng)一希望還是非常大的,比如以英特爾的CPU為核心,其它廠家開(kāi)發(fā)兼容英特爾CPU接口的芯片,并將其封裝到一起。 ?

06?UCIe聯(lián)盟服務(wù)于“定制芯片”

而從商業(yè)角度看,UCIe聯(lián)盟本質(zhì)上是要做“定制芯片”的生意。就比如一家沒(méi)有芯片方面技術(shù)積累的公司,可以作為甲方向芯片公司下達(dá)需求,芯片公司完成相應(yīng)需求,并將芯片產(chǎn)品交付給甲方。UCIe聯(lián)盟實(shí)際上相當(dāng)于允許甲方可以同時(shí)向多家芯片公司進(jìn)行一個(gè)委托,比如去A公司定制芯片a(或者直接選用已有型號(hào)的芯片Die),再去B公司定制芯片b,然后a+b封裝在一起。這樣一來(lái)定制的自由度其實(shí)是提高了,而且如果是選用已有型號(hào)的芯片Die,成本也會(huì)更低。 在這種商業(yè)模式下,甲方公司其實(shí)可以自己做一點(diǎn)芯片的東西并加入到最終產(chǎn)品中。這也就是借助Chiplet可以由淺入深地提高芯片內(nèi)部使用的“自研”比例。 而且近些年很多國(guó)際大廠是比較看好這類合作的。以英特爾為例,英特爾這些年在一些項(xiàng)目上的策略實(shí)際上是“不爭(zhēng)名只逐利”。從津逮CPU的案例上看,英特爾是很樂(lè)于讓其它廠商使用他們的內(nèi)核,并且使用英特爾晶圓廠的工藝制造這些芯片。而且英特爾并不介意最終的芯片產(chǎn)品上打上其它廠商的logo。并且英特爾還會(huì)發(fā)文章稱這種合作是“win-win”(雙贏),畢竟對(duì)于英特爾來(lái)說(shuō)他們?cè)搾甑腻X并沒(méi)有少掙。而對(duì)于芯片發(fā)布廠商來(lái)說(shuō),他們確實(shí)發(fā)布了一款性能和英特爾“完全一樣”的芯片產(chǎn)品。不過(guò)這個(gè)與其說(shuō)是“彎道超車”,不如說(shuō)是“站在巨人的肩膀上”。 從目前已有的案例看,想要使用英特爾的CPU內(nèi)核就必須使用英特爾的工藝,甚至最終還要配套使用英特爾的封裝技術(shù)。所以這對(duì)于英特爾等國(guó)際大廠來(lái)說(shuō)是一種擴(kuò)大銷路的方式。 ?

07?結(jié)語(yǔ)

1、Chiplet可以在有限范圍內(nèi)實(shí)現(xiàn)芯片的自由組合。我們可以借助Chiplet循序漸進(jìn)發(fā)展***。 2、這種“中美合拍”的芯片最終算不算“***”可能會(huì)取決于國(guó)產(chǎn)化的比例。不過(guò)只要芯片公司在宣發(fā)的時(shí)候說(shuō)清楚,哪些部分是自己做的?哪些部分是別人做的?那就是好公司。畢竟芯片技術(shù)是要靠腳踏實(shí)地一點(diǎn)點(diǎn)積累,要求一口吃個(gè)胖子也不現(xiàn)實(shí)。肯定有些公司在宣傳的時(shí)候不想說(shuō)清楚這些問(wèn)題,直接用“聯(lián)合研發(fā)”或者“自研”的名號(hào)糊弄過(guò)去。 3、與消費(fèi)端芯片相比,Chiplet在服務(wù)器端的優(yōu)勢(shì)更大。 4、Chiplet的很多優(yōu)勢(shì)其實(shí)來(lái)自于“先進(jìn)封裝”,但具體有哪些優(yōu)勢(shì)取決于使用何種“先進(jìn)封裝”,所以這方面內(nèi)容在本文中沒(méi)有過(guò)多展開(kāi)討論。 5、關(guān)于UCIe的相關(guān)標(biāo)準(zhǔn),由于篇幅較長(zhǎng),感興趣的讀者可以參考UCIe Specification Revision 1.0。

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論