散熱設(shè)計(jì)是芯片封裝設(shè)計(jì)中非常重要的一環(huán),直接影響芯片運(yùn)行時(shí)的溫度和可靠性。芯片內(nèi)部封裝材料的尺寸參數(shù)和物理特性對(duì)芯片散熱有較大影響,可以用芯片熱阻或結(jié)溫的高低來(lái)衡量其散熱性能的好壞。通過(guò)數(shù)值模擬(有限體積法)的方法,對(duì)某國(guó)產(chǎn)FCBGA封裝的CPU散熱性能進(jìn)行研究,分析CPU封裝內(nèi)的各層材料尺寸、導(dǎo)熱系數(shù)及功率密度等因素對(duì)CPU溫度和熱阻的影響。研究結(jié)果表明:TIM1導(dǎo)熱系數(shù)在35 W/(m·K)以內(nèi)時(shí),TIM1導(dǎo)熱系數(shù)和厚度對(duì)CPU散熱有較大影響;晶圓面積(功率密度)對(duì)CPU散熱有較大影響,晶圓厚度對(duì)CPU散熱影響不大。

01 引言

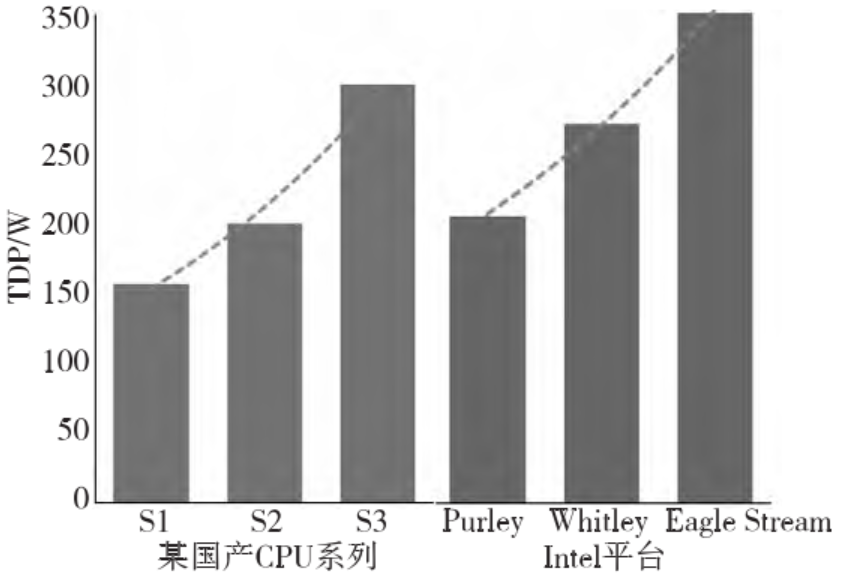

隨著萬(wàn)物互聯(lián)、云計(jì)算和5G 商用的算力需求日益增長(zhǎng),計(jì)算芯片的性能需求也越來(lái)越高,而計(jì)算性能的提高又引起芯片的功耗迅速增長(zhǎng)。圖1為某國(guó)產(chǎn)CPU平 臺(tái) 和Intel CPU平臺(tái)近三代 CPU的熱設(shè)計(jì)功耗TDP(Thermal Design Power)增長(zhǎng)趨勢(shì)圖。從圖1可以看出,其功耗年增長(zhǎng)率接近20%。同時(shí),芯片集成化和小封裝的需求也不斷增長(zhǎng),這就導(dǎo)致了芯片的功率密度(單位面積的功耗)越來(lái)越高,因此芯片散熱問(wèn)題日趨嚴(yán)峻。芯片散熱是將芯片晶圓產(chǎn)生的熱量傳遞到外界環(huán)境中去,主要通過(guò)對(duì)流、傳導(dǎo)和輻射3種換熱形式進(jìn)行。

圖1 服務(wù)器CPU功耗增長(zhǎng)趨勢(shì)

02

CPU 散熱方式

對(duì)于FCBGA(Flip Chip Ball Grid Array)倒裝球柵陣列封裝的CPU芯片來(lái)說(shuō),通常有2個(gè)傳熱路徑:一部分熱量通過(guò)封裝底面的焊盤傳導(dǎo)至主板上進(jìn)行散熱;另外一部分熱量通過(guò)封裝頂面?zhèn)鲗?dǎo)至散熱器,再由散熱器向外界環(huán)境散熱。根據(jù)FCBGA封裝的結(jié)構(gòu)特性和相關(guān)研究表明,約90%以上的熱量是通過(guò)封裝頂面?zhèn)鲗?dǎo)至散熱器進(jìn)行散熱。因此,為提高芯片散熱效率,需要盡量減少芯片晶圓到外界環(huán)境的散熱熱阻。如圖2所示,為某FCBGA封裝的CPU傳熱結(jié)構(gòu)和傳熱熱阻鏈路示意圖。

圖2 某FCBGA封裝CPU傳熱路徑

根據(jù)CPU的傳熱熱阻路徑可以得到如式(1)和式(2)所示的熱阻和溫差計(jì)算公式:

Tj-Ta=Q*(Rjc+Rcs+Rsa) (1)

Tj-Ta=ΔTjc+ΔTTIM2+ΔTheatsink?(2)

其中,Tj表示芯片結(jié)溫,單位為℃;Tc(見(jiàn)圖2)表示芯片殼溫,單位為℃;Ts(見(jiàn)圖2)表示散熱器基板溫度,單位為℃;Ta?表示環(huán)境溫度,單位為℃;Q表示芯片功耗,單位為W;ΔTjc?表示芯片結(jié)殼溫差,單位為℃;ΔTTIM2?表示界面材料 TIM2的上下表面溫差,單位為℃;Theatsink表示散熱器基板和空氣的溫差,單位為℃;Rjc表示芯片結(jié)殼熱阻,單位為℃/W,主要由封裝結(jié)構(gòu)、材料屬性決定;Rcs表示接觸熱阻,單位為℃/W,主要由 TIM2的厚度、導(dǎo)熱系數(shù)及有效傳導(dǎo)面積決定;Rsa表示散熱器熱阻,單位為℃/W,主要由散熱器本身屬性決定。

由式(1)熱阻計(jì)算公式可知,當(dāng)環(huán)境溫度和芯片功耗一定時(shí),芯片結(jié)到外界環(huán)境的熱阻越低,芯片的結(jié)溫就越小。而芯片結(jié)到環(huán)境的熱阻由結(jié)殼熱阻、接觸熱阻及散熱器熱阻三者之和組成,其中結(jié)殼熱阻為芯片內(nèi)部熱阻,接觸熱阻和散熱器熱阻為芯片外部熱阻。

本文以芯片內(nèi)部熱阻為研究目標(biāo),通過(guò)芯片級(jí)熱仿真和控制變量法,分析芯片封裝結(jié)構(gòu)和材料參數(shù)對(duì)芯片散熱效率的影響,即對(duì)芯片結(jié)殼熱阻或溫度的影響。

03

某 CPU 封裝結(jié)構(gòu)及參數(shù)定義

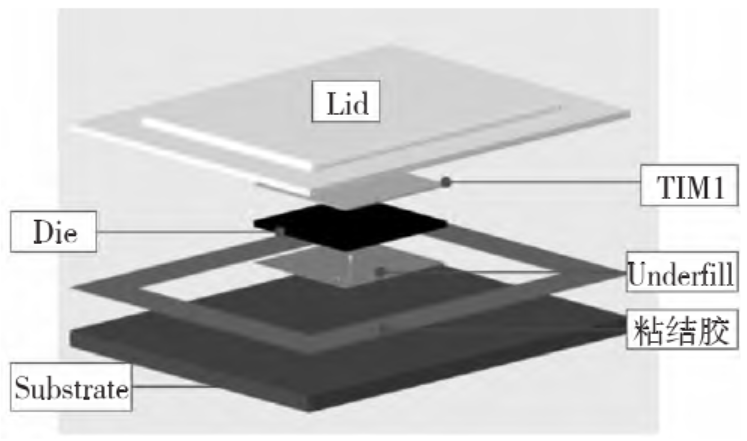

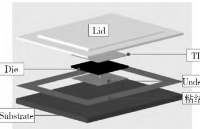

本文以某國(guó)產(chǎn)CPU為研究對(duì)象,分析 CPU封裝各個(gè)部件的結(jié)構(gòu)尺寸和材料參數(shù)對(duì)芯片散熱的影響趨勢(shì)。圖3為該CPU 的封裝結(jié)構(gòu)圖。如圖3所示,該 CPU 封裝結(jié)構(gòu)由上往下分別為散熱蓋(Lid)、界面材料 (TIM1)、晶圓 (Die)、填底材料(Underfill)、粘結(jié)膠、基板(Substrate)和焊球(Sol-derball)。因?yàn)楹盖驍?shù)量有3000余個(gè),如果詳細(xì)建模會(huì)導(dǎo)致總體網(wǎng)格數(shù)量和計(jì)算量過(guò)大,因此通過(guò)等效法將焊球歸一為各項(xiàng)異性的整體模塊,節(jié)省計(jì)算資源。

圖3 某CPU封裝結(jié)構(gòu)圖

圖3中,Lid表示 CPU 封裝頂蓋,對(duì) CPU 內(nèi)部起了一個(gè)物理隔離和保護(hù)的作用,同時(shí)具有一定的散熱作用,材質(zhì)為純銅,導(dǎo)熱系數(shù)較高;TIM1表示熱界面材料,起到粘結(jié)封裝蓋板和晶圓的作用,同時(shí)具有傳熱效果,能降低晶圓和蓋板間的接觸熱阻;Die表示 CPU 晶圓,材料為純硅;Underfill表示填底材料,用于填充晶圓和基板之間的縫隙,是倒裝芯片中使用的材料。

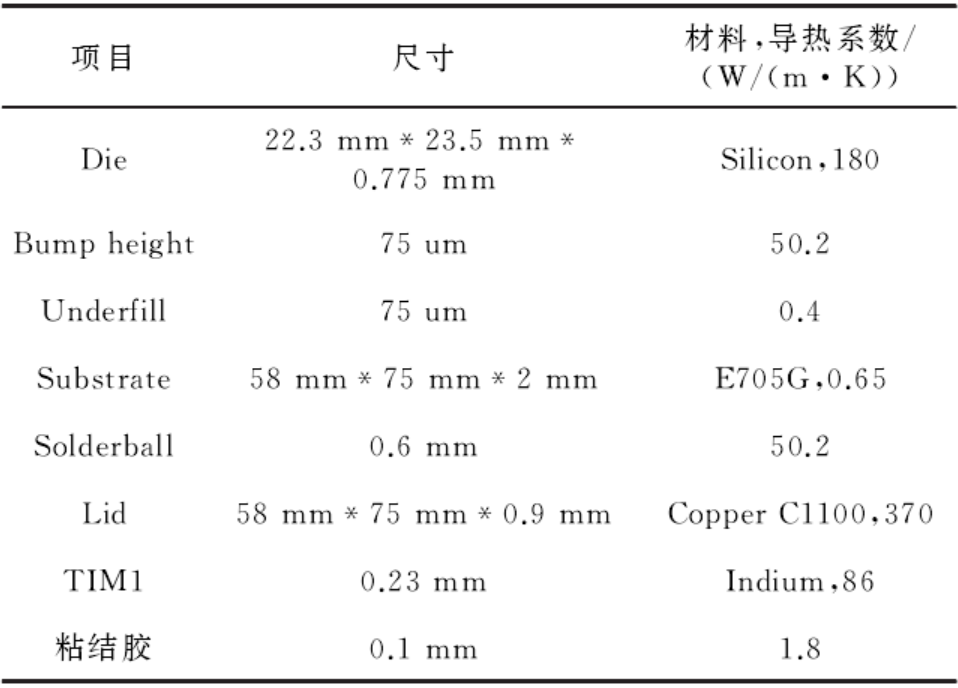

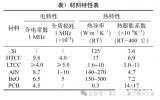

表1給出了該芯片封裝的結(jié)構(gòu)尺寸和導(dǎo)熱系數(shù)參數(shù)。

表1 某 CPU 封裝物理參數(shù)

04

研究方法

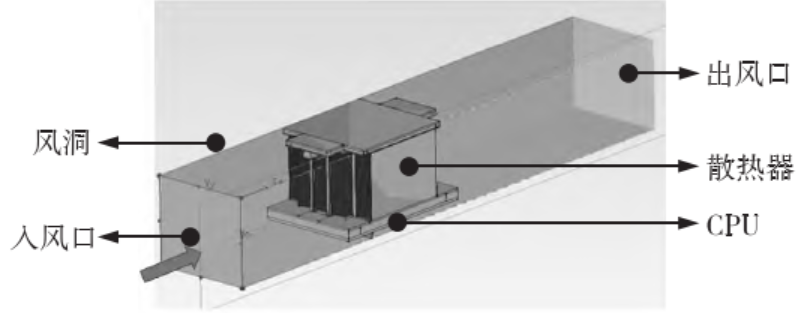

本文利用數(shù)值模擬技術(shù),建立一個(gè)數(shù)值風(fēng)洞,通過(guò)模擬CPU在數(shù)值風(fēng)洞中的散熱情況,研究CPU封裝材料和結(jié)構(gòu)參數(shù)對(duì)其散熱的影響。如圖4所示,為仿真軟件中構(gòu)建的數(shù)值風(fēng)洞,CPU 通過(guò)一種2U翅片散熱器進(jìn)行散熱,風(fēng)洞入口處給以一定風(fēng)量的入口邊界條件,以此計(jì)算 CPU 的溫度分布和最大結(jié)溫,并研究 CPU 最大結(jié)溫和各個(gè)影響因素之間的關(guān)系。

圖4 數(shù)值風(fēng)洞

05

研究結(jié)果及分析

5.1 TIM1導(dǎo)熱系數(shù)對(duì) CPU 散熱的影響

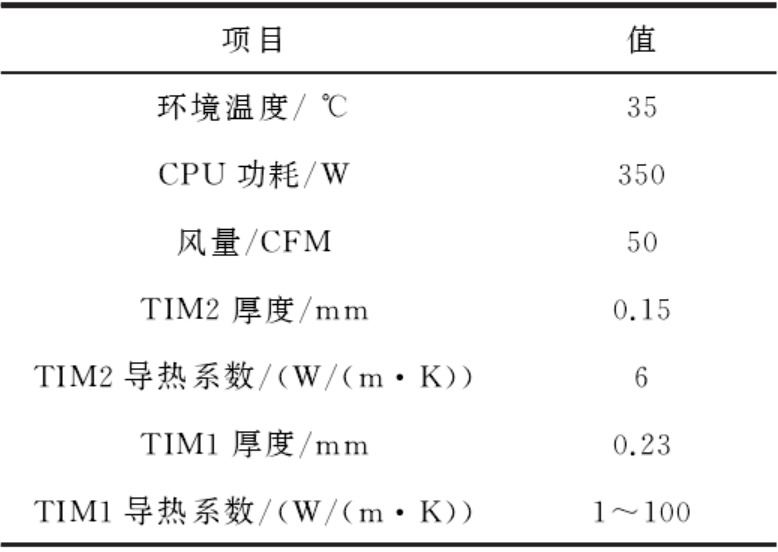

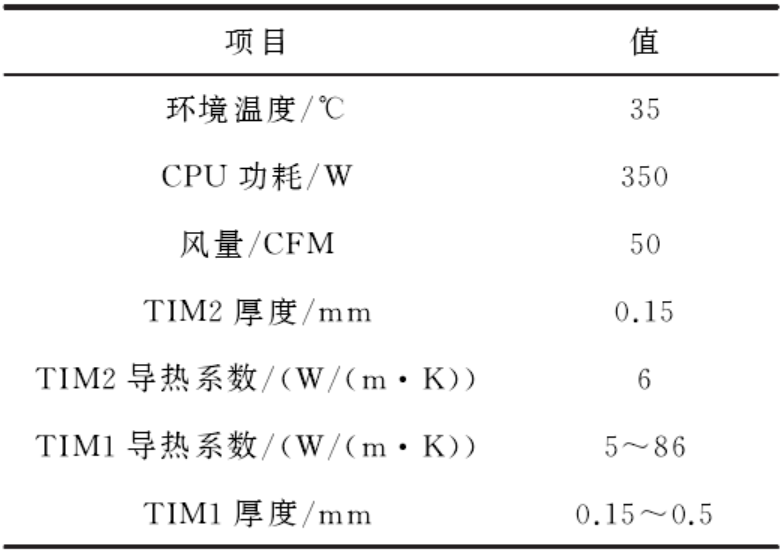

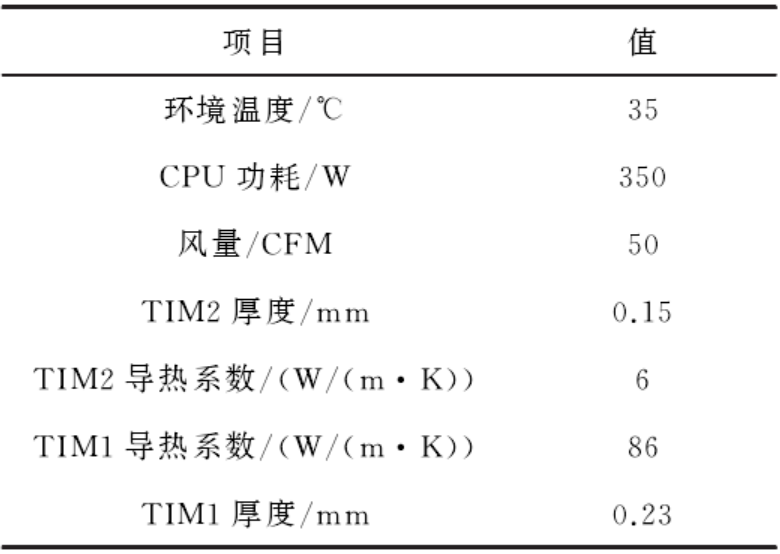

控制其他參數(shù)不變,研究 TIM1 導(dǎo)熱系數(shù)從1~100(W/(m·K))變化時(shí),CPU 最大結(jié)溫的變化情況。表2為仿真條件。

表2 TIM1導(dǎo)熱系數(shù)的仿真條件

通過(guò)一系列的仿真計(jì)算,得到 CPU 最大結(jié)溫的變化曲線圖,如圖5所示。

由圖5可以看出:

(1)TIM1導(dǎo)熱系數(shù)低于10 W/(m·K)時(shí),導(dǎo)熱系數(shù)的提升對(duì)CPU結(jié)溫的改善比較顯著;

(2)TIM1導(dǎo)熱系數(shù)超過(guò)35 W/(m·K)時(shí),CPU結(jié)溫隨導(dǎo)熱系數(shù)增高而下降的趨勢(shì)放緩,直到穩(wěn)定不變;

(3)該型號(hào) CPU 使用的 TIM1材料(Indium)導(dǎo)熱系數(shù)為86 W/(m·K),處于曲線穩(wěn)定狀態(tài);

(4)由于散熱器性能不變,所以 CPU 殼溫基本不受TIM1導(dǎo)熱系數(shù)影響。

圖5 CPU殼溫、結(jié)溫、結(jié)殼溫差與TIM1導(dǎo)熱系數(shù)的關(guān)系曲線

5.2 TIM1厚度對(duì) CPU 散熱的影響

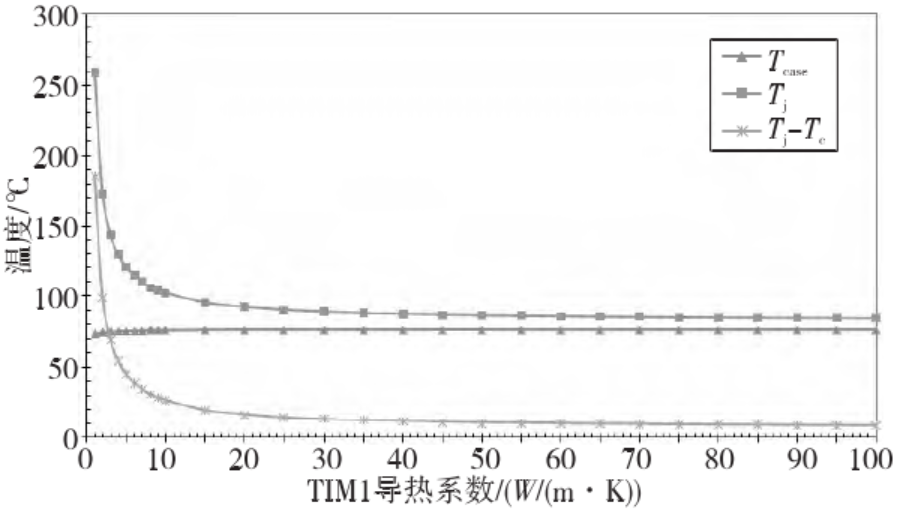

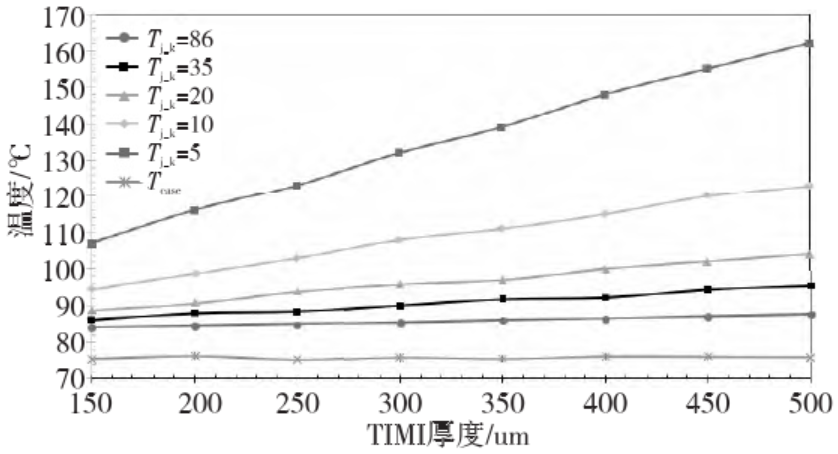

研究方法同上。由于在不同 TIM1導(dǎo)熱系數(shù)情況下,CPU 結(jié)溫隨 TIM1厚度變化的趨勢(shì)有一定差別,因此本節(jié)研究了不同 TIM1導(dǎo)熱系數(shù)情況下,TIM1厚度變化對(duì) CPU 結(jié)溫的影響。根據(jù)5.1節(jié)的計(jì)算結(jié)果,選取幾組典型的 TIM1 導(dǎo)熱系數(shù)(5 W/(m·K),10 W/(m·K),20 W/(m·K),35 W/(m·K),86 W/(m·K)),TIM1厚度控制在 0.15~0.5mm變化,計(jì)算不同導(dǎo)熱系數(shù)情況下,TIM1厚度變化對(duì)CPU最大結(jié)溫的影響。表3為本節(jié)的仿真計(jì)算條件。

表3 TIM1厚度的仿真條件

圖6為計(jì)算得到的CPU最大結(jié)溫和TIM1厚度之間的變化曲線,每一組導(dǎo)熱系數(shù)值對(duì)應(yīng)一條變化曲線。

圖6 CPU結(jié)溫與TIM1厚度的關(guān)系曲線

從圖6可以看出:

(1)TIM1厚度增大時(shí),CPU 結(jié)溫有升高趨勢(shì);

(2)TIM1導(dǎo)熱系數(shù)越小,CPU 結(jié)溫隨 TIM1厚度增加而升高的趨勢(shì)越明顯;

(3)TIM1 導(dǎo)熱系數(shù)超過(guò) 35 W/(m·K)后,TIM1厚度增加對(duì)CPU結(jié)溫影響較小;

(4)該型號(hào) CPU 使用的 TIM1材料(Indium)導(dǎo)熱系數(shù)為86 W/(m·K),此時(shí) TIM1 厚度在150~500um變化,對(duì) CPU 結(jié)溫的影響可以忽略不計(jì);

(5)由于散熱器性能不變,因此 CPU 殼溫基本不受TIM1厚度和導(dǎo)熱系數(shù)影響。

5.3 晶圓厚度對(duì) CPU 散熱的影響

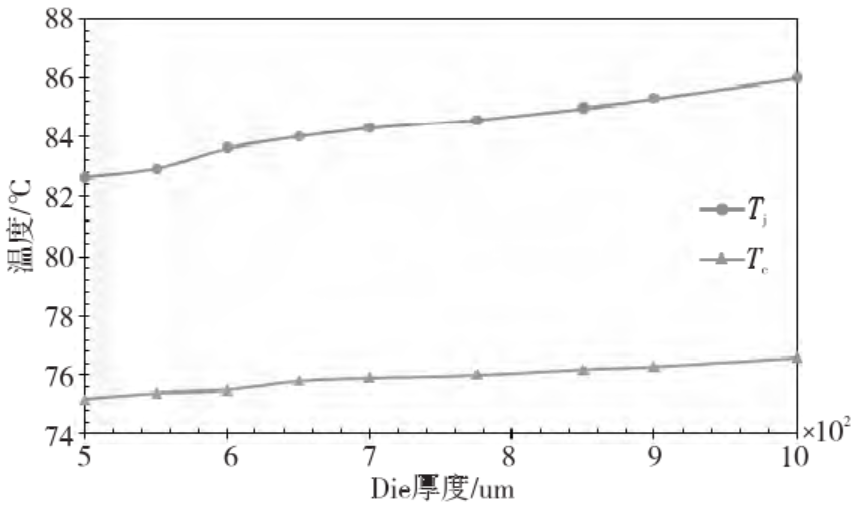

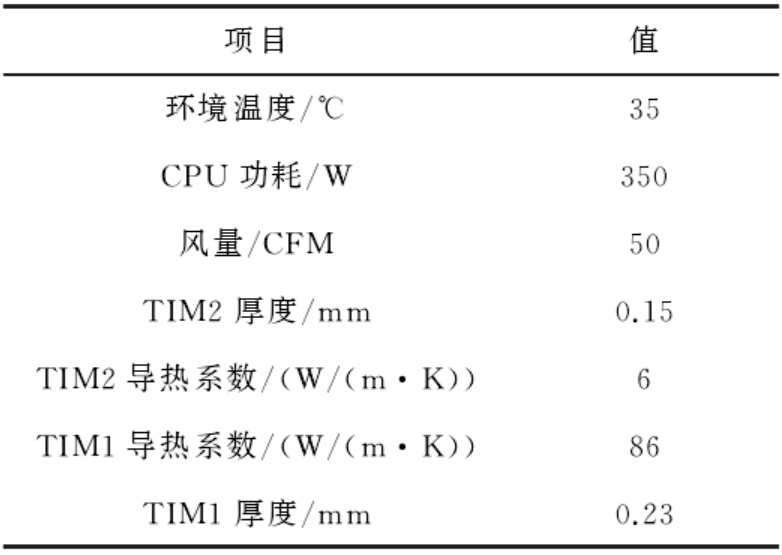

研究方法同上,控制其他參數(shù)不變,研究晶圓厚度在500~1000um變化時(shí),CPU 最大結(jié)溫的變化情況。表4為基本仿真條件。

表4 晶圓厚度的仿真條件

圖7為計(jì)算得到的CPU最大結(jié)溫和晶圓厚度之間的變化關(guān)系曲線。

圖7 CPU結(jié)溫、殼溫與晶圓厚度的關(guān)系曲線

從圖7可以看出:

(1)Die的厚度增加;CPU 結(jié)溫隨之升高;

(2)Die的厚度從0.5mm 增加至1mm;CPU溫度升高約3.5℃;

(3)由于散熱器性能不變,因此 CPU 殼溫基本不受Die厚度的影響;

(4)總體來(lái)看,Die厚度小范圍的變化對(duì) CPU散熱影響較小。

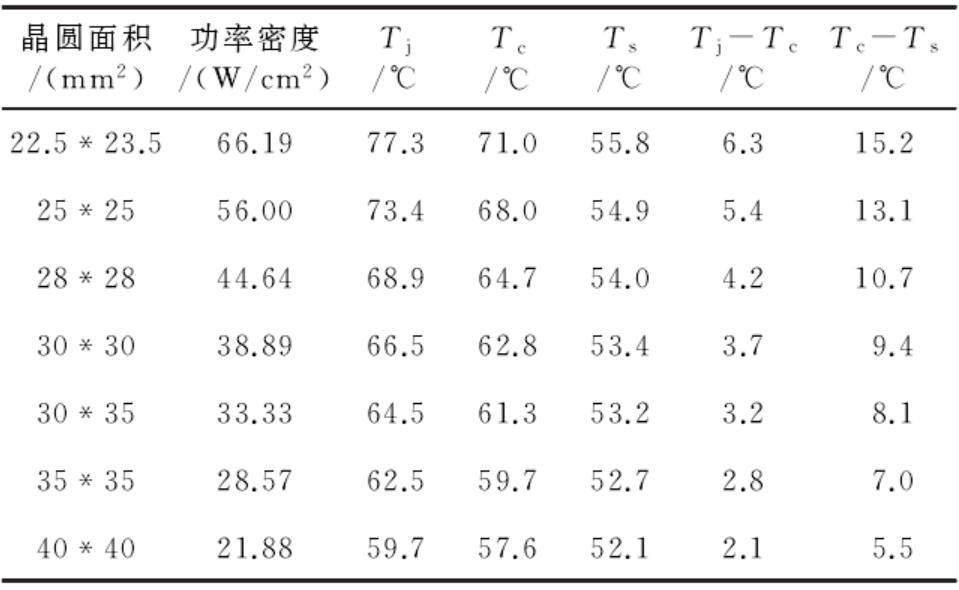

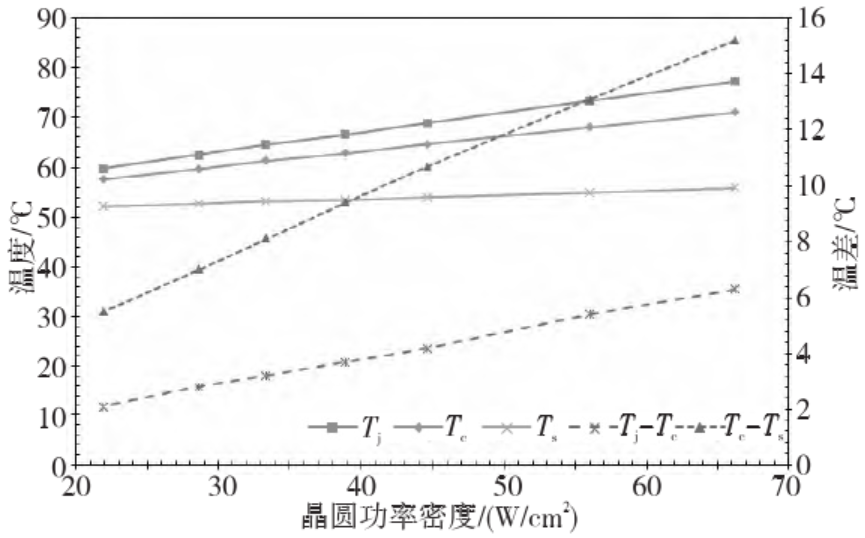

5.4 晶圓功率密度對(duì) CPU 散熱的影響

功率密度是指單位面積的功率大小,單位為?W/cm2。本節(jié)通過(guò)控制 CPU 總功率不變,改變晶圓的尺寸(面積),以此改變功率密度,再分別計(jì)算不同功率密度下CPU的散熱情況。表5為仿真條件。表6 為不同功率密度/晶圓面積下,CPU 結(jié)溫、CPU 殼溫、散熱器溫度、結(jié)殼溫差和 TIM1接觸溫差的計(jì)算結(jié)果。

表5 晶圓功率密度仿真條件

表6 不同晶圓面積/功率密度下仿真計(jì)算結(jié)果

圖8為晶圓功率密度和溫度之間的關(guān)系曲線。

圖8 晶圓功率密度與CPU結(jié)溫的關(guān)系曲線

從圖8可以看出:

(1)Die的面積越大,CPU 晶圓功率密度越小,CPU結(jié)溫、殼溫、散熱器溫度越低;

(2)Die的面積越大,CPU結(jié)殼溫差越小,即CPU結(jié)殼熱阻越小;

(3)Die的面積越大,CPU 外殼到散熱器之間的溫差越小;

(4)Die的面積(晶圓功率密度)對(duì) CPU 熱阻和接觸熱阻影響較大,Die的面積增大至40mm*40mm(功率密度為22 W/cm2左右)時(shí),CPU 結(jié)溫降低17.6℃,殼溫降低13.4℃。 ?

06

結(jié)束語(yǔ)

(1)TIM1導(dǎo)熱系數(shù)低于35 W/(m·K)時(shí),導(dǎo)熱系數(shù)的變化或者厚度變化對(duì)CPU散熱影響顯著; (2)TIM1導(dǎo)熱系數(shù)超過(guò)35 W/(m·K)時(shí),導(dǎo)熱系數(shù)的提高對(duì)CPU散熱影響較小; (3)CPU 晶圓厚度對(duì)散熱影響較小,晶圓面積對(duì)散熱影響顯著; (4)對(duì)于功耗超過(guò)200 W 的 CPU 芯片,建議使用STIM(金屬焊接封裝 TIM1),或者導(dǎo)熱系數(shù)大于35 W/(m·K)的 TIM1材料; (5)對(duì)于大功耗芯片,建議增大晶圓的設(shè)計(jì)面積,使其功率密度盡量控制在40 W/cm2以內(nèi),單個(gè)Die面積超過(guò) 30 mm*30 mm時(shí),建議使用Chiplet多核封裝; (6)建議芯片設(shè)計(jì)階段(包括封裝材料選型設(shè)計(jì)),同步進(jìn)行芯片級(jí)熱仿真評(píng)估,避免因芯片功率密度過(guò)大或者傳導(dǎo)熱阻過(guò)大引起的系統(tǒng)散熱風(fēng)險(xiǎn)或散熱瓶頸。

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論