前言

老實(shí)話,不知道這個(gè)中斷有沒(méi)有寫(xiě)的必要,因?yàn)榫W(wǎng)上有太多的優(yōu)秀的文章。

但是最后看了好多篇前輩們的文章后,仿佛懂了,但是總感覺(jué)不得勁。最后發(fā)現(xiàn)前輩的大多數(shù)內(nèi)容都是很局部的,這不是因?yàn)榍拜厒兊哪芰Γ皇且驗(yàn)榍拜呄氡M量用簡(jiǎn)短的文字去描述一些知識(shí)。

于是這篇畢竟啰嗦的文章就產(chǎn)生了,之前恰好也搞了gic,于是這里x86和arm都會(huì)有所涉及,相信這篇文章會(huì)對(duì)你有所收獲。

1、從硬件看什么是中斷?

1、前言

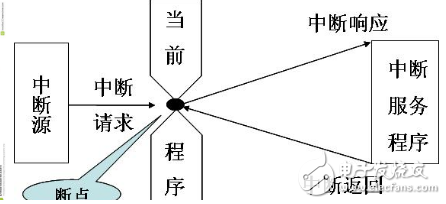

所謂中斷,是指CPU在正常運(yùn)行程序時(shí),由程序預(yù)先安排好的事件,或者由內(nèi)、外部事件引起CPU中斷正在運(yùn)行的程序,而轉(zhuǎn)到為預(yù)先安排的事件或內(nèi)、外部事件服務(wù)的程序中去。

??這些引起程序中斷的事件稱為中斷源。

??預(yù)先安排好的事件是指PC的中斷指令。

執(zhí)行到此,立即轉(zhuǎn)到對(duì)應(yīng)的服務(wù)程序去執(zhí)行。

內(nèi)部事件是指系統(tǒng)板上出現(xiàn)的一些事件信號(hào),中斷指令也可看做內(nèi)部事件。

外部事件是指某些接口設(shè)備所發(fā)出的請(qǐng)求中斷程序執(zhí)行的信號(hào),這些信號(hào)稱為中斷請(qǐng)求信號(hào)。

中斷請(qǐng)求信號(hào)何時(shí)發(fā)生是不可預(yù)知的,然而,它們一旦請(qǐng)求中斷,就會(huì)向CPU發(fā)出電信號(hào),因此這些信號(hào)CPU是可以測(cè)知的。這樣,CPU就無(wú)需花大量的時(shí)間去查詢這些信號(hào)。

例如,鍵盤(pán)何時(shí)有鍵按下是隨機(jī)的,因而CPU可以對(duì)鍵盤(pán)不加等待,而去執(zhí)行其他程序,一旦有鍵按下,鍵盤(pán)馬上產(chǎn)生中斷信號(hào),CPU得知這一信號(hào)后,就立即去執(zhí)行為鍵盤(pán)服務(wù)的中斷程序,服務(wù)結(jié)束后,CPU又恢復(fù)執(zhí)行被中斷了的程序。

??中斷服務(wù)程序執(zhí)行完,返回原來(lái)執(zhí)行程序的中斷處(稱為斷點(diǎn))繼續(xù)往下執(zhí)行,稱為中斷返回。

??有時(shí)中斷請(qǐng)求信號(hào)(即中斷源)可能有好幾個(gè),因此CPU響應(yīng)這些中斷就得有先后次序,這稱為中斷的優(yōu)先級(jí)。

優(yōu)先級(jí)高的中斷,CPU首先響應(yīng);優(yōu)先級(jí)低的中斷暫不響應(yīng),稱為掛起。

??有些中斷源產(chǎn)生的中斷,可以用編程的方法,使CPU不予理睬,這叫做中斷的屏蔽。

CPU響應(yīng)中斷轉(zhuǎn)去執(zhí)行中斷服務(wù)程序前,需要把被中斷程序的現(xiàn)場(chǎng)信息保存起來(lái),以便執(zhí)行完中斷服務(wù)程序后,接著從被中斷程序的斷點(diǎn)處繼續(xù)往下執(zhí)行。

現(xiàn)場(chǎng)信息包括程序計(jì)數(shù)器的內(nèi)容、CPU的狀態(tài)信息、執(zhí)行指令后的結(jié)果特征和一些通用寄存器的內(nèi)容。

有些信息的保存,如程序計(jì)數(shù)器的內(nèi)容等,由機(jī)器硬件預(yù)先安排完成,稱為中斷處理的隱操作;而有些信息的保存是在中斷服務(wù)程序中預(yù)先安排的。

CPU響應(yīng)中斷,由中斷源提供地址信息,引導(dǎo)程序轉(zhuǎn)移并執(zhí)行中斷服務(wù)程序,這個(gè)地址信息稱為中斷向量,它一般是和中斷源相對(duì)應(yīng)的。PC采用類型碼來(lái)標(biāo)識(shí)中斷源。

在數(shù)據(jù)采集或?qū)崟r(shí)控制中,CPU對(duì)接口設(shè)備的控制或交換信息,可采用查詢、中斷、DMA等方式,而中斷方式以其執(zhí)行速度快,可實(shí)時(shí)處理,不占用CPU過(guò)多的時(shí)間等優(yōu)點(diǎn),在接口技術(shù)中較多地被采用。

2、中斷概述

1-中斷的必要性

如上所述,CPU在與外設(shè)交換信息時(shí),若用查詢的方式,則CPU就要浪費(fèi)很多時(shí)間去等待外設(shè)。

這樣就存在一個(gè)快速的CPU與慢速的外設(shè)之間的矛盾,這也是計(jì)算機(jī)在發(fā)展過(guò)程中遇到的嚴(yán)重問(wèn)題之一。為解決這個(gè)問(wèn)題,一方面要提高外設(shè)的工作速度;另一方面發(fā)展了中斷的概念。中斷有以下好處。

??1.同步操作

有了中斷功能,就可以使CPU和外設(shè)同時(shí)工作。?CPU在啟動(dòng)外設(shè)工作后,就繼續(xù)執(zhí)行主程序,同時(shí)外設(shè)也在工作;當(dāng)外設(shè)把數(shù)據(jù)準(zhǔn)備好后,發(fā)出中斷申請(qǐng),請(qǐng)求CPU中斷它的程序,執(zhí)行輸入或輸出(中斷處理);處理完以后,CPU恢復(fù)執(zhí)行主程序,外設(shè)也繼續(xù)工作。而且有了中斷功能,CPU可命令多個(gè)外設(shè)同時(shí)工作,這樣就大大提高了CPU的利用率,也提高了輸入、輸出的速度。

? 2.實(shí)現(xiàn)實(shí)時(shí)處理 當(dāng)計(jì)算機(jī)用于實(shí)時(shí)控制時(shí),中斷是一個(gè)十分重要的功能。現(xiàn)場(chǎng)的各種參數(shù)、信息,需要的話可在任何時(shí)間發(fā)出中斷申請(qǐng),要求CPU處理;CPU可以馬上響應(yīng)(若中斷是開(kāi)放的話)并加以處理。這樣的及時(shí)處理在查詢工作方式下是做不到的。

? 3.故障處理 計(jì)算機(jī)在運(yùn)行過(guò)程中,往往會(huì)出現(xiàn)事先預(yù)料不到的情況,或出現(xiàn)一些故障,如電源突跳、存儲(chǔ)器出錯(cuò)、運(yùn)算溢出等,計(jì)算機(jī)可以利用中斷系統(tǒng)自行處理,不必停機(jī)或報(bào)告工作人員。

2 中斷源

引起中斷的原因,或能發(fā)出中斷申請(qǐng)的來(lái)源,稱為中斷源。通常中斷源有以下幾種。

? 1.一般的輸入/輸出設(shè)備 如鍵盤(pán)、紙帶讀入機(jī)、打印機(jī)等。

? 2.?dāng)?shù)據(jù)通道中斷源 如磁盤(pán)、磁帶等。3.實(shí)時(shí)時(shí)鐘

? 3.實(shí)時(shí)時(shí)鐘 在控制中,常遇到時(shí)間控制問(wèn)題等,若用CPU執(zhí)行一段程序來(lái)實(shí)現(xiàn)延時(shí)的方法,則在這段時(shí)間內(nèi),CPU不能干別的工作,降低了CPU的利用率。所以,常采用外部時(shí)鐘電路,當(dāng)需要定時(shí)時(shí),CPU發(fā)出命令,令時(shí)鐘電路(電路的定時(shí)時(shí)間通常是可編程的,即可用程序來(lái)確定和改變)開(kāi)始工作,待規(guī)定的時(shí)間到了后,時(shí)鐘電路發(fā)出中斷申請(qǐng),由CPU加以處理。(看門(mén)狗)

? 4.故障源 例如,電源掉電時(shí),需要把正在執(zhí)行的程序的狀態(tài)——PC(或IP)、各個(gè)寄存器的內(nèi)容和標(biāo)志位的狀態(tài)保留下來(lái),以便重新供電后能從斷點(diǎn)處繼續(xù)運(yùn)行。另外,目前絕大部分微型計(jì)算機(jī)中,RAM為半導(dǎo)體存儲(chǔ)器,電源掉電后,必須接入備用電源(電池)供電,以保護(hù)存儲(chǔ)器中的信息。所以,在直流電源上并上大電容,使其因掉電或電壓下降到一定值時(shí)就發(fā)出中斷申請(qǐng),由計(jì)算機(jī)的中斷系統(tǒng)執(zhí)行上述的各項(xiàng)操作。

? 5.為調(diào)試程序而設(shè)置的中斷源 一個(gè)新程序編制好以后,必須經(jīng)過(guò)反復(fù)調(diào)試才能可靠地工作。在程序調(diào)試時(shí),為了檢查結(jié)果,或?yàn)榱藢ふ颐∷冢笤诔绦蛑性O(shè)置斷點(diǎn),或進(jìn)行單步工作(一次只執(zhí)行一條指令),這要由中斷系統(tǒng)來(lái)實(shí)現(xiàn)。?(斷點(diǎn)竟然是中斷)

3 中斷系統(tǒng)的功能

為了滿足上述各種情況下的中斷要求,中斷系統(tǒng)應(yīng)具有如下功能。

? 1.實(shí)現(xiàn)中斷及返回 當(dāng)某一中斷源發(fā)出中斷申請(qǐng)時(shí),CPU能決定是否響應(yīng)這個(gè)中斷請(qǐng)求(當(dāng)CPU在執(zhí)行更緊急、更重要的工作時(shí),可以暫不響應(yīng)中斷)。若允許響應(yīng)這個(gè)中斷請(qǐng)求,CPU必須在現(xiàn)行的指令執(zhí)行完后,把斷點(diǎn)處的IP和CS的值(即下一條應(yīng)執(zhí)行指令的地址)、各個(gè)寄存器的內(nèi)容和標(biāo)志位的狀態(tài),推入堆棧保留下來(lái)──保護(hù)斷點(diǎn)和現(xiàn)場(chǎng)。然后才能轉(zhuǎn)到需要處理的中斷源的服務(wù)程序(Interrupt Service Routine)的入口,同時(shí)清除中斷請(qǐng)求觸發(fā)器。當(dāng)中斷處理完后,恢復(fù)被保留下來(lái)的各個(gè)寄存器和標(biāo)志位的狀態(tài)(稱為恢復(fù)現(xiàn)場(chǎng)),并恢復(fù)IP和CS的值(稱為恢復(fù)斷點(diǎn)),使CPU返回?cái)帱c(diǎn),繼續(xù)執(zhí)行主程序。

? 2.能實(shí)現(xiàn)優(yōu)先排隊(duì) 通常,在系統(tǒng)中有多個(gè)中斷源,會(huì)出現(xiàn)兩個(gè)或更多個(gè)中斷源同時(shí)提出中斷請(qǐng)求的情況,這樣就必須要求設(shè)計(jì)者事先根據(jù)輕重緩急,給每個(gè)中斷源確定一個(gè)中斷級(jí)別──優(yōu)先權(quán)。當(dāng)多個(gè)中斷源同時(shí)發(fā)出中斷申請(qǐng)時(shí),CPU能找到優(yōu)先權(quán)級(jí)別最高的中斷源,響應(yīng)它的中斷請(qǐng)求;在優(yōu)先權(quán)級(jí)別最高的中斷源處理完以后,再響應(yīng)級(jí)別較低的中斷源。

? 3.高級(jí)中斷源能中斷低級(jí)的中斷處理 當(dāng)CPU響應(yīng)某一中斷源的請(qǐng)求,在進(jìn)行中斷處理時(shí),若有優(yōu)先權(quán)級(jí)別更高的中斷源發(fā)出中斷申請(qǐng),則CPU要能中斷正在進(jìn)行的中斷服務(wù)程序,保留這個(gè)程序的斷點(diǎn)和現(xiàn)場(chǎng)(類似于子程序嵌套),響應(yīng)高級(jí)中斷,在高級(jí)中斷處理完以后,再繼續(xù)執(zhí)行被中斷的中斷服務(wù)程序。當(dāng)發(fā)出新的中斷申請(qǐng)的中斷源的優(yōu)先級(jí)別與正在處理的中斷源為同級(jí)或更低時(shí),CPU就先不響應(yīng)這個(gè)中斷申請(qǐng),直至正在處理的中斷服務(wù)程序執(zhí)行完以后才去處理新的中斷申請(qǐng)。

3、CPU響應(yīng)中斷的條件和過(guò)程

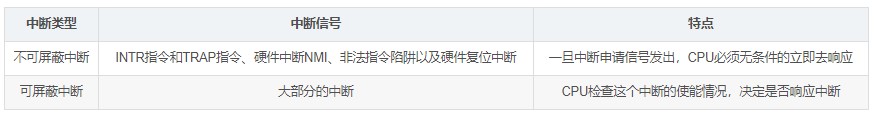

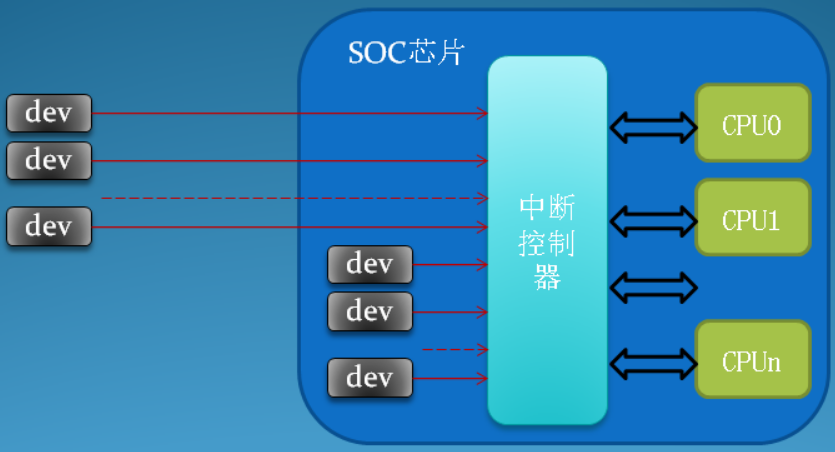

由于引腳的限制,CPU的中斷請(qǐng)求線的數(shù)量是有限的。例如,8088只有一條可屏蔽硬件中斷請(qǐng)求線(INTR)。最簡(jiǎn)單的情況當(dāng)然是只有一個(gè)中斷源,我們就從這個(gè)最簡(jiǎn)單的情況分析。

1 CPU響應(yīng)中斷的條件

??1.設(shè)置中斷請(qǐng)求觸發(fā)器

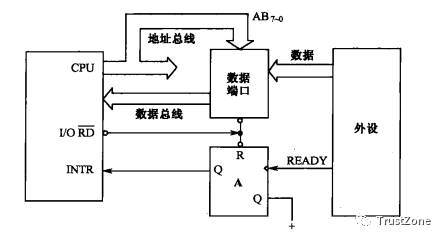

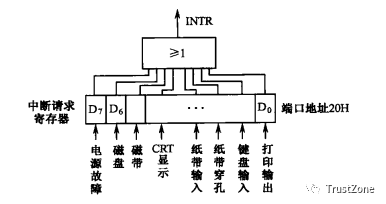

每一個(gè)中斷源,要能發(fā)出中斷請(qǐng)求信號(hào),且這個(gè)信號(hào)能一直保持到CPU響應(yīng)這個(gè)中斷請(qǐng)求后,才可清除中斷請(qǐng)求。故要求每一個(gè)中斷源有一個(gè)中斷源請(qǐng)求觸發(fā)器A,如圖所示。

圖1 設(shè)置中斷請(qǐng)求的電路

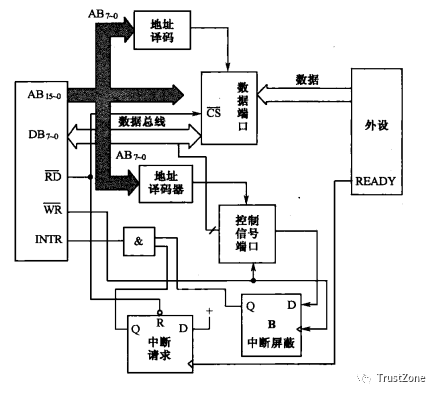

? 2.設(shè)置中斷屏蔽觸發(fā)器 在實(shí)際系統(tǒng)中,往往有多個(gè)中斷源。為了增強(qiáng)控制的靈活性,需要在每一個(gè)外設(shè)的接口電路中增加一個(gè)中斷屏蔽觸發(fā)器B,只有當(dāng)此觸發(fā)器的輸出為“1”時(shí),外設(shè)的中斷請(qǐng)求才能被送至CPU,如圖2所示。可把8個(gè)外設(shè)的中斷屏蔽觸發(fā)器組成一個(gè)端口,用輸出指令來(lái)控制它們的狀態(tài)。

圖2 具有中斷屏蔽的接口電路

2 CPU對(duì)中斷的響應(yīng)

??3.中斷是開(kāi)放的

在CPU內(nèi)部有一個(gè)中斷允許觸發(fā)器。只有當(dāng)其為“1”時(shí)(即中斷開(kāi)放時(shí)),CPU才能響應(yīng)中斷;若其為“0”(即中斷是關(guān)閉的),則即使INTR線上有中斷請(qǐng)求,CPU也不響應(yīng)。

這個(gè)觸發(fā)器的狀態(tài)可由STI和CLI指令改變。+?當(dāng)CPU復(fù)位時(shí),中斷允許觸發(fā)器的輸出為“0”,即關(guān)中斷,所以必須用STI指令開(kāi)中斷。+?當(dāng)中斷響應(yīng)后,CPU自動(dòng)關(guān)中斷,所以必須在中斷服務(wù)程序中用STI指令開(kāi)中斷。

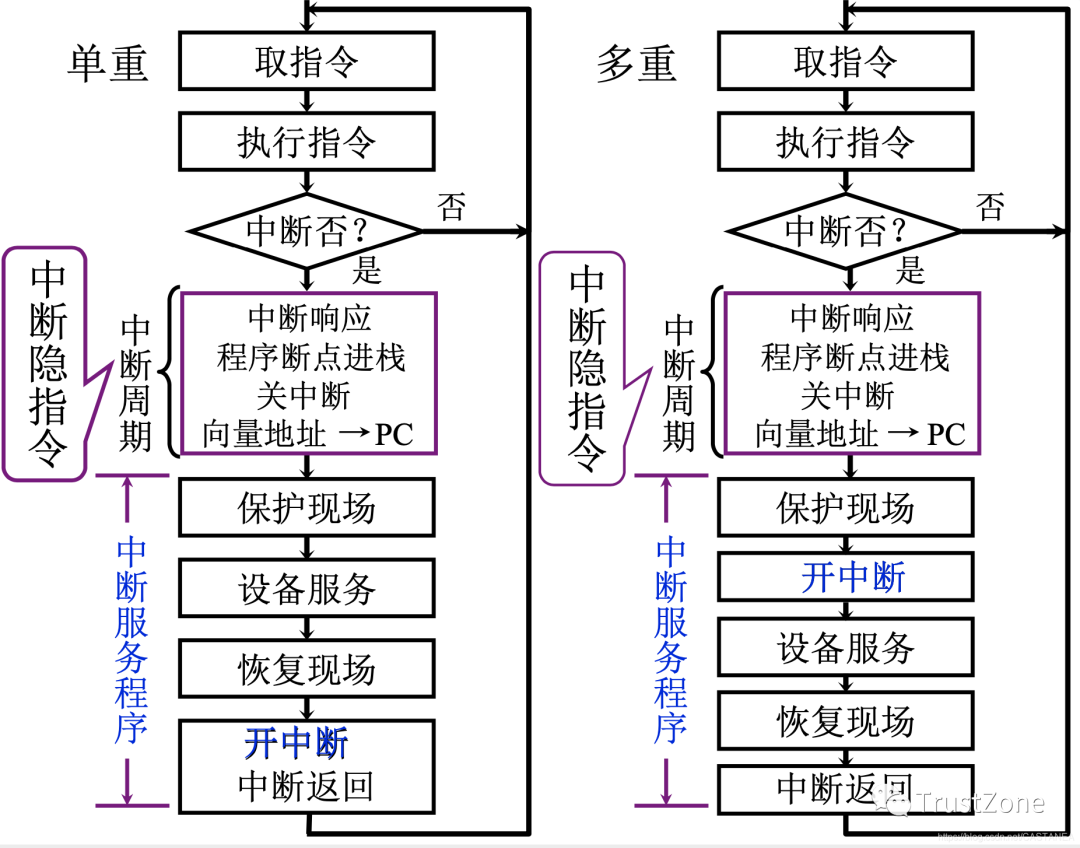

??4.CPU在現(xiàn)行指令結(jié)束后響應(yīng)中斷

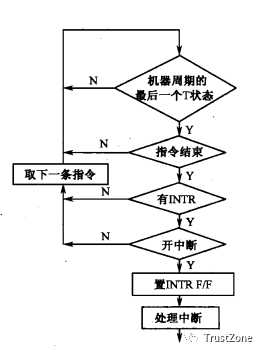

CPU在現(xiàn)行指令運(yùn)行到最后一個(gè)機(jī)器周期的最后一個(gè)T狀態(tài)時(shí),才采樣INTR線。

若發(fā)現(xiàn)有中斷請(qǐng)求,則把內(nèi)部的中斷鎖存器置“1”,下一個(gè)機(jī)器周期不進(jìn)入取指周期,而進(jìn)入中斷周期。其時(shí)序流程如圖3所示。

圖3 中斷時(shí)序流程圖

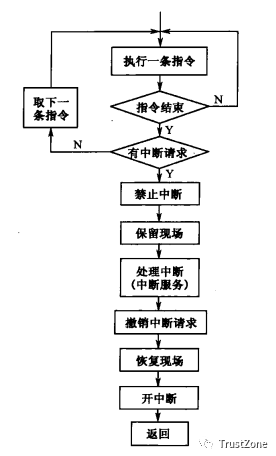

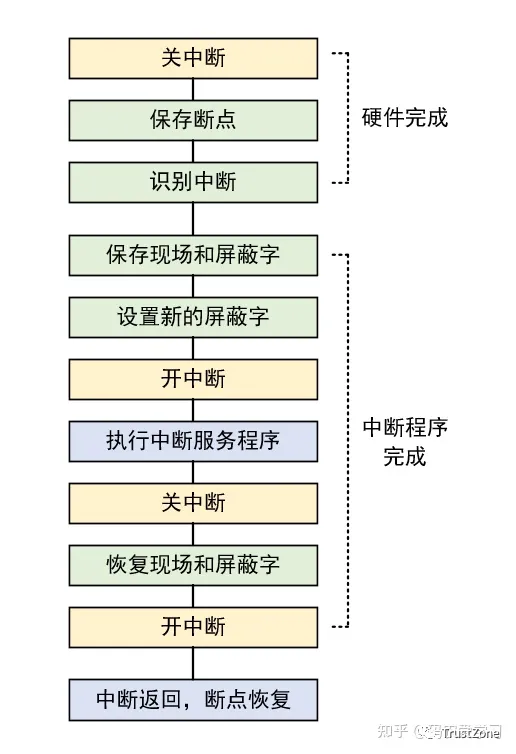

當(dāng)滿足上述條件后,CPU響應(yīng)中斷,轉(zhuǎn)入中斷周期,CPU做以下幾件事。

??1.關(guān)中斷

8088在CPU響應(yīng)中斷后,發(fā)出中斷響應(yīng)信號(hào)INTA的同時(shí),內(nèi)部自動(dòng)地實(shí)現(xiàn)關(guān)中斷。

??2.保留斷點(diǎn)

CPU響應(yīng)中斷,封鎖IP+1,且把IP和CS推入堆棧保留,以備中斷處理完畢后,能返回主程序。

??3.保護(hù)現(xiàn)場(chǎng)

為了使中斷處理程序不影響主程序的運(yùn)行,故要把斷點(diǎn)處有關(guān)的各個(gè)寄存器的內(nèi)容和標(biāo)志位的狀態(tài),推入堆棧保護(hù)起來(lái)。8088通過(guò)軟件(即在中斷服務(wù)程序中)把要用到的寄存器的內(nèi)容用PUSH指令推入堆棧。

??4.給出中斷入口,轉(zhuǎn)入相應(yīng)的中斷服務(wù)程序

8088由中斷源提供的中斷矢量形成中斷入口地址(即中斷服務(wù)程序的起始地址)。在中斷服務(wù)程序完成后,還要做下述的5、6兩步工作。

? 5.恢復(fù)現(xiàn)場(chǎng) 把所保存的各個(gè)內(nèi)部寄存器的內(nèi)容和標(biāo)志位的狀態(tài),從堆棧彈出,送回CPU中的原來(lái)位置。這個(gè)操作在8088中也是通過(guò)服務(wù)程序中的POP指令來(lái)完成的。

??6.開(kāi)中斷與返回

在中斷服務(wù)程序的最后,要開(kāi)中斷(以便CPU能響應(yīng)新的中斷請(qǐng)求)和安排一條返回指令,將堆棧內(nèi)保存的IP和CS的值彈出,程序恢復(fù)到主程序中運(yùn)行。

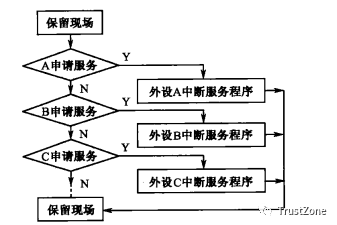

上述過(guò)程可用如圖4所示的流程圖表示。

圖4 中斷響應(yīng)、服務(wù)及返回流程圖

4、中斷優(yōu)先權(quán)及多重中斷

1 中斷優(yōu)先權(quán)

如前所述,實(shí)際的系統(tǒng)中,是有多個(gè)中斷源的,但是,由于CPU引腳的限制,往往只有一條中斷請(qǐng)求線。于是,當(dāng)有多個(gè)外中斷源同時(shí)請(qǐng)求時(shí),CPU就要識(shí)別出哪些中斷源有中斷請(qǐng)求,辨別和比較它們的優(yōu)先權(quán)(Priority),先響應(yīng)優(yōu)先權(quán)級(jí)別最高的中斷請(qǐng)求。另外,當(dāng)CPU處理中斷時(shí),也要能響應(yīng)更高級(jí)的中斷請(qǐng)求,而屏蔽掉同級(jí)或較低級(jí)的中斷請(qǐng)求。

要判別和確定各個(gè)中斷源的優(yōu)先權(quán)可以用軟件和硬件兩種方法。

1.用軟件確定中斷優(yōu)先權(quán)

軟件采用查詢技術(shù)。當(dāng)CPU響應(yīng)中斷后,就用軟件查詢以確定是哪些外設(shè)申請(qǐng)了中斷,并判斷它們的優(yōu)先權(quán)。

把8個(gè)外設(shè)的中斷請(qǐng)求觸發(fā)器組合起來(lái),作為一個(gè)端口,并賦以設(shè)備號(hào),如圖5所示,把各個(gè)外設(shè)的中斷請(qǐng)求信號(hào)相“或”后,作為INTR信號(hào),故任一外設(shè)有中斷請(qǐng)求,都可向CPU送出INTR信號(hào)。

當(dāng)CPU響應(yīng)中斷后,把中斷寄存器的狀態(tài),作為一個(gè)外設(shè)讀入CPU,逐位檢測(cè)它們的狀態(tài),若有中斷請(qǐng)求就轉(zhuǎn)到相應(yīng)的服務(wù)程序的入口。其流程如圖6所示。

查詢程序有兩種實(shí)現(xiàn)方式

??(1)屏蔽法IN ???? AL,[20H]????;輸入中斷請(qǐng)求觸發(fā)器的狀態(tài)

TEST ?? AL,80H ?????;檢查最高位

JNE ??? PWF ?????????;外設(shè)A中斷服務(wù)程序

TEST ?? AL,40H ?????;檢查次高位

JNE ??? DISS ????????;外設(shè)B中斷服務(wù)程序

TEST????AL,20H

JNE ??? MT ??????????;外設(shè)C中斷服務(wù)程序

??(2)移位法XOR?????AL,AL

IN ???? AL ,[20H]???;輸入中斷請(qǐng)求觸發(fā)器的狀態(tài)

RCL?????AL,1

JC ???? PWF ?????????;?外設(shè)A中斷服務(wù)程序

RCL?????AL,1

JC ???? DISS ????????;?外設(shè)B中斷服務(wù)程序

……查詢技術(shù)的優(yōu)點(diǎn)是:

??① 詢問(wèn)的次序,即是優(yōu)先權(quán)的次序。顯然,最先詢問(wèn)的,優(yōu)先權(quán)的級(jí)別最高。

??② 省硬件。不需要有判斷與確定優(yōu)先權(quán)的硬件排隊(duì)電路。

缺點(diǎn)是:由詢問(wèn)轉(zhuǎn)至相應(yīng)的服務(wù)程序入口的時(shí)間長(zhǎng),尤其是在中斷源較多的情況下。

2.硬件優(yōu)先權(quán)排隊(duì)電路

??(1)中斷優(yōu)先權(quán)編碼電路

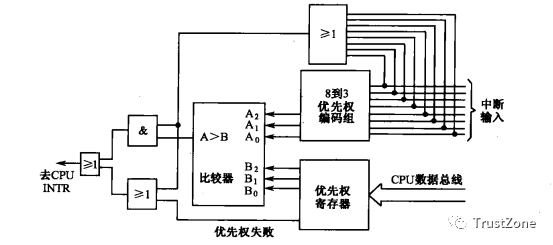

采用硬件編碼器和比較器的優(yōu)先權(quán)排隊(duì)電路,如圖7所示

圖7 編碼器和比較器的優(yōu)先權(quán)排隊(duì)電路

若有8個(gè)中斷源,當(dāng)任意一個(gè)有中斷請(qǐng)求時(shí),通過(guò)或門(mén),即可有一個(gè)中斷請(qǐng)求信號(hào)產(chǎn)生,能否送至CPU的中斷請(qǐng)求線,還要受比較器的控制(若優(yōu)先權(quán)失效信號(hào)為低電平,則與門(mén)2關(guān)閉)。

8條中斷輸入線的任一條,經(jīng)過(guò)編碼器可以產(chǎn)生三位二進(jìn)制優(yōu)先權(quán)編碼A2A1A0,優(yōu)先權(quán)最高的線的編碼為111,優(yōu)先權(quán)最低的線的編碼為000。而且若有多個(gè)輸入線同時(shí)輸入,則編碼器只輸出優(yōu)先權(quán)最高的編碼。

正在進(jìn)行中斷處理的外設(shè)的優(yōu)先權(quán)編碼,通過(guò)CPU的數(shù)據(jù)總線,送至優(yōu)先權(quán)寄存器,然后輸出編碼B2B1B0至比較器,以上過(guò)程是由軟件實(shí)現(xiàn)的。

比較器比較編碼A2A1A0與B2B1B0的大小,若A

若CPU不再進(jìn)行中斷處理時(shí)(即在執(zhí)行主程序),則優(yōu)先權(quán)失效信號(hào)為高電平,當(dāng)有任一種中斷源請(qǐng)求中斷時(shí),都能通過(guò)與門(mén)2發(fā)出INTR信號(hào)。這樣的優(yōu)先權(quán)電路,如何才能轉(zhuǎn)入優(yōu)先權(quán)最高的外設(shè)的服務(wù)程序的入口呢?當(dāng)外設(shè)的個(gè)數(shù)小于等于8時(shí),則它們公用一個(gè)產(chǎn)生中斷矢量的電路,根據(jù)比較器的編碼A2A1A0,就能做到不同的編碼轉(zhuǎn)入不同的入口地址。

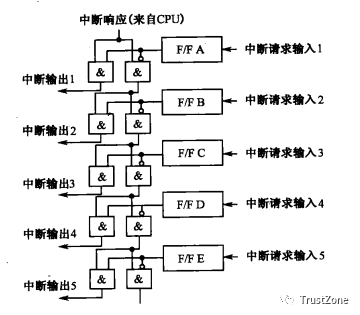

??(2)雛菊花環(huán)(Daisy Chain)式或稱為鏈?zhǔn)絻?yōu)先權(quán)排隊(duì)電路

當(dāng)多個(gè)輸入有中斷請(qǐng)求時(shí),則由中斷輸入信號(hào)的“或”電路產(chǎn)生INTR信號(hào),送至CPU。CPU執(zhí)行完現(xiàn)行指令后,響應(yīng)中斷,發(fā)出中斷響應(yīng)信號(hào)。但究竟響應(yīng)哪一個(gè)中斷呢?或CPU是轉(zhuǎn)向哪一個(gè)中斷服務(wù)程序的入口呢?這要由圖8所示的鏈?zhǔn)絻?yōu)先權(quán)排隊(duì)電路確定。

當(dāng)中斷響應(yīng)為高電平時(shí),若F/F A有中斷請(qǐng)求,則它的輸出為高電平,于是與門(mén)A1輸出為高電平,由它控制轉(zhuǎn)至中斷1的服務(wù)程序的入口,且門(mén)A2輸出為低電平,因而使門(mén)B1、B2、C1、C2…所有下面各級(jí)門(mén)的輸入和輸出全為低電平,即屏蔽了以下的各級(jí)。

若第一級(jí)沒(méi)有中斷請(qǐng)求,即F/F A=0,則中斷輸出為低電平,但門(mén)A2的輸出卻為高電平,即把中斷響應(yīng)傳遞至中斷請(qǐng)求2。若此時(shí)F/F B=1,則與門(mén)B1輸出為高電平,控制轉(zhuǎn)去執(zhí)行中斷2的服務(wù)程序;此時(shí)與門(mén)B2的輸出為低電平,因而屏蔽了以下各級(jí)。而若F/F B=0,則與門(mén)B1輸出為低電平,而與門(mén)B2輸出為高電平,把中斷響應(yīng)傳遞至中斷請(qǐng)求3……

圖8 鏈?zhǔn)絻?yōu)先權(quán)排隊(duì)電路

綜上所述,在鏈?zhǔn)絻?yōu)先權(quán)排隊(duì)電路中,

??若上級(jí)的輸出信號(hào)為“0”,則屏蔽了本級(jí)和所有的低級(jí)中斷;

??若上級(jí)輸入為“1”,在本級(jí)有中斷請(qǐng)求時(shí),則轉(zhuǎn)去執(zhí)行本級(jí)的處理程序,且使本級(jí)至下級(jí)的輸出為“0”,屏蔽所有低級(jí)中斷;

??若本級(jí)沒(méi)有中斷請(qǐng)求,則本級(jí)至下級(jí)的輸出為“1”,允許下一級(jí)中斷,故在鏈的最前面的優(yōu)先權(quán)最高。

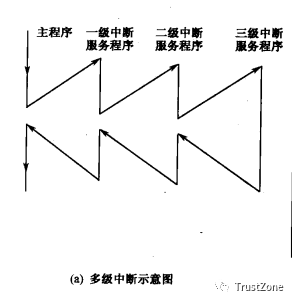

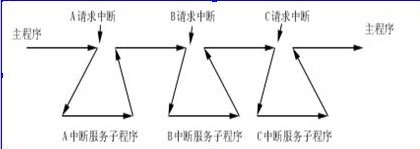

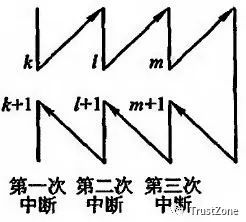

2 多級(jí)中斷的概念

多級(jí)中斷系統(tǒng)是指計(jì)算機(jī)系統(tǒng)中有相當(dāng)多的中斷源,根據(jù)各中斷事件的輕重緩急而分成若干級(jí)別,每一中斷級(jí)分配一個(gè)優(yōu)先權(quán)。

一般來(lái)說(shuō),優(yōu)先權(quán)高的中斷級(jí)可以打斷優(yōu)先權(quán)低的中斷服務(wù)程序,以程序嵌套方式進(jìn)行工作。

如圖9(a)所示,三級(jí)中斷優(yōu)先權(quán)高于二級(jí),而二級(jí)中斷優(yōu)先權(quán)高于一級(jí)。

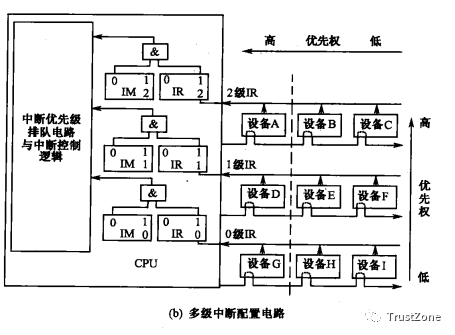

根據(jù)系統(tǒng)的配置不同,多級(jí)中斷又可分為一維多級(jí)中斷和二維多級(jí)中斷,如圖9(b)所示。

一維多級(jí)中斷是指每一中斷中只有一個(gè)中斷源,而二維多級(jí)中斷是指每一級(jí)中斷中又有多個(gè)中斷源。

圖中虛線左邊結(jié)構(gòu)為一維多級(jí)中斷,如果取掉虛線則成為二維多級(jí)中斷結(jié)構(gòu)。

對(duì)于多級(jí)中斷,我們著重說(shuō)明如下幾點(diǎn):

??第一,一個(gè)系統(tǒng)若有n級(jí)中斷,在CPU中就有n個(gè)中斷請(qǐng)求觸發(fā)器,總稱為中斷請(qǐng)求寄存器;與之對(duì)應(yīng)的有n級(jí)中斷屏蔽觸發(fā)器,總稱為中斷屏蔽寄存器。

??與單級(jí)中斷不同,在多級(jí)中斷中,中斷屏蔽寄存器的內(nèi)容是一個(gè)很重要的程序現(xiàn)場(chǎng),因此在響應(yīng)中斷時(shí),需要把中斷屏蔽寄存器的內(nèi)容保存起來(lái),并設(shè)置新的中斷屏蔽狀態(tài)。

??一般在某一級(jí)中斷被響應(yīng)后,要置“0”(關(guān)閉)本級(jí)和優(yōu)先權(quán)低于本級(jí)的中斷屏蔽觸發(fā)器,置“1”(開(kāi)放)更高級(jí)的中斷屏蔽觸發(fā)器,以此來(lái)實(shí)現(xiàn)正常的中斷嵌套。

??第二,多級(jí)中斷中的每一級(jí)可以只有一個(gè)中斷源,也可以有多個(gè)中斷源。在多級(jí)中斷之間可以實(shí)現(xiàn)中斷嵌套,但是同一級(jí)內(nèi)的不同中斷源的中斷是不能嵌套的,必須是處理完一個(gè)中斷后再響應(yīng)和處理同一級(jí)內(nèi)的其他中斷源。

??第三,設(shè)置多級(jí)中斷的系統(tǒng)一般都希望有較快的中斷響應(yīng)時(shí)間,因此首先響應(yīng)哪一級(jí)中斷和哪個(gè)中斷源,由硬件邏輯實(shí)現(xiàn),而不是由程序?qū)崿F(xiàn)。

??圖9(b)中的中斷優(yōu)先排隊(duì)電路,就是用于決定優(yōu)先響應(yīng)中斷級(jí)的硬件邏輯。另外,在二維中斷結(jié)構(gòu)中,除了由中斷優(yōu)先級(jí)排隊(duì)電路確定優(yōu)先響應(yīng)中斷級(jí)外,還要確定優(yōu)先響應(yīng)的中斷源,一般通過(guò)鏈?zhǔn)讲樵兊挠布壿媮?lái)實(shí)現(xiàn)。

??顯然,這是用獨(dú)立請(qǐng)求方式與鏈?zhǔn)讲樵兎绞较嘟Y(jié)合的方法來(lái)決定首先響應(yīng)哪個(gè)中斷源。

??第四,和單級(jí)中斷情況類似,在多級(jí)中斷中也使用中斷堆棧保存現(xiàn)場(chǎng)信息。使用堆棧保存現(xiàn)場(chǎng)的好處是:

??① 控制邏輯簡(jiǎn)單,保存和恢復(fù)現(xiàn)場(chǎng)的過(guò)程按先進(jìn)后出順序進(jìn)行。

??②?每一級(jí)中斷不必單獨(dú)設(shè)置現(xiàn)場(chǎng)保護(hù)區(qū),各級(jí)中斷現(xiàn)場(chǎng)可按其順序放在同一棧里。

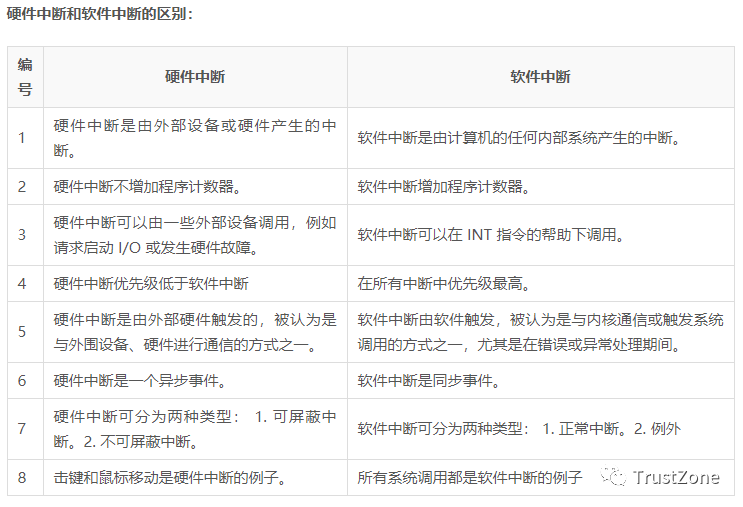

5、 8088的中斷方式

8088有兩種類型的中斷:由執(zhí)行某些指令引起的軟中斷和設(shè)備引起的硬中斷,這兩類中斷均有中斷類型碼相對(duì)應(yīng)。

1.軟中斷

執(zhí)行下述指令時(shí),將產(chǎn)生或可能產(chǎn)生中斷。

??(1)DIV(除)或IDIV(整除)指令

當(dāng)執(zhí)行這些除法指令時(shí),若除數(shù)為0或商溢出,則產(chǎn)生中斷,稱為0型中斷。

??(2)INT指令

當(dāng)執(zhí)行中斷指令I(lǐng)NT n時(shí),則產(chǎn)生n型中斷。

??(3)INTO指令

若在指令序列執(zhí)行過(guò)程中,上條指令執(zhí)行的結(jié)果使溢出標(biāo)志位O=1,接著若執(zhí)行的是INTO指令,則引起內(nèi)部中斷,稱為4型中斷;若溢出標(biāo)志位O=0,該指令將不起作用。

??(4)單步執(zhí)行

當(dāng)標(biāo)志位T=1時(shí),每執(zhí)行一條指令,則引起一次中斷,即指令為單步執(zhí)行方式,這種方式常用于程序的調(diào)試。單步執(zhí)行為1型中斷。

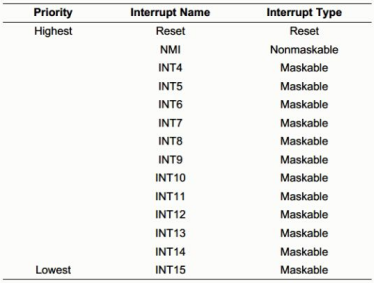

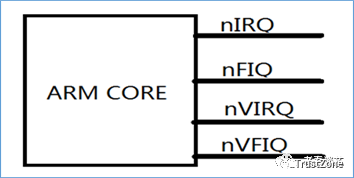

2.硬中斷

8088有兩種中斷請(qǐng)求線:

非屏蔽中斷NMI線和可屏蔽中斷INTR線,在這兩條線上產(chǎn)生中斷請(qǐng)求信號(hào)而引起的中斷稱為硬中斷。

??(1)可屏蔽中斷

出現(xiàn)在INTR線上的請(qǐng)求信號(hào)是電平觸發(fā)的,它的出現(xiàn)是異步的,在CPU內(nèi)部由CLK的上升沿來(lái)同步。在該線上的中斷請(qǐng)求信號(hào)(高電平有效)必須保持到當(dāng)前指令的結(jié)束。

在這條線上出現(xiàn)的中斷請(qǐng)求,CPU是否響應(yīng)要取決于標(biāo)志位I的狀態(tài), + 若I=1,則CPU就響應(yīng),可以認(rèn)為此時(shí)CPU處于中斷狀態(tài);+ 若I=0,則CPU就不響應(yīng)。

I位的狀態(tài),可以用指令STI使其置位(即開(kāi)中斷);也可用CLI指令使其復(fù)位(即關(guān)中斷)。?要注意:+ 在系統(tǒng)復(fù)位以后,標(biāo)志位I=0;此外任一種中斷(內(nèi)部中斷、NMI、INTR)被響應(yīng)后,I=0。所以必須在一定的時(shí)候用STI來(lái)開(kāi)放中斷。+ CPU是在當(dāng)前指令周期的最后一個(gè)T狀態(tài)采樣中斷請(qǐng)求信號(hào)的,?若發(fā)現(xiàn)有可屏蔽中斷請(qǐng)求,且中斷允許(I=1),則CPU進(jìn)入中斷響應(yīng)周期。

(時(shí)鐘周期,又稱節(jié)拍周期,是處理器的最基本單位,晶振頻率的倒數(shù),也稱T狀態(tài))

??(2)非屏蔽中斷

當(dāng)NMI線上出現(xiàn)一個(gè)由低向高上跳的高電平中斷請(qǐng)求信號(hào)后(持續(xù)時(shí)間大于兩個(gè)時(shí)鐘周期),不管標(biāo)志寄存器I位的狀態(tài)如何,當(dāng)前指令執(zhí)行完成后,8088馬上轉(zhuǎn)入中斷處理。

此種類型的中斷有三種來(lái)源:+ 電源故障, + 系統(tǒng)板上隨機(jī)存儲(chǔ)器奇偶校驗(yàn)錯(cuò), + 8087(協(xié)處理器)中斷請(qǐng)求和I/O通道檢查錯(cuò)。非屏蔽中斷的優(yōu)先權(quán)高于可屏蔽中斷。

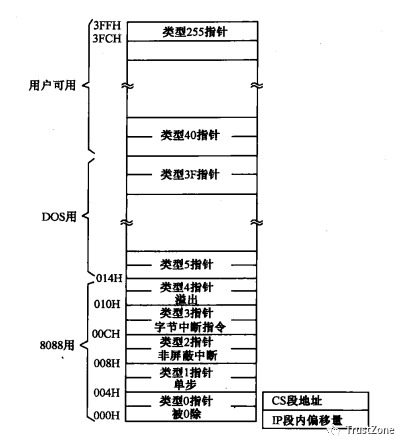

3.中斷向量表

8088中有一個(gè)簡(jiǎn)單而又多功能的中斷系統(tǒng)。上述的任何一種中斷,CPU響應(yīng)以后,都要保護(hù)現(xiàn)場(chǎng)(主要是標(biāo)志位)和保護(hù)斷點(diǎn)(現(xiàn)行的碼段寄存器CS和指令指針I(yè)P),然后轉(zhuǎn)入各自的中斷服務(wù)程序。在8088中各種中斷如何轉(zhuǎn)入各自的中斷服務(wù)程序呢?

8088在內(nèi)存的前1KB(地址為00000H~003FFH)建立了一個(gè)中斷向量表,可以容納256個(gè)中斷向量(或256個(gè)中斷類型),每個(gè)中斷向量占用4B。(這個(gè)應(yīng)該是)

在這4B中,包含著這個(gè)中斷向量(或這個(gè)中斷類型)的服務(wù)程序的入口地址——前兩個(gè)字節(jié)為服務(wù)程序的IP,后兩個(gè)字節(jié)為服務(wù)程序的CS,如圖10所示。(CS:IP)

其中前5個(gè)中斷向量(或中斷類型)由Intel專用,系統(tǒng)又保留了若干個(gè)中斷向量,余下的就可以由用戶自己使用,作為中斷源的向量。

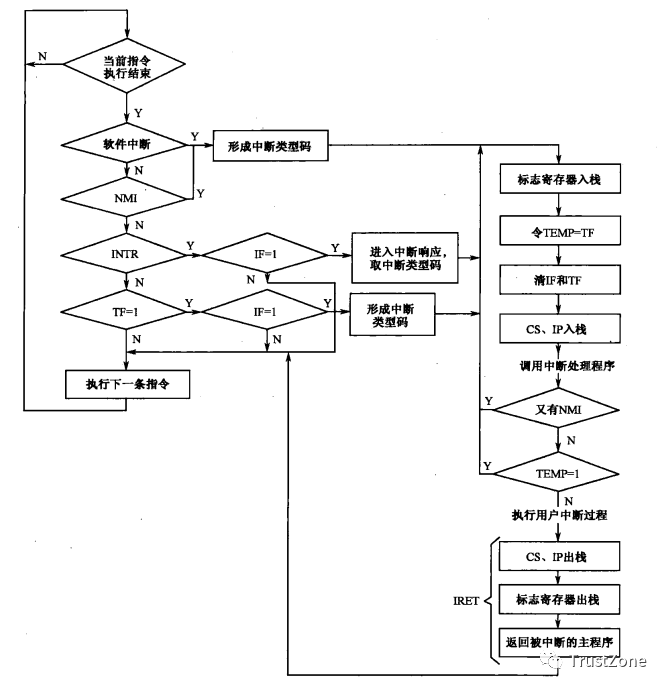

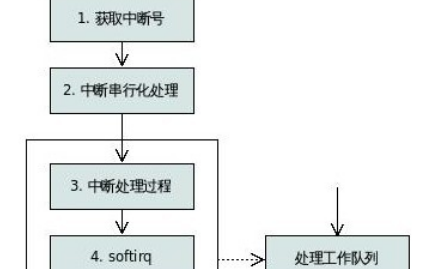

4.8088中的中斷響應(yīng)和處理過(guò)程

8088中各種中斷的響應(yīng)和處理過(guò)程是不相同的,但主要區(qū)別在于如何獲取相應(yīng)的中斷類型碼(向量號(hào))。

對(duì)于硬件(外部)中斷,CPU在當(dāng)前指令周期的T狀態(tài)采樣中斷請(qǐng)求信號(hào),

??如果有可屏蔽中斷請(qǐng)求,且CPU處在開(kāi)中斷狀態(tài)(I標(biāo)志為1),則CPU轉(zhuǎn)入兩個(gè)連續(xù)的中斷響應(yīng)周期,在第二個(gè)中斷周期的T4狀態(tài)前沿,采樣數(shù)據(jù)線獲取由外設(shè)輸入的類型碼;

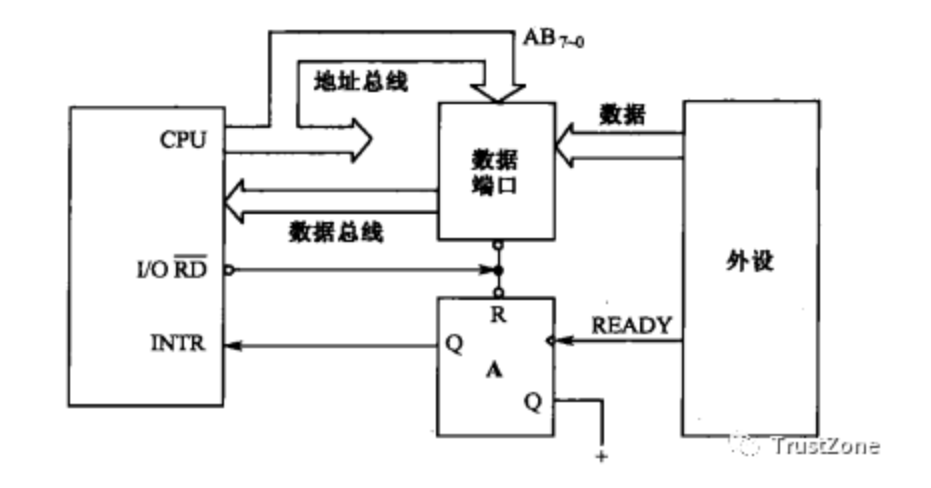

C.PU在T1、T2、T3、T4這四個(gè)狀態(tài)完成一個(gè)總線周期。 在T1狀態(tài),把地址信息從地址線A19~A16,A15~A8和AD7~AD0上輸出,且立即發(fā)出地址鎖存信號(hào)ALE,把在A19~A16上出現(xiàn)的高4位地址和在AD15~AD0(8088則是AD7~AD0)上出現(xiàn)的地址,在外部地址鎖存器上鎖存。 在T2狀態(tài),CPU發(fā)送讀寫(xiě)等控制命令。 在T3、T4狀態(tài),CPU發(fā)送或接收數(shù)據(jù),并在T4狀態(tài)結(jié)束此總線周期。 當(dāng)外部存儲(chǔ)器或I/O端口的時(shí)序不能與CPU的時(shí)序相配合時(shí),就需要插入TW周期。 **因此,在CPU中設(shè)計(jì)了一條準(zhǔn)備就緒READY輸入線,即存儲(chǔ)器或I/O端口輸給CPU的狀態(tài)線。** CPU在T3采樣READY線,若為高電平,則在T3狀態(tài)后進(jìn)入T4狀態(tài)。 若存儲(chǔ)器或I/O端口來(lái)不及在T4狀態(tài)的前沿把數(shù)據(jù)準(zhǔn)備好,則當(dāng)CPU在T3狀態(tài)采樣時(shí)應(yīng)使READY線為低電平,并在T3狀態(tài)后插入一個(gè)等待狀態(tài)TW。

??若是采樣到非屏蔽中斷請(qǐng)求,則CPU不經(jīng)過(guò)上述的兩個(gè)中斷響應(yīng)周期,而在內(nèi)部自動(dòng)產(chǎn)生中斷類型碼2。

對(duì)于軟件中斷,中斷類型碼也是自動(dòng)形成的。對(duì)于INT n指令,則類型碼即為指令中給定的n。8088在取得了類型碼后的處理過(guò)程是一樣的,其順序?yàn)椋?/p>

??① 將類型碼乘4,作為中斷向量表的指針;

??② 把CPU的標(biāo)志寄存器入棧,保護(hù)各個(gè)標(biāo)志位,此操作類似于PUSH F指令;

??③ 復(fù)制追蹤標(biāo)志T的狀態(tài),接著清除I和T標(biāo)志,屏蔽新的INTR中斷和單步中斷;

??④ 保存主程序中的斷點(diǎn),即把主程序斷點(diǎn)處的IP和CS的值推入堆棧保護(hù),先推入CS的值,再推入IP的值;

??⑤ 從中斷向量表中取中斷服務(wù)程序的入口地址,分別送至CS和IP中,先取CS的值;

??⑥ 按新地址執(zhí)行中斷服務(wù)程序。

在中斷服務(wù)程序中,通常要保護(hù)CPU內(nèi)部寄存器的值(保護(hù)現(xiàn)場(chǎng))及開(kāi)中斷(若允許中斷嵌套的話)。

在中斷服務(wù)程序執(zhí)行完后,要恢復(fù)現(xiàn)狀,最后執(zhí)行中斷返回指令I(lǐng)RET。

IRET指令按次序恢復(fù)斷點(diǎn)處的IP和CS的值,恢復(fù)標(biāo)志寄存器(相當(dāng)于POP F)。

于是程序就恢復(fù)到斷點(diǎn)處繼續(xù)執(zhí)行。8088的中斷響應(yīng)和處理過(guò)程可用如圖11所示的流程圖來(lái)表示。

6、IBM PC/XT的中斷方式

1.IBM PC/XT的中斷類型

在IBM PC/XT中有三種類型的中斷。

??(1)內(nèi)部中斷即軟中斷

包括被0除、單步執(zhí)行、溢出和中斷指令(包括斷點(diǎn)中斷)等。這是由8088執(zhí)行指令產(chǎn)生的中斷。

??(2)非屏蔽中斷NMI

在IBM PC/XT中若存儲(chǔ)器的讀/寫(xiě)奇偶校驗(yàn)錯(cuò),或者是由8087(協(xié)處理器)的異常所產(chǎn)生的中斷,都送至8088的NMI輸入端要求處理。

??(3)可屏蔽中斷INTR

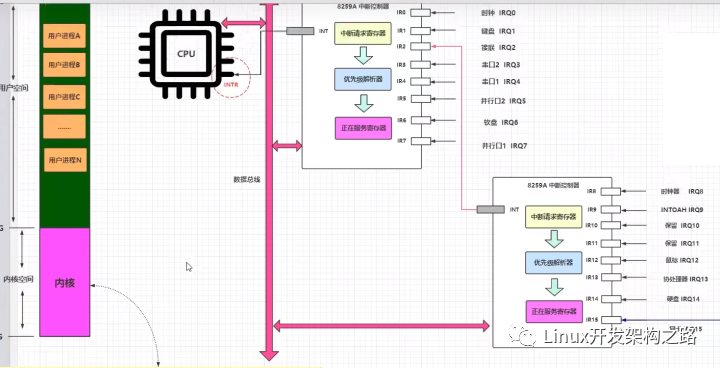

在IBM PC/XT系統(tǒng)中,可能有多個(gè)外部設(shè)備中斷請(qǐng)求信號(hào),而8088 CPU的可屏蔽中斷輸入信號(hào)只有一個(gè)INTR。

為此,在IBM PC/XT系統(tǒng)中,采用中斷控制器(8259)將外部設(shè)備中斷請(qǐng)求信號(hào)擴(kuò)充到8個(gè)。

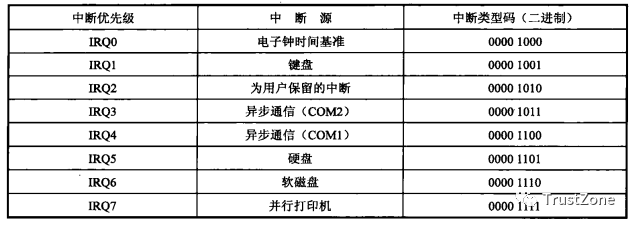

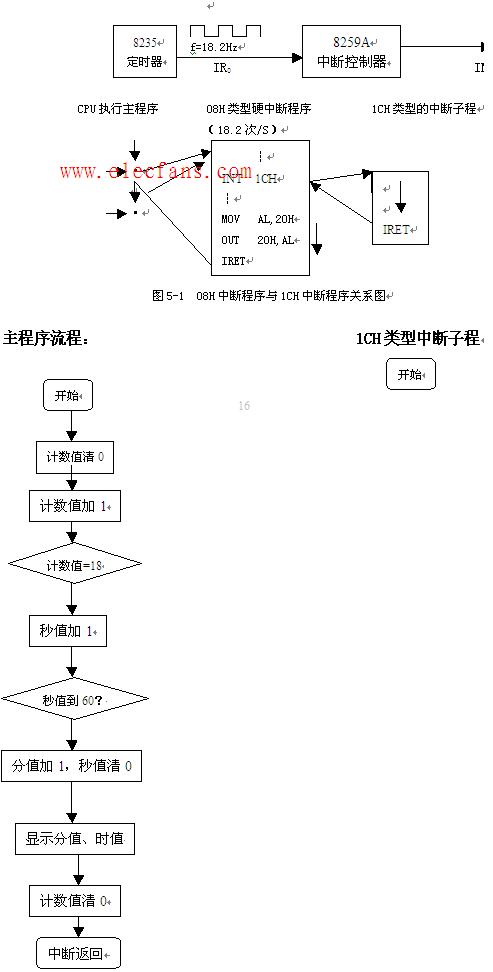

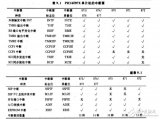

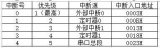

IBM PC/XT系統(tǒng)中可屏蔽的中斷源及其相應(yīng)的類型碼如表1所示。

表1 可屏蔽的中斷源及其相應(yīng)的類型碼

2.IBM PC/XT中系統(tǒng)保留的中斷

8088 CPU最多能處理256種不同的中斷,其中有5個(gè)保留為CPU專用;又有相當(dāng)一部分是由磁盤(pán)操作系統(tǒng)DOS保留為系統(tǒng)用的。

所有已經(jīng)保留的中斷類型,用戶就不能再使用了,但可使用的仍然有近200個(gè)中斷,這對(duì)于絕大部分用戶來(lái)說(shuō)已經(jīng)是足夠了。

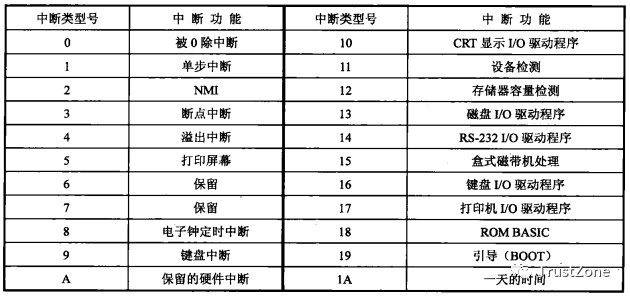

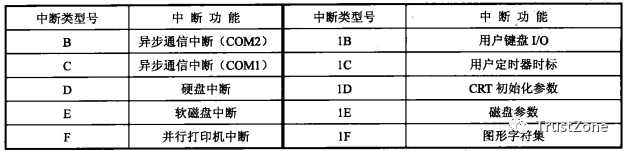

IBM PC/XT中保留的中斷(所用的DOS的版本號(hào)不同會(huì)有一些不同)中,前5個(gè)中斷類型是8088規(guī)定的專用中斷。BIOS的中斷類型號(hào)為0~1F,其功能如表2所示:

表2 IBM PC/XT中保留的BIOS中斷

?

在這些類型的中斷中,

??類型號(hào)8~F就是上述通過(guò)8259的八級(jí)硬件中斷;

??類型號(hào)5和10~1A是基本外部設(shè)備的輸入/輸出驅(qū)動(dòng)程序和BIOS中調(diào)用的有關(guān)程序;

??類型號(hào)1B和1C由用戶設(shè)定,1D~1F指向3個(gè)數(shù)據(jù)區(qū)域。

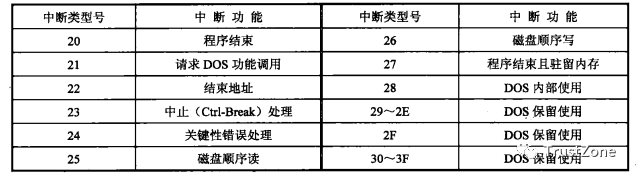

中斷類型號(hào)20~3F由DOS操作系統(tǒng)使用,用戶程序也可以調(diào)用其中的20~27號(hào)中斷。

這些中斷功能安排如表3所示。

表3 IBM PC/XT中保留的DOS中斷

40號(hào)以后的中斷類型可由用戶程序安排使用。

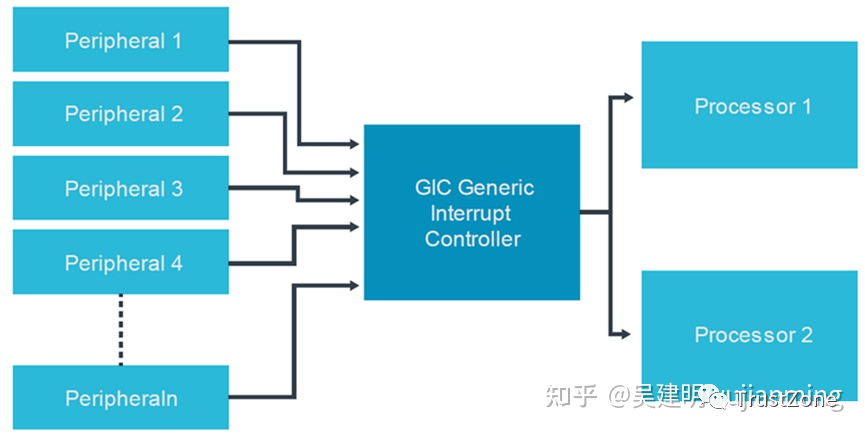

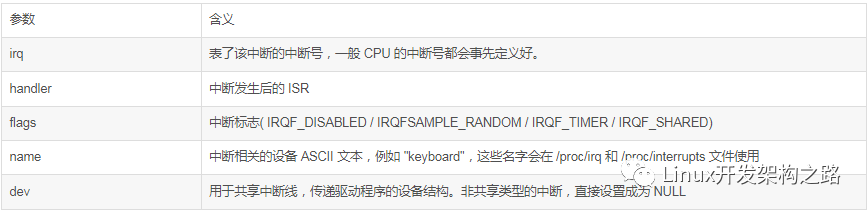

本章我們借助8088這個(gè)基礎(chǔ)的中斷控制器,讓我們對(duì)中斷的硬件電路有了基礎(chǔ)的認(rèn)知,這里我們來(lái)看兩個(gè)當(dāng)下非常常用和流行的中斷控制管理器8259A、APIC。

當(dāng)然ARM的GIC肯定也是會(huì)有的哦。

審核編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論