??? 關(guān)鍵詞:可編程邏輯器件,周期信號(hào)測(cè)試儀,ISP芯片,自頂向下

1 引 言

周期信號(hào)測(cè)試儀是直接用十進(jìn)制數(shù)字來顯示被測(cè)信號(hào)周期的一種測(cè)量裝置,它可以測(cè)量正弦波、矩形波、三角波等信號(hào)的周期。傳統(tǒng)的設(shè)計(jì)是采用標(biāo)準(zhǔn)邏輯器件(如TTL74系列、CMOS4000系列),再由這些器件和其他元件自上而下組成數(shù)字系統(tǒng),所用的元器件數(shù)量較多、體積大、功耗高、且可靠性差。本文采用現(xiàn)今流行的自頂向下(Top-Down)的設(shè)計(jì)方法,設(shè)計(jì)中選用Lattice公司生產(chǎn)的在系統(tǒng)可編程器件ispLSI1016,以周期信號(hào)測(cè)試儀電路系統(tǒng)的開發(fā)設(shè)計(jì)為例,說明在系統(tǒng)可編程邏輯器件實(shí)現(xiàn)數(shù)字系統(tǒng)的具體方法。

2 周期信號(hào)測(cè)試儀的工作原理及設(shè)計(jì)方案

2.1 工作原理

周期信號(hào)測(cè)試儀的基本原理是在被測(cè)信號(hào)的一個(gè)完整周期內(nèi),對(duì)標(biāo)準(zhǔn)時(shí)鐘脈沖進(jìn)行計(jì)數(shù)。考慮到測(cè)試的準(zhǔn)確性,被測(cè)信號(hào)的周期應(yīng)遠(yuǎn)大于標(biāo)準(zhǔn)時(shí)鐘脈沖的周期。假設(shè)標(biāo)準(zhǔn)時(shí)鐘脈沖周期為1μs,則計(jì)數(shù)器在被測(cè)信號(hào)的一個(gè)周期內(nèi)的計(jì)數(shù)值,就是被測(cè)信號(hào)的周期,單位為1μs。

2.2 測(cè)試儀的原理框圖

周期信號(hào)測(cè)試儀的原理框圖如圖1所示。測(cè)試儀主要由五位十進(jìn)制計(jì)數(shù)器、閘門控制電路和譯碼

顯示電路等組成。圖1中,S為被測(cè)信號(hào),ST為啟動(dòng)信號(hào),CLK為標(biāo)準(zhǔn)時(shí)鐘脈沖。

本設(shè)計(jì)采用模塊化設(shè)計(jì)方法,以原理圖與ABEL-HDL語言混合輸入方式實(shí)現(xiàn)設(shè)計(jì)。其中,控制電路模塊名為GCOL,采用原理圖方式輸入;計(jì)數(shù)器模塊名為COUNT,采用五個(gè)模10計(jì)數(shù)器級(jí)連實(shí)現(xiàn),模10計(jì)數(shù)器采用ABEL-HDL語言方式輸入;譯碼顯示電路模塊名為ALLOC,將計(jì)數(shù)器的計(jì)數(shù)值以掃描的方式在數(shù)碼管中顯示出來,采用ABEL-HDL語言方式輸入。圖2是周期信號(hào)測(cè)試儀的頂層原理圖。

3.1 控制電路設(shè)計(jì)

控制電路的底層原理圖如圖3所示。在被測(cè)信號(hào)ST發(fā)出后,被測(cè)信號(hào)S的第一個(gè)下降沿使G端輸出高電平,閘門開啟,允許標(biāo)準(zhǔn)時(shí)鐘脈沖通過,計(jì)數(shù)器開始計(jì)數(shù)。當(dāng)被測(cè)信號(hào)的下一個(gè)下降沿到來后,

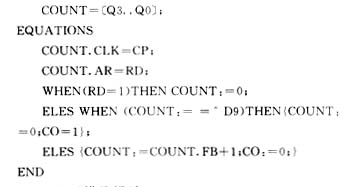

為了便于譯碼顯示,計(jì)數(shù)器輸出8421BCD碼共五位(為了使低頻范圍內(nèi)的信號(hào)均能得以測(cè)量)最大計(jì)數(shù)值為99999,用五個(gè)十進(jìn)制遞增計(jì)數(shù)器級(jí)連實(shí)現(xiàn),如圖4所示。設(shè)標(biāo)準(zhǔn)時(shí)鐘脈沖的周期為Tcp,則被測(cè)信號(hào)的最大測(cè)量周期Tmax=99999Tcp。

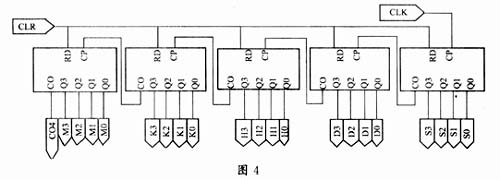

采用ABEL-HDL語言設(shè)計(jì)十進(jìn)制遞增計(jì)數(shù)器,其中,CP為計(jì)數(shù)器的計(jì)數(shù)脈沖,由通過閘門的標(biāo)準(zhǔn)時(shí)鐘脈沖提供,RD為計(jì)數(shù)器清零信號(hào),由系統(tǒng)的啟動(dòng)信號(hào)ST提供。模10計(jì)數(shù)器的ABEL源文件清單如下:

3.3 顯示模塊設(shè)計(jì)

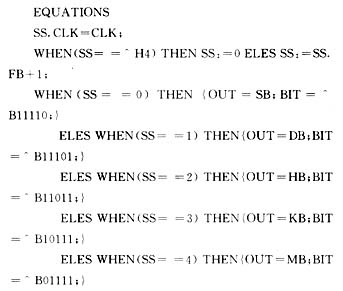

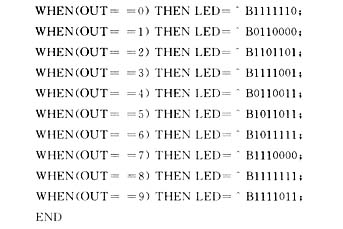

顯示模塊用來將五位十進(jìn)制計(jì)數(shù)器的計(jì)數(shù)值輸出至LED數(shù)碼管進(jìn)行顯示。于是,首先要完成BCD/七段碼的譯碼。為了節(jié)省可編程邏輯器件的I/O資源(這在復(fù)雜數(shù)字系統(tǒng)設(shè)計(jì)時(shí)尤為重要),5個(gè)數(shù)碼管采用掃描顯示的形式,即一次只驅(qū)動(dòng)一位數(shù)碼管顯示,5個(gè)數(shù)碼管輪流顯示,只要掃描的速度足夠快,由于視覺滯留的存在,眼睛就察覺不出閃爍。

??? 顯示模塊用ABEL語言描述如下:

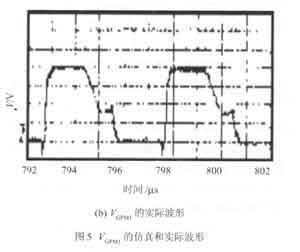

??? 對(duì)各資源文件從底層至頂層逐個(gè)編譯、調(diào)試之后,得到控制電路和計(jì)數(shù)器輸出的仿真波形,如圖5所示。圖中,SBusi(i=1、2、3、4、5、6)是選用總線方式顯示的計(jì)數(shù)器輸出,G為閘門信號(hào)。由圖可見,ST為高電平時(shí),系統(tǒng)清零。接著,被測(cè)信號(hào)S的下降沿使閘門開啟,G=1,計(jì)數(shù)器開始計(jì)數(shù),直至被測(cè)信號(hào)S的下一個(gè)下降沿,計(jì)數(shù)器才停止計(jì)數(shù),并保持測(cè)量結(jié)果。圖中,SBus5為計(jì)數(shù)器萬位,SBus4為計(jì)數(shù)器千位,SBus3為計(jì)數(shù)器百位,SBus2為計(jì)數(shù)器十位,SBus1為計(jì)數(shù)器的個(gè)位,SBus6為計(jì)數(shù)器總線輸出。

4 結(jié)束語

用可編程邏輯器件設(shè)計(jì)的數(shù)字電路系統(tǒng)具有電路簡(jiǎn)單、體積小的突出優(yōu)點(diǎn)。若將本設(shè)計(jì)中的閘門信號(hào)G換成高電平寬度為1秒的脈沖,而將時(shí)鐘脈沖CLK輸入端換成被測(cè)信號(hào)輸入,便能得到被測(cè)信號(hào)的頻率。利用CPLD/FPGA器件設(shè)計(jì)數(shù)字系統(tǒng)的最大特點(diǎn),是實(shí)現(xiàn)了硬件設(shè)計(jì)的軟件化,使得設(shè)計(jì)難度降低,修改十分方便,大大縮短了產(chǎn)品的開發(fā)設(shè)計(jì)周期。

2 徐志軍.大規(guī)模可編程邏輯器件及其應(yīng)用.成都:電子科技大學(xué)出版社,2000

3 閻 石.數(shù)字電子技術(shù)基礎(chǔ).北京:高等教育出版社,1998

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論