在最近幾年中日益流行在高性能嵌入式應用中使用現場可編程門陣列(FPGA)。FPGA已經被證明有能力處理各種不同的任務,從相對簡單的控制功能到更加復雜的算法操作。雖然FPGA在某些功能上比ASIC硬件具有時間和成本上的優勢,但在面向軟件應用中的FPGA比傳統處理器和DSP的優勢并沒有體現出來。這很大程度上是由于過去割裂了硬件和軟件開發工具和方法之間的關系。

然而最近FPGA在軟件設計工具方面的發展,及器件容量的持續增加為軟件開發者創造了新的環境。在這種環境下,FPGA可視為軟件編譯器的一個可能的目標。現在,工具能夠幫助軟件工程師利用FPGA平臺,同時在結合了傳統處理器(或軟處理器核)和FPGA的單一目標平臺上,幫助這些開發者利用其所具有的高度算法并行性。

基于FPGA的計算平臺,尤其是那些具有嵌入式“軟”處理器的平臺,有能力實現非常高性能的應用。通過使用最新一代的硬件/軟件協同設計工具,有可能使用多種面向軟件的設計方式作為FPGA設計過程的一部分。

使用基于FPGA的參考平臺

FPGA中使用嵌入式處理器的優勢之一是能夠在單個可編程器件上建立硬件/軟件開發對象——等效硬件參考平臺。 快速下載和測試新的軟件/硬件配置的能力也能大大提高設計率。通過使用嵌入式處理器作為測試生成器,單獨的硬件部件也可以快速地驗證功能。

這種快速原型平臺的典型例子是Altera公司提供的Nios開發包。Cyclone或Stratix FPGA中都包括這個工具包,除了高性能的Nios 32位軟核處理器核之外還包括多種硬件和軟件外設接口。在設計過程中可以選擇這種核,使用Altera SOPC Builder工具配置并下載到相應的FPGA中。板上本身的連接容許直接和各種不同的外部部件連接,從串口(RS232和USB)到Flash存儲器和網絡接口。

在開發過程中使用這種板子并結合Altera工具,容許嵌入式系統設計者用應用原型所需的部件(包括嵌入式處理器)組成目標平臺。然后,軟件開發者能夠關注應用本身,分析和試驗不同的硬件/軟件劃分方案。

權衡硬件和軟件資源

在一些高性能嵌入式應用中,從產品構建費用和開發成本考慮最佳的資源使用方案是混合處理器方案。在這種方案中非關鍵性能的功能由主處理器實現(它們可能是或不是嵌入式處理器核),而大計算量的部件是一個或多個DSP芯片、或者其它專用ASIC或FPGA。這種的解決方案通常需要豐富的硬件設計和工具的知識,但是在性能和成本方面上具有最佳的收益。

對于系統中的每個處理單元(即標準處理器、DSP、FPGA或ASIC),需要不同水平的專用技能。例如,雖然DSP是軟件可編程的,在工具上的初期投入小,但他們需要在DSP專門的設計技術方面有一些專門經驗,通常需要匯編級的編程技能。在另一方面,FPGA在設計和工具經驗上需要相對高的投入,在硬件設計語言作為主要的設計輸入方式時尤其如此。

然而FPGA和專用ASIC設計所需的經驗和工具投入相比,顯然FPGA在開發專用硬件上具有更低的風險。的確,相對于專用ASIC方案的簡單性和低風險的設計過程是選擇FPGA的關鍵因素。最近基于軟件的FPGA設計工具使這種設計過程獲得更大的效率。這反過來讓系統設計者和軟件應用開發者在實際的硬件上能夠更快地嘗試新的算法方式,使用迭代方式進行設計。

這種迭代方式重要好處是能夠一次改變一個單元(例如將關鍵的算法移至FPGA)。應用最初是完全用軟件進行原型設計,并驗證其正確性,然后由FPGA完成特定的功能,這是在每個步驟都要對系統重新進行驗證的硬件實現過程。這種方式被證實能大大地縮短調試時間,降低引入難以調試的系統錯誤的風險。

你如何在考慮“將設計的哪部分以硬件實現”上做出最明智的選擇?一個普遍采用的方式是從用C,Matlab,SystemC或其它一些軟件編程語言的軟件模型開始。隨著應用模型和部件算法的發展,設計者確定并發揮設計中的并行性(或重新設計算法),利用可編程硬件在建立并行結構方面的獨有能力。增加并行度通常轉化為增加硬件資源。使用軟件模型驗證假設,建立可重復的測試組,這些測試組可以作為模型,進一步提煉可以進行軟件和硬件編譯的內容。

混合軟硬件設計方法

現今如何開發混合軟件和硬件應用呢?如果設計是軟件驅動的(現今越來越多的設計是這樣),軟件或系統工程師從編寫代碼(如上所述)來建立系統原型。 另一種是,工程師用更高級的工具如Simulink(來自Mathworks),基于UML的工具或其它系統設計環境開始。 在這個過程中,系統設計者或軟件工程師將采用更高級的設計抽象以獲得最大的效率,但是可能獲得很低的性能結果。因為以這種方式自動選用的處理器類型是受限的,為性能轉換低級代碼的機會相對更少。有經驗的嵌入式開發者可能會進一步用匯編語言優化應用的各個部分,或使用專用處理器(即DSP芯片)來提高性能。硬件工程師可以參與優化面向FPGA和ASIC實現的設計中的那部分接口。

初始系統設計和劃分完成之后,需要最高性能的各個部分可以手工描述出來,交給硬件工程師。工程師為FPGA或ASIC部分編寫低層的HDL代碼,他們的設計生產率通常非常低(軟件工程師1/10或更少)。結果是系統速度增加了,但是代碼和最初的軟件代碼無法對應,設計周期不再一致,系統規格的改變可能很痛苦。

在這種情況下,系統設計者必須作為硬件/軟件仲裁者,指定硬件/軟件接口,鎖定設計反映設計的前期時間。一旦硬件開發認真地展開,可能幾乎沒有機會再次從整體上把握。

基于C的設計和原型工具加速開發過程

在上述的方式中,最終的設計是軟件和硬件源文件的組合。 一些需要軟件的編譯/調試工具流程,其它需要硬件設計流程和專業知識。 然而,隨著基于C的FPGA設計工具的出現,使得在大部分的設計中可以采用熟悉的標準C語言,尤其在那些本身就是實現算法的硬件電路。 后面的性能轉換可能會引入手工的硬件描述語言(HDL)取代自動生成的硬件(正如面向DSP處理器的源代碼通常用匯編重新編寫),但是因為設計直接從C代碼編譯成最初的FPGA實現,硬件工程師要參與性能轉換的時間會進一步提早至設計階段,系統可以用更高效率的軟件設計模式來進行設計。

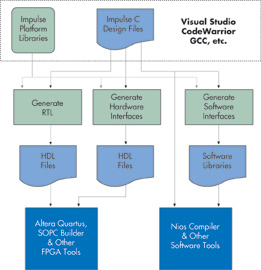

CoDeveloper工具(Impluse Accelerated Technologies提供)允許C語言的應用編譯后以FPGA網表形式建立硬件,包括允許描述高度并行和多過程應用描述所必須的C語言擴展。對于包括嵌入式處理器(如Altera的Nios軟核處理器)的目標平臺,CoDeveloper可以用來生成必要的硬件/軟件接口,及生成特定過程的低級硬件描述。

采用這種工具和硬件/軟件方式獲得成功的關鍵是軟件和硬件處理資源之間合理的劃分。好的劃分方案不僅要考慮給定算法部件對計算量的需求,而且要考慮數據帶寬需求。這是因為硬件/軟件接口可能是主要的性能瓶頸。

合理地利用高并行應用的編程模型也很重要。雖然它試圖用傳統編程方式如遠程過程調用(RPC)將特定功能交由FPGA處理,但是研究表明面向數據流的通信方式更有效率,它不可能引入阻塞或造成應用死鎖。在一些情況下,這意味著重新從整體上考慮設計,尋找新的方式對數據進行搬移和處理。這么做的結果是非常顯著的:通過增加應用級的并行性,充分利用可編程邏輯資源,這可能將使一般算法比純軟件實現提升幾個數量級。

在這種應用的開發過程中(或重新工程化),設計工具是可視化的,能調試多個并行過程的互連。工具有助于量化地給出劃分方式的結果,識別可能表示應用瓶頸的高數據吞吐量的區域。用戶可以在工具的幫助下,進行更詳細的分析和性能調整。

圖1,在應用調試和監視過程中連接硬件和軟件過程

設計實例:基于FPGA的圖像慮波器

為了演示這些工具如何用來把算法過程移至FPGA,我們以圖像慮波器為例,其中輸入數據流必須非常快速地處理,生成輸出數據流。這樣的問題可能涉及大量的計算,而且也是對帶寬要求非常高。

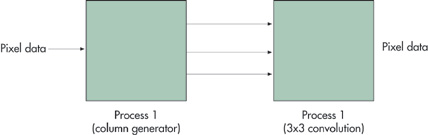

圖2說明一個簡單的圖像慮波器如何工作。在所示的示例中(邊緣檢測慮波器),尤其是3×3窗口的像素數據必須以流方式組合和處理。

圖2,圖像慮波器過程一次處理輸入圖像一個像素,在最近的八個像素進行卷積

有許多可能的方法實現這種算法。在本例中,兩個流水式硬件處理器用C描述完成這種功能:一個過程生成匹配源圖像的匹配行像素(以像素流讀取),同時第二個過程接受第一個過程的數據流的結果,將對每個像素窗口卷積,生成一個輸出圖像,用第二個過程中單一的卷積像素流表示。這個過程和流用Impulse C庫(見附文《Impluse C編程模型》)提供的C兼容的流I/O例程來聲明和讀/寫。

因為算法是用標準C(外加Impulse C庫)描述的,我們能從軟件設計(用Microsoft Visual Studio開發)開始,它在桌面仿真環境下完成圖像算法。這種設計將兩種硬件過程和圖像卷積功能結合到軟件臺設計中(它可以編譯,并以基于PC的臺式機應用或運行在Nios處理器中的嵌入式應用運行),它從TIFF格式文件中讀取數據進行處理。這種設計可以用標準桌面調試工具和CoDeveloper Application Monitor進行設置和運行。在這種方式下,算法結果可以在編譯到FPGA平臺之前進行驗證。

編譯為硬件

用標準桌面C開發工具仿真它的功能之后,我們準備用Altera Stratix開發原型板,在混合FPGA/處理器目標上實現該應用。Altera Nios開發包包括所有編譯和綜合至FPGA所需的硬件和軟件(包括自動生成的硬件過程的HDL源文件和表示軟件過程的C源代碼)。Altera提供的軟件結合Impulse CoDeveloper,為我們提供了從C語言編譯和執行測試應用所需的一切。

我們第一步是為圖像濾波器本身生成硬件。為了達到這一目的,我們從CoDeveloper工具中選用Altera Nios Platform Support Package,處理相關的Impulse C源文件。這將產生大約1200行的RTL和相關的硬件/軟件接口源文件。

接下來,用Altera Quartus工具建立新的項目,生成包括必要外設的Nios處理器核(用Altera的SOPC Builder)。CoDeveloper輸出生成的硬件和軟件文件給Quartus。使用Altera的框圖工具,我們通過Avalon片內總線將生成的硬件過程和Nios處理器相連。

整個系統用Altera Quartus綜合。應用的軟件部分(主要由測試生成器和客戶功能組成,包括組函數)也導入Quartus項目,用所包含的Nios編譯器編譯。

最后,用Altera工具生成bit文件,通過提供的并口電纜下載到平臺上。在這個平臺按預期要求上電和運行。

在這個例子中,顯式流水的兩個圖像濾波器過程和由CoDeveloper C自動為硬件編譯器生成的流水在每兩個FPGA時鐘周期獲得最佳的單像素圖像處理速率,相當于大約10ms完成整個512×512圖像的處理速度。

當然,在FPGA上任何算法的性能是取決于I/O因素及算法本身。在我們的圖像濾波器測試方案中,圖像數據從Nios上運行的測試生成器通過Avalon片內互連傳送到生成的FPGA硬件上,這樣可以獲得比上述最大像素速率低得多的有效吞吐量。另一個算法版本中,像素數據直接從FPGA硬件接口傳送和讀取,這樣做的結果會最接近最佳的結果。因此考慮帶寬的限制是非常重要的。象CoDeveloper這樣的工具可以更容易和更快地進行這方面的評估和實驗。

附文:Impluse C編程模型

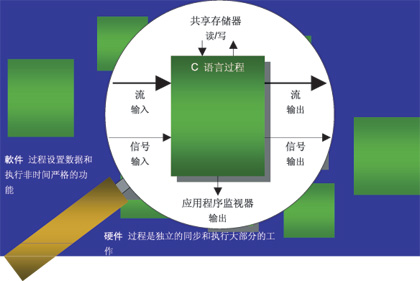

建立軟件和硬件相結合的設計需要對并行編程技術有所了解。為了幫助建立高度并行的混合硬件/軟件應用,Impulse C庫包括了設置和管理多個獨立過程的功能,它可以通過數據流、信號和可選的共享存儲資源相連接。

Impulse C編程模型(概念上和1980年C.A.R.Hoare描述的通信時序處理模型類似)提供了對硬件/軟件劃分和同步的系統級控制,同時允許用標準C構造編寫和自動優化獨立過程。

圖a,Impulse C編程模型:通信主要通過數據流(映射為生成硬件中的FIFO),其它需要同步的信號,本地存儲器。

使用Impulse C庫功能,C語言可用來描述高度并行的應用,具有最小的軟件編程復雜度,同時具有用標準C開發環境下編譯和調試的能力。例如,使用Impulse C庫功能,一個簡單的圖像濾波器可以用如下的代碼風格描述(實際算法省略)

這設計方法的結果是底層硬件平臺的實際情況被抽象,用戶(他可能是有經驗的C程序員,但幾乎沒有硬件設計知識)不必學習硬件設計方法,就可以描述和運行混合軟件/硬件應用。

電子發燒友App

電子發燒友App

評論