摘要:APA150是Actel公司推出的第二代基于Flash的可編程FPGA器件系列ProASIC Plus中的一種,非常適合替代ASIC用于航空、消費電子、工業(yè)控制、網(wǎng)絡(luò)和通信市場。文章介紹了APA150的主要特點、內(nèi)部結(jié)構(gòu)、主要性能參數(shù),給出了APA150在通信系統(tǒng)設(shè)計中的應(yīng)用實例。

關(guān)鍵詞:APA150 FPGA ASIC Flash

1 概述

APA150是Actel公司推出的第二代基于Flash(閃存)的可編程FPGA(Field Programable Gate Array,現(xiàn)場可編程門陣列)器件ProASIC Plus系列中的一種。該系列器件兼具ASIC(專用集成電路)的性能和FPGA的靈活性于一身,因此,可非常經(jīng)濟地替代A-SIC用于航空、消費電子、工業(yè)控制、網(wǎng)絡(luò)和通信市場。ProASIC Plus系列產(chǎn)品的主要特點如下:

●系統(tǒng)內(nèi)可重復(fù)編程;

●非易失,采用0.22μm標(biāo)準(zhǔn)CMOS工藝,內(nèi)置Flash單元,具有安全的非易失代碼存儲功能,上電即可運行,無需額外配置PROM存儲器;

●高度保密,使用者可編程設(shè)置多位密鑰以阻止外界自行讀取或更改器件的配置;

●功耗低?芯片核心電壓為2.5V;

●具有與ASIC類似的精細顆粒架構(gòu),支持流行的ASIC工具流程,因而可縮短產(chǎn)品上市時間,便于轉(zhuǎn)換到ASIC。

?

2 內(nèi)部結(jié)構(gòu)和工作原理

APA150主要由邏輯單元塊、嵌入式RAM塊、I/O塊和可編程連線等幾個部分構(gòu)成,塊與塊之間用不同等級的連接線和Flash開關(guān)相連。

?

邏輯單元是ProASIC Plus器件的基本組成單元,用以實現(xiàn)基本的邏輯功能。APA150內(nèi)部有6144個邏輯單元,每個邏輯單元有三個輸入端和一個輸出端。通過適當(dāng)編程配置Flash開關(guān)的狀態(tài),可將邏輯單元設(shè)置成為具有三個輸入的、除了異或功能之外的任意邏輯功能塊,例如與非門、具有清零或置位端的鎖存器或D觸發(fā)器等。多個邏輯單元互連還可以實現(xiàn)更復(fù)雜的邏輯功能。一般的復(fù)雜性和隨機性設(shè)計可在邏輯單元中實現(xiàn),但為了提高硅片的利用率和器件的性能,一些較為復(fù)雜的功能應(yīng)通過內(nèi)嵌的隨機存儲單元來完成。

APA150內(nèi)嵌16個共36kbits的RAM塊(256×9),這些RAM塊可以非常方便地實現(xiàn)一些規(guī)模不太大的FIFO、雙端口RAM等功能。每個RAM塊均包含如下3個部分:

(1)數(shù)據(jù)區(qū);

(2)總線,包括9位輸入數(shù)據(jù)總線(第9位是奇偶極性位)、讀和寫各8位地址總線和輸出數(shù)據(jù)總線;

(3)讀/寫控制,讀和寫可以獨立編程配置為同步或異步工作方式,以適應(yīng)電路設(shè)計的靈活性和時序安排。

另外可以根據(jù)設(shè)計要求級聯(lián)或堆疊多個RAM塊,以得到更大的寬度或深度。因為這些片內(nèi)存儲器的讀、寫比片外RAM快得多。

I/O塊主要用于提供管腳到內(nèi)部信號線的接口?并負責(zé)輸入輸出的電氣特性控制。通過編程配置I/O塊可使I/O管腳具有輸入、輸出、雙向緩沖或三態(tài)驅(qū)動等功能,其內(nèi)部結(jié)構(gòu)如圖1所示。將控制上拉電阻接到每個I/O管腳可以防止器件在非正常工作時管腳出現(xiàn)懸浮;通過控制輸出信號的電壓擺率可滿足低噪聲或高轉(zhuǎn)換速度的要求。如將VDDP接到電源,那么,當(dāng)VDDP為2.5V時,輸入電壓或輸出高電平為2.5V;而當(dāng)VDDP為3.3V時,輸入電壓可為2.5V/3.3V,輸出電平則與2.5V或3.3V系統(tǒng)兼容。

APA150器件內(nèi)部遍布一系列四個級別水平和垂直的連接線:其中超高速本地線用于連接相鄰邏輯單元;有效長線則可實現(xiàn)遠距離和高扇出連接,其長度可以跨越1、2或4個邏輯單元;另外,高速甚長線常用于甚長或甚高扇出連接,它可以跨越整個器件;高性能全局線常用以連接全局管腳到內(nèi)部的邏輯單元,如分配作時鐘、復(fù)位的管腳等。

諸多連接線與邏輯單元或其它塊的連接狀態(tài)由上電即可在系統(tǒng)內(nèi)編程的Flash開關(guān)來決定,其結(jié)構(gòu)如圖2所示。其中,浮動?xùn)诺淖饔檬峭ㄟ^充電或放電來設(shè)定連接兩個金屬線路之間的開關(guān)狀態(tài)。由于可編程器件或開關(guān)器件未發(fā)生任何物理變化,因此通過材料分析探測不到任何結(jié)果。發(fā)生變化的只有浮動?xùn)诺?a target="_blank">電子數(shù),因此,基于Flash的APA150 比采用其它工藝(如反熔絲)的FPGA更難以反求和復(fù)制。

3 管腳功能和主要參數(shù)

3.1 管腳功能

APA150的封裝形式有100腳TQFP(薄型四方扁平封裝)、208 腳PQFP(塑料方型扁平式封裝)、456 腳PBGA(塑料球柵陣列封裝)以及144、256腳FBGA(微間距球柵陣列)封裝等形式。使用時可根據(jù)所設(shè)計的系統(tǒng)選擇適當(dāng)?shù)姆庋b。下面以100 腳的TQFP為例介紹其管腳功能,具體如表1所列。

表1 APA150的管腳功能

| 管 腳 名 | 管? 腳? 號 |

管? 腳? 描? 述 |

| VDD | 17,37,68,89 | 接2.5V,作為芯片電源 |

| VDDP | 26,39,40,76,87,100 | 接2.5V或3.3V,作為I/O驅(qū)動電壓 |

| I/O |

2~8,18~24,27~36,41~46, 57~59,69~74,77~85,90~99 |

可用作輸入、輸出、三態(tài)或雙向緩沖,作輸入、輸出時兼容TTL和CMOS電平,不用的輸入管腳應(yīng)接上位電阻 |

| GL | 11,16,60,65 | 全局管腳,可作為低時滯時鐘或其它全局信號輸入,也可以作為普通I/O使用 |

| NPECL | 13,63 | 除了標(biāo)準(zhǔn)I/O口,APA150芯片還提供低電壓正射極耦合邏輯(LVPECL)標(biāo)準(zhǔn)的差分I/O接品,NPECL、PPECL分別為負、正極性輸入,二者比較的結(jié)果將送給內(nèi)部鎖相環(huán)。不用時空接 |

| PPECL | 15,61 | |

| TMS | 49 | 測試模式選擇,用于控制邊界掃描電路 |

| TCK | 47 | 測試時鐘,同時是邊界掃描的時鐘輸入(最大為10MHz) |

| TDI | 48 | 測試數(shù)據(jù)輸入,作為邊界掃描的串行輸入 |

| TDO | 54 | 測試數(shù)據(jù)輸出,作為邊界掃描的串行輸出 |

| TRST | 55 | 測試復(fù)位輸入,作為邊界掃描的異步復(fù)位端,低電平有效 |

| RCK | 56 | 運行時鐘,編程時用來取代不可靠的TCK |

| VPP | 52 | 編程器電源,范圍是0~16.5V,也可以空接,Actel推薦空接或連接至VDDP |

| VPN | 53 | 編程器電源,范圍是0~-13.8V,也可以空接,Actel推薦空接或接地 |

| AVDD | 14,62 | 內(nèi)部鎖相環(huán)電源腳,接2.5V電壓,它與地之間應(yīng)有一個合適的去耦電容以減小噪聲;不用內(nèi)部鎖相環(huán)時該管腳空接 |

| AGND | 12,64 | 內(nèi)部鎖相環(huán)地端 |

| GLMA | 10,66 | 多元全局管腳,可用此管腳作為內(nèi)部鎖相環(huán)需要外部環(huán)回時的輸入,另外也可以作為普通I/O使用 |

| GND | 1,9,25,38,40,51,67,75,86,88 | 接地 |

3.2 主要參數(shù)

ProASIC Plus系列共有七種產(chǎn)品,其密度從75000到1百萬系統(tǒng)門。其中APA150的主要特點如下:

●具有150000個系統(tǒng)門,邏輯單元為6144個;

●內(nèi)嵌36kB的雙端口SRAM的2個鎖相環(huán)?PLL?內(nèi)核;

●最大支持242個用戶I/O? I/O電壓有3.3V和2.5V兩種可供選擇;

●支持3.3V、32bits、50MHz的PCI總線,系統(tǒng)時鐘最高頻率為32MHz;

●工作溫度:民用溫度范圍為0~70℃,工業(yè)級溫度范圍為-40~85℃。

4 應(yīng)用實例

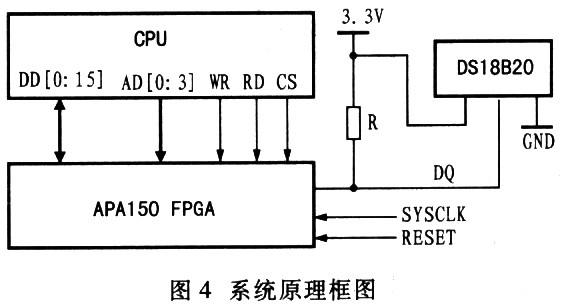

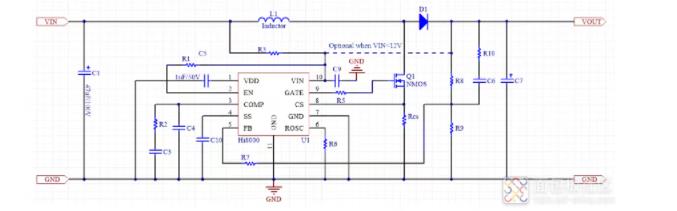

圖3是筆者以APA150為核心器件設(shè)計的CAN總線復(fù)接系統(tǒng)。CAN(Controller Area Network,控制器局域網(wǎng))是一種多主方式的串行通訊總線,在工業(yè)系統(tǒng)中具有廣泛的應(yīng)用。但是它的直接通信距離和通信速率是一對矛盾。本系統(tǒng)借助FPGA /VHDL技術(shù),把15路125kbps的CAN信號復(fù)接成2.048Mbps的E1信號,從而利用現(xiàn)有的時分復(fù)用通信線路或光纖實現(xiàn)了高速、遠距離傳輸。

PCA82C250是CAN總線的物理接口芯片。16-bit電平轉(zhuǎn)換芯片74LCX16245用于實現(xiàn)15路、5V CAN信號與APA150器件的3.3V輸入/輸出間的相互轉(zhuǎn)換。APA150則用于完成2MHz的E1信號與15路CAN信號間的分接和復(fù)接。而MC100LVELT22與MC100LVELT23則用于實現(xiàn)APA150的低壓TTL信號與3.3V低壓PECL信號間的轉(zhuǎn)換。光電轉(zhuǎn)換器件采用C-13-155-T3-SSC3B,這是一個3.3V、155MHz、單模光纖收發(fā)一體模塊。本系統(tǒng)采用基于EDA技術(shù)的自頂向下(TOP-DOWN)的設(shè)計方法。本設(shè)計所采用的工具是Actel公司的集成設(shè)計環(huán)境Libero V2.2,它支持VHDL、Verilog 語言的頂層設(shè)計,同時支持原理圖、狀態(tài)機及流程圖等輸入,而且還集成了業(yè)界領(lǐng)先的設(shè)計工具,如仿真和設(shè)計驗證軟件ModelSim、綜合軟件Synplify、布放軟件Designer R1-2002等。

本系統(tǒng)的核心器件采用基于Flash的APA150。與SRAM工藝的FPGA相比,APA150具有如下優(yōu)點:

(1)成本低,APA150的價格低于8美元,而且由于APA150具有非易失性,因此不需要用于存儲編程數(shù)據(jù)的PROM,從而節(jié)約了成本;

(2)安全性高,一經(jīng)編程鎖定就難以反求,而SRAM FPGA易于復(fù)制,安全性不足;

(3)功耗低,其功耗僅是基于SRAM的FPGA產(chǎn)品的1/3到1/2。

與ASIC相比,本系統(tǒng)的研制周期較短,設(shè)計成本亦較低,而且具有可重復(fù)編程性,因而大大提高了設(shè)計的靈活性。

電子發(fā)燒友App

電子發(fā)燒友App

評論