WCDMA文章列表:WiMAX與HSDPA優(yōu)勢比較?

USB:淺談USB閃存盤與PIC微控制器系統(tǒng)的連接

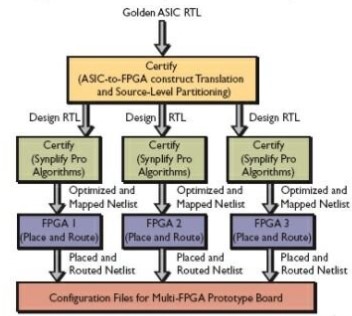

3G知識普及:3G研發(fā)歷史本文將介紹,如何在專業(yè)的驗證軟件Certify 的幫助下,實現(xiàn)快速有效的用多片FPGA 來進(jìn)行ASIC 設(shè)計驗證。

前言

在現(xiàn)在復(fù)雜的ASIC 設(shè)計中,校驗(Verification)是最大的瓶頸。隨著先進(jìn)的半導(dǎo)體工藝技術(shù)不斷前

進(jìn),隨之帶來的是ASIC 設(shè)計規(guī)模和設(shè)計復(fù)雜度的飛速增長,這使得傳統(tǒng)的軟件仿真工具已經(jīng)無法完全解決驗證的問題。而且隨著越來越多的需要處理大量實時數(shù)據(jù)的應(yīng)用(如視頻)出現(xiàn),驗證技術(shù)就要求能夠在接近實時頻率的條件下進(jìn)行驗證。現(xiàn)在越來越多的ASIC 設(shè)計者自己設(shè)計FPGA 驗證板來進(jìn)行ASIC 設(shè)計驗證。用FPGA 驗證ASIC 的好處是可以使軟件的開發(fā)調(diào)試和ASIC 的開發(fā)調(diào)試并行的進(jìn)行。

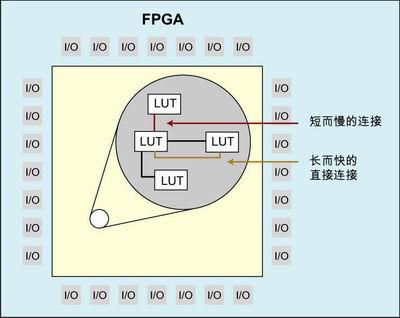

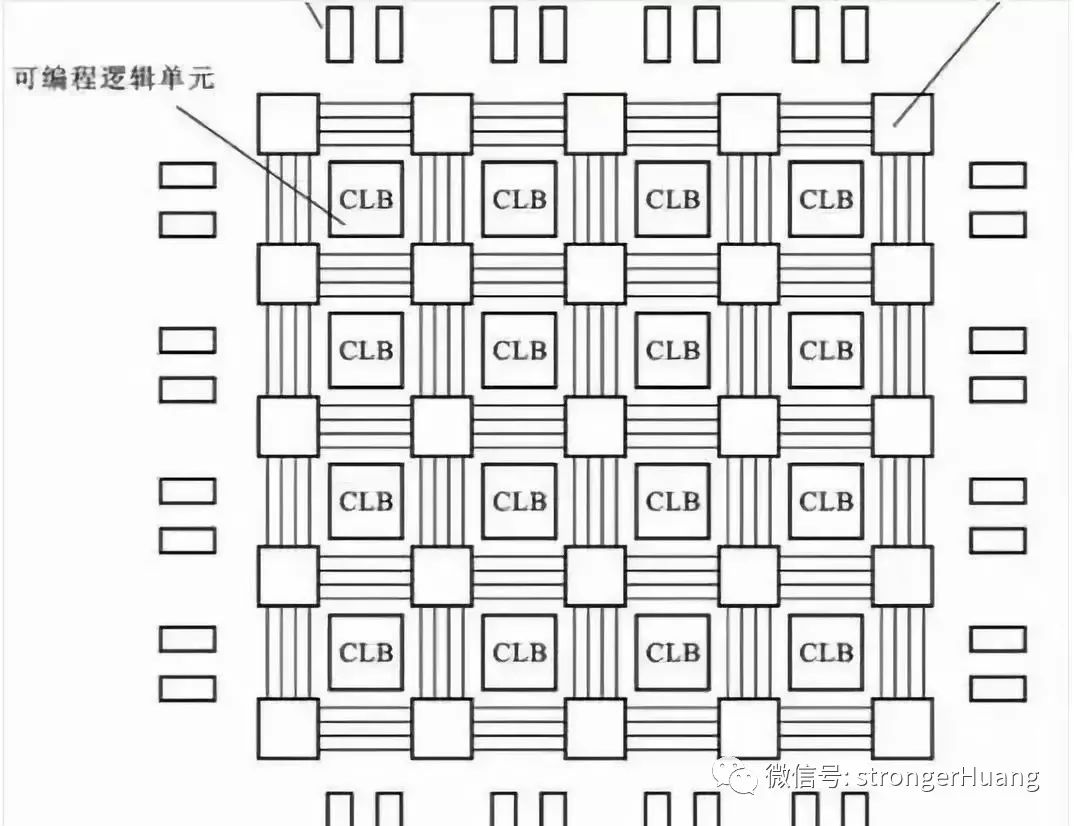

ASIC 的設(shè)計者在用FPGA 做驗證和調(diào)試的時候會面臨很多挑戰(zhàn)。一個最大的問題就是即使是:最大

容量的FPGA 和復(fù)雜的ASIC 相比還是太小。這意味著設(shè)計者必須把他們的ASIC 設(shè)計分割到幾塊FPGA 中。

在作分割和FPGA 綜合的時候,沒有工具幫他們做出好的分割決定,也很難確定驗證板的參數(shù)和設(shè)計。這樣設(shè)計者只能單調(diào)乏味的在分割、綜合、板上實現(xiàn)幾個步驟中重復(fù),浪費大量的時間。

Certify 是SYNPLICITY 公司的新一代設(shè)計軟件,它就是針對用FPGA 做ASIC 驗證的設(shè)計。Certify

結(jié)合了RTL 多片分割和業(yè)界最好FPGA 綜合技術(shù)。它是業(yè)界的第一個也是唯一一個針對使用多片F(xiàn)PGA 做ASIC 驗證的設(shè)計工具。

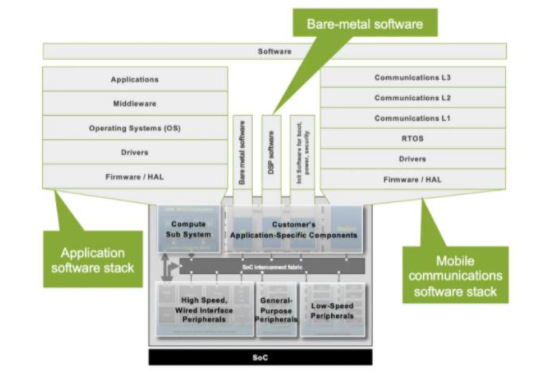

SOC(片上系統(tǒng))ASIC 的驗證方法ASIC 設(shè)計者面臨著一系列的壓力。他們的設(shè)計要達(dá)到最高的集成度,并且要能滿足最新的工藝技術(shù),達(dá)到最大的容量。而且他們也不得不要考慮Time-To-Market 的時間,所以要盡快的得到功能完全準(zhǔn)確、可以工作的芯片。由于推向市場時間的巨大壓力,SOC 芯片還要有軟件的部分,因此同樣不容許因為芯片功能沒有達(dá)到準(zhǔn)確而導(dǎo)致拖延軟件的開發(fā)和調(diào)試。軟硬件的合作開發(fā)和調(diào)試是必須的。

EDA 工業(yè)就是為了滿足對新工具和新方法的需要。高級的描述語言和高級的庫極大的提高了設(shè)計者的生產(chǎn)力。越來越多的IP 核允許設(shè)計者使用增強(qiáng)功能的元件快速可靠的設(shè)計很大的設(shè)計。瓶頸來自于驗證,因為ASIC 投產(chǎn)之前必須是正確的。對百萬門級片上系統(tǒng)的ASIC 設(shè)計,每次投片的NRE 費用是巨大的。因此,在功能沒有被驗證之前不去投片是可以理解的。而且隨著設(shè)計容量的增加,充分仿真需要測試向量的數(shù)量也增加的更快。所以現(xiàn)在的ASIC 設(shè)計周期中,驗證占了50%強(qiáng)。預(yù)計將來兩年的設(shè)計中,驗證會達(dá)到70%。

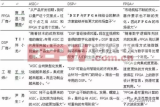

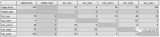

對SOC 的設(shè)計者來說,有許多的驗證方法。下圖是一個比較:

傳統(tǒng)的仿真技術(shù)已經(jīng)遠(yuǎn)遠(yuǎn)不能滿足現(xiàn)在復(fù)雜的ASIC 驗證對速度的需要。軟件仿真器和定制的軟件模型非常普及,但僅僅它們已不能滿足用戶的需要。硬件加速器有比較好的性能,但是貴而且使用不方便,并且對于具有高速數(shù)據(jù)處理的一些應(yīng)用,如MPEG 視頻處理等,仍然不能達(dá)到所需的性能。而現(xiàn)在世面上更加昂貴而且更難于使用的硬件仿真器,也不能滿足現(xiàn)在的ASIC 設(shè)計的性能需要。

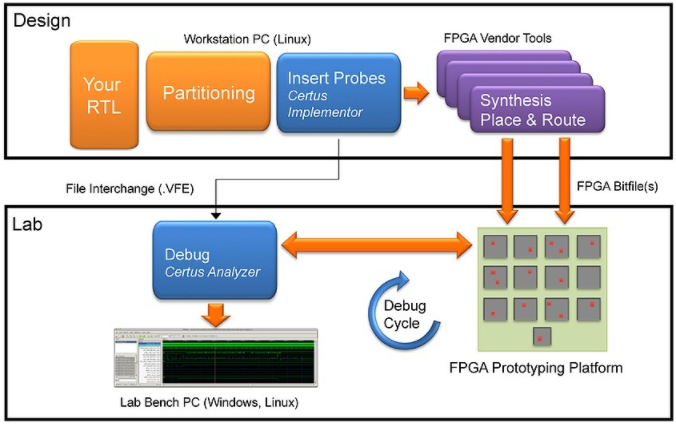

所以現(xiàn)在ASIC 設(shè)計者更多的使用定制或者是可重構(gòu)的驗證環(huán)境來做系統(tǒng)驗證。驗證設(shè)計的流程如下

圖所示:

綜合/分割的瓶頸用FPGA 作原型驗證提供了很多好處,但同時也帶來了新的難題。把整個設(shè)計分割到多片F(xiàn)PGA 中經(jīng)常會花費很長周期,從而也延遲了整個的開發(fā)周期。圖2 顯示了定制的原型驗證傳統(tǒng)的設(shè)計流程。在流程中綜合和分割是分開的,互不關(guān)聯(lián)。綜合的時候不會考慮到設(shè)計如何分割到多片的FPGA 中,因此,不會達(dá)到所希望的速度。分割的方法也不會反饋,不會對利用率和系統(tǒng)性能帶來影響。因此,設(shè)計者會在分割和綜合之間反復(fù)多次。每次的反復(fù)都會浪費時間,結(jié)果增加了驗證的時間,降低了生產(chǎn)力。當(dāng)對源代碼改動的時候,這個過程有可能再會重復(fù)多次。更大的問題是仔細(xì)認(rèn)真作出的分割不會在對多個FPGA 綜合的時候用到而優(yōu)化系統(tǒng)性能。這有可能降低驗證的性能,還會迫使你使用更多更大的更昂貴的器件。

所以要真正解決問題,就需要把FPGA 分割和綜合結(jié)合起來,并且在RTL 級就完成分割。結(jié)合Certify軟件就能做到這樣。這避免了反復(fù)的浪費時間,加快了原型驗證,縮短了驗證的開發(fā)周期,使產(chǎn)品更快的推向市場。

Certify 是建立在Synplify 綜合技術(shù)上的,Synplify 的核心算法包括了適合每種FPGA 特殊結(jié)構(gòu)的綜合算法,它的時序驅(qū)動的綜合算法使設(shè)計可以達(dá)到盡可能高的系統(tǒng)速度。

這種綜合算法的內(nèi)核被擴(kuò)展到了運用獨特的分割驅(qū)動綜合算法的Certify 中。有了這種方法,綜合過程就基于一個確定的分割。在多片F(xiàn)PGA 之間的時間預(yù)算自動的被包含在分割驅(qū)動的綜合算法中。

這個方法是Certify 解決方案的核心,提高了驗證的性能,并使得設(shè)計者可以在幾乎相當(dāng)于實時的速度中對其設(shè)計進(jìn)行驗證。

Certify 的綜合引擎,基于已經(jīng)驗證的Synplify 技術(shù),可以處理超過100 萬門的設(shè)計。它同樣有能力進(jìn)行快速綜合。工作在450MHZ,1G 內(nèi)存的PC 平臺上的綜合測試,Cerity 綜合分割100 萬門的設(shè)計到幾個FPGA 器件中不多于9 小時。

Certify 用戶接口

Certify 提供了簡單易用的圖形用戶界面(如圖3),用戶可以快速的產(chǎn)生合理的分割,并可以估計驗

證的速度和效率。Certify 利用成功的HDL 分析器,自動由HDL 代碼產(chǎn)生RTL 圖,并將二者都在窗口顯示。

其他的窗口顯示系統(tǒng)驗證板和FPGA 的圖形說明。

Certify 中要首先要估計設(shè)計中每個模塊的面積和I/O 數(shù)。這個估計是通過調(diào)用估計模式下的綜合引擎

實現(xiàn)的;估計的結(jié)果作為RTL 塊圖的標(biāo)注顯示。

用戶通過從RTL 圖中選擇塊并把他們拖曳到目標(biāo)FPGA 器件中實現(xiàn)分割。Certify 直接為每個器件提供I/O 和面積利用率的百分比的反饋信息。這就使用戶可以完全控制分配及分割結(jié)果的快速反饋。然后設(shè)計者可以利用這個信息把選中的模塊分配到最合適的FPGA 中去,同時又保證分割的結(jié)果對面積和I/O 利用而言是合理的。

當(dāng)分配完成后,Certify 利用物理分割信息驅(qū)動綜合算法。這些選擇會影響電路的實現(xiàn)。因此當(dāng)把片內(nèi)

和片外的延遲及板子上的延遲時計算在內(nèi)時,時序中的關(guān)鍵路徑能夠被優(yōu)化。

不改變RTL 源代碼而進(jìn)行邏輯復(fù)制

為了增加驗證性能并將FPGA 之間的互連最少,Certify 讓設(shè)計者不改變HDL 源代碼而復(fù)制邏輯。例如在圖4-a 中,解碼器的16 位輸出驅(qū)動三片F(xiàn)PGA 中的邏輯。板子上的總線布線會導(dǎo)致系統(tǒng)速度降低,會產(chǎn)生版圖設(shè)計的問題并需要大量的利用珍貴的I/O 資源。

相反的,在圖4b 中,解碼器可以被復(fù)制在三個FPGA 中的每一個。盡管這樣做會增加總的芯片面積,卻減少了板子之間的互聯(lián)并大大的減少了I/O 的需求。在Certify 中,這個復(fù)制可以通過簡單的在RTLCertify 用戶接口Certify 提供了簡單易用的圖形用戶界面(如圖3),用戶可以快速的產(chǎn)生合理的分割,并可以估計驗證的速度和效率。Certify 利用成功的HDL 分析器,自動由HDL 代碼產(chǎn)生RTL 圖,并將二者都在窗口顯示。其他的窗口顯示系統(tǒng)驗證板和FPGA 的圖形說明。

Certify 中要首先要估計設(shè)計中每個模塊的面積和I/O 數(shù)。這個估計是通過調(diào)用估計模式下的綜合引擎

實現(xiàn)的;估計的結(jié)果作為RTL 塊圖的標(biāo)注顯示。

用戶通過從RTL 圖中選擇塊并把他們拖曳到目標(biāo)FPGA 器件中實現(xiàn)分割。Certify 直接為每個器件提供I/O 和面積利用率的百分比的反饋信息。這就使用戶可以完全控制分配及分割結(jié)果的快速反饋。

Certify 包含了強(qiáng)有力的“what-if”分析,用戶可以通過它快速分析分割對面積和I/O 的影響。通過在設(shè)計模塊上點鼠標(biāo)右鍵調(diào)用“what-if”分析。利用選中的模塊和所有以前分割的模塊之間的互連情況,Certify 計算把選中的模塊到分配到驗證板上每個FPGA 時對面積和I/O 的影響,并把這個信息反饋給用戶。然后設(shè)計者可以利用這個信息把選中的模塊分配到最合適的FPGA 中去,同時又保證分割的結(jié)果對面積和I/O 利用而言是合理的。

當(dāng)分配完成后,Certify 利用物理分割信息驅(qū)動綜合算法。這些選擇會影響電路的實現(xiàn)。因此當(dāng)把片內(nèi)

和片外的延遲及板子上的延遲時計算在內(nèi)時,時序中的關(guān)鍵路徑能夠被優(yōu)化。不改變RTL 源代碼而進(jìn)行邏輯復(fù)制為了增加驗證性能并將FPGA 之間的互連最少,Certify 讓設(shè)計者不改變HDL 源代碼而復(fù)制邏輯。例如解碼器的16 位輸出驅(qū)動三片F(xiàn)PGA 中的邏輯。板子上的總線布線會導(dǎo)致系統(tǒng)速度降低,會產(chǎn)生版圖設(shè)計的問題并需要大量的利用珍貴的I/O 資源。相反的,在圖4b 中,解碼器可以被復(fù)制在三個FPGA 中的每一個。盡管這樣做會增加總的芯片面積,卻減少了板子之間的互聯(lián)并大大的減少了I/O 的需求。在Certify 中,這個復(fù)制可以通過簡單的在RTL視Figure 3

用戶通過從RTL 圖中選擇塊并把他們拖曳到目標(biāo)FPGA 器件中實現(xiàn)分割。Certify 直接為每個器件提供I/O 和面積利用率的百分比的反饋信息。這就使用戶可以完全控制分配及分割結(jié)果的快速反饋。

Certify 包含了強(qiáng)有力的“what-if”分析,用戶可以通過它快速分析分割對面積和I/O 的影響。通過在設(shè)計模塊上點鼠標(biāo)右鍵調(diào)用“what-if”分析。利用選中的模塊和所有以前分割的模塊之間的互連情況,Certify 計算把選中的模塊到分配到驗證板上每個FPGA 時對面積和I/O 的影響,并把這個信息反饋給用戶。

然后設(shè)計者可以利用這個信息把選中的模塊分配到最合適的FPGA 中去,同時又保證分割的結(jié)果對面積和I/O 利用而言是合理的。

當(dāng)分配完成后,Certify 利用物理分割信息驅(qū)動綜合算法。這些選擇會影響電路的實現(xiàn)。因此當(dāng)把片內(nèi)

和片外的延遲及板子上的延遲時計算在內(nèi)時,時序中的關(guān)鍵路徑能夠被優(yōu)化。

不改變RTL 源代碼而進(jìn)行邏輯復(fù)制

為了增加驗證性能并將FPGA 之間的互連最少,Certify 讓設(shè)計者不改變HDL 源代碼而復(fù)制邏輯。例如在圖4-a 中,解碼器的16 位輸出驅(qū)動三片F(xiàn)PGA 中的邏輯。板子上的總線布線會導(dǎo)致系統(tǒng)速度降低,會產(chǎn)生版圖設(shè)計的問題并需要大量的利用珍貴的I/O 資源。

相反的,在圖4b 中,解碼器可以被復(fù)制在三個FPGA 中的每一個。盡管這樣做會增加總的芯片面積,

卻減少了板子之間的互聯(lián)并大大的減少了I/O 的需求。在Certify 中,這個復(fù)制可以通過簡單的在RTL 視圖中拖曳解碼器到版圖視圖中的每個FPGA 中去實現(xiàn)。

由于原型的主要目的是對ASIC 進(jìn)行驗證,僅僅因為驗證的目的設(shè)計者是很不愿意改變HDL 源代碼的。事實上,很多機(jī)構(gòu)中,驗證小組被嚴(yán)格的禁止對源代碼進(jìn)行改動。利用傳統(tǒng)的綜合和分割建立原型是不可能不改變源代碼而在FPGA 中復(fù)制邏輯的。這就導(dǎo)致了效率低的-有時是不可行的原型驗證。只有Certify可以使設(shè)計者不改變源代碼而復(fù)制邏輯,只需要把目標(biāo)從RTL 視圖中拖曳到目標(biāo)器件就可以了。

不改變RTL 源代碼而建立探測點傳統(tǒng)的綜合和分割的方法中,說明一個要被輸出到FPGA 邊界作為探測點的信號,需要改變HDL 源代碼。只有Certify 可以使設(shè)計者不改變HDL 代碼而指定探測點,只要把信號拖曳到和FPGA 關(guān)聯(lián)的管腳分配表上即可。

重復(fù)的設(shè)計流程驗證的一個主要目的是快速的找到并修改原設(shè)計中的錯誤。為了支持重復(fù)的驗證-調(diào)試-修改-驗證-調(diào)試這樣的周期,驗證的工具必須最佳化。Certify 是這個設(shè)計流程的最佳工具。除了為設(shè)計中的每個FPGA 建立門級網(wǎng)表,Certify 也為每個FPGA 輸出HDL 源代碼。修復(fù)設(shè)計中bug 的重復(fù)過程通常被限制到設(shè)計中為數(shù)不多的模塊中去。通過Certify,只有需要重新實現(xiàn)的FPGA 才會被影響,這樣就減少了增加設(shè)計改變所需要的時間。

關(guān)于IP 核ASIC 設(shè)計,特別是被認(rèn)為是芯片上系統(tǒng)的一個明顯趨勢是設(shè)計的重用性,即那些不論是自己生產(chǎn)還是買回來的IP 核。Certify 可以容易的使用它們。

如果有RTL 代碼,就可以放入設(shè)計過程中去,并在一個或多個FPGA 上驗證。另一種方法是把它當(dāng)作FPGA外面的東西放入到系統(tǒng)中。Certify 中,這將被認(rèn)為是一個黑盒子。這個器件在版圖中被定義,然后在分割過程中被例化。同樣的方法可以例化標(biāo)準(zhǔn)的功能模塊例如UART 和存貯器。

靈活選擇實現(xiàn)方式Certify 的輸出為測試板產(chǎn)生一個頂層的網(wǎng)表,為每個FPGA 產(chǎn)生一個可以進(jìn)行布局布線的優(yōu)化網(wǎng)表,這就使得使用者可以定義一個定制驗證板,并通過布線互聯(lián)器件例如I-Cube 建立驗證板。它也可以被用于流行的來自Aptix 的產(chǎn)品System Explorer 的輸入。System Explorer 把Certify 創(chuàng)立的網(wǎng)表作為輸入,在驗證板上放置器件,配置可編程的板子之間的互聯(lián),然后調(diào)用FPGA 布局布線工具執(zhí)行每個器件。

Certify 支持FPGA 供應(yīng)商最流行的FPGA 器件。在Certify 的第一個發(fā)行版本中支持的有Altera 的Flex10k,Apex,ApexII,Xilinx 4k 以及Xilinx Virtex 系列。利用Certify 可以用最流行的FPGA 器件以及幾乎所有的驗證板為用戶提供了最靈活的實現(xiàn)方案選擇。

Certify 將RTL 多片分割和FPGA 綜合技術(shù)結(jié)合起來,是第一個也是唯一的著眼于ASIC 驗證和利用多片F(xiàn)PGA 進(jìn)行驗證的綜合產(chǎn)品。Certify 的獨特的分割驅(qū)動綜合方法使得設(shè)計者達(dá)到最快的驗證速度。Certify大大簡化了ASIC 驗證,減少了驗證開發(fā)時間,并使其快速市場化。

電子發(fā)燒友App

電子發(fā)燒友App

評論