摘要: 從PCI時序分析入手,重點闡述了PCI通用的狀態機設計,說明了用VHDL語言來實現本PIC通信狀態機的軟件設計以及進行MaxPlusII驗證的程序和方法。用該方法所設計的接口既可支持PCI常規傳輸,又可支持PCI猝發傳輸。

關鍵詞: PCI時序 CPLD器件 狀態圖 VHDL語言 PCI猝發傳輸

用CPLD設計所構成的CPI接口系統具有簡潔、可靠等優點,是一種行之有效的設計途徑。很多技術雜志和網站上,都有不少用CPLD設計PCI常規傳輸系統的文章。但用這些方法在MzxPlusII、Fundition等環境下進行模擬仿真時,其產生的時序往往與PCI規范有很大出入。雖然 Altera 等公司推出PCI核可以直接使用,但這樣的內核占用CPLD資源較多,且能適配的器件種類少,同時價格也高,在實際設計應用中有很大的局限性。因此,使用通用型CPLD器件設計簡易型PCI接口有很大的現實意義。在Compact接口的CPLD設計中,筆者根據PCI總線傳輸時序來進行狀態機構造,并使用VHDL語言進行功能模擬和定時分析,從而達到了預期目的。用該方法設計的CPLD-PCI接口既可支持PCI常規傳輸,也可支持PCI猝發傳輸,而且在系統編程和下載器件方面,效果也都很好。

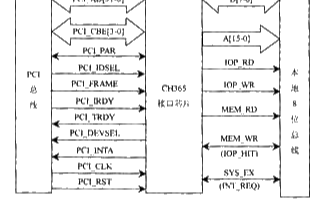

1 典型的CPLD-PCI接口模型簡介

用CPLD作PCI接口所構成的系統模型如圖1所示。這里,CPLD/FPGA用于完成PCI主/從傳輸時序的邏輯構成與變換,并對雙口RAM進行適當操作。在整個系統的設計中,CPLD常常使用PCI總線的33MHz時鐘,雙口RAM常常選用高速器件來簡化PCI傳輸的邏輯設計。

2 PCI總線傳輸時序分析

PCI總線傳輸至少需要40多條信號線,包括數據/地址線、接口控制線、仲裁、總線命令及系統線等。每次數據傳輸均由一個地址脈沖和一個或幾個數據脈沖組成。一次傳輸一個地址和一個數據的稱為常規傳輸;一次傳輸一個地址和一批數據的稱為猝發傳輸。常用的控制信號有:幀同步信號FRAME、主設備準備好信號IRDY、從設備準備好信號TRDY、從設備選通信號DEVSEL、命令/字節信號C/BE等。圖2 和圖3分別給出了PCI單數據段和猝發操作時的讀寫時序。

分析PCI總線的傳輸時序,可以看出,PCI總線傳輸有以下幾個顯著特點:

(1)每次數據傳輸時首先傳出地址和命令字,從設備一般可從地址中確定是不是對本機的訪問,并確定訪問的首地址;而從設備則從命令字中識別該訪問是讀操作還是寫操作;

(2)讀寫訪問只有在信號IRDY、TRDY、DEVSEL都為低狀態時才能進行;

(3)猝發傳輸通常需要通過邏輯來實現地址的自動遞加;

(4)主從設備中任一方沒有準備好,操作中都需要能夠引起等待狀態插入的活動;

(5)系統通常在幀同步信號FRAME的下降沿誘發數據傳輸,而在上升沿指明只有一個數據或只剩下一個數據;

(6)讀操作比寫操作多一個中間準備過程。

圖2

3 基于CPLD的狀態機設計

3.1 狀態機的構造

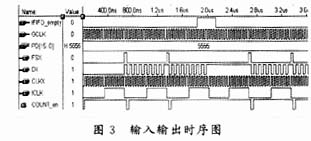

根據對上述時序圖的分析,完成一個簡易PCI總線傳輸需要設計六個狀態:S0~S5,其中狀態S0標識PCI總線空閑時期;狀態S1標識地址與總線命令識別階段;狀態S2標識讀操作入口的準備階段;狀態S3標識讀/寫訪問周期;狀態S4標識最后一個數據傳輸階段;狀態S5標識操作中的等待時期。

3.2 狀態功能的確定

各狀態所應執行的功能如下:

狀態S0~S2用于對PCI總線置高信號TRDY和DEVSEL;對雙口RAM則置高片選信號CS,以使讀/寫信號處于讀狀態,此時地址呈現三態。此外,在S1態還應依據地址信號來確定是不是對本機的選擇,并識別是不是讀或寫操作。

狀態S3~S4用于對PCI總線置低信號TRDY和DEVSEL;對雙口RAM則產生片選信號CS、讀或寫信號,同時確定適當的讀寫訪問地址。

狀態S5用于對PCI總線置低信號TRDY和DEVSEL;并且對雙口RAM置高片選信號CS,以使讀/寫信號處于讀狀態,此時地址呈現三態。

3.3 狀態變化的確定

根據對PCI總線傳輸時序的分析,影響各個狀態相互轉化的因素是:幀同步信號FRAME、主設備準備好信號IRDY、從設備選擇信號CS-MAP、讀識別信號READ以及寫識別信號WRITE。這里,可用CS-MAP、READ、WRITE來標識狀態S1產生的中間識別信號。

圖3

需要注意,在狀態S1時要寄存收到的首地址,而在狀態S3變化時要適時進行地址遞增。

還要注意狀態機設計時產生的容錯問題,以便在非設計狀態下能夠無條件回到空閑態S0。

由于采用的是高速雙口RAM,并且規劃分開了RAM兩側的寫操作區域,因此可以認為:RAM是可以任意訪問的。

3.4 狀態圖的規劃

綜上所述便可得出如圖4所示的設計規劃圖。

4 VHDL語言的描述

設計時,使用三個進程和幾個并行語句可實現整個CPLD的功能:一個進程用于完成從設備及其讀寫操作的識別;一個進程用于完成操作地址的獲取與地址的遞增;第三個進程完成狀態機的變化。用幾個并行語句完成操作信號的產生時,需要注意,各狀態所完成的功能要用并行語句實現,不能再用進程,否則就會引起邏輯綜合的麻煩,有時甚至根本不能綜合。整 個程序如下:

LIBRARY ieee;

USE ieee.std_logic_1164.All;

USE ieee.std_logic_unsigned.ALL;

ENTTTY cpci IS

PORT(clk,rst,frame,irdy:IN STD_LOGIC;

ad_high : IN STD_LOGIC_VECTOR(31 downto 24);

ad_low : IN STD_LOGIC_VECTOR(12 downto 0);

c_be : IN STD_LOGIC_VECTOR(3 downto 0);

trdy,devsel:OUT STD_LOGIC;

cs, r_w :OUT STD-LOGIC;

addr: OUT STD_LOGIC_VECTOR(12 downto 0);

END cpci;

ARCHITECTURE behave OF cpci IS

SIGNAL addr_map : STD_LOGIC_VECTOR(12 downto 0);

SIGNAL read,write,cs-map:STD_LOGIC;

TYPE state_type IS(s0,s1,s2,s3,s4,s5);

SIGNAL state: state_type;

BEGIN

Identify: PROCESS(clk)- -讀、寫、從設備的識別

BEGIN

IF rising_edge(clk)THEN

IF c_be=X"6"AND ad_high=X"50"AND state=s1

HTEN read < = '0'; - -讀

write < = '1';

cs_map < ='0';

ELSIF c_be=X"7"AND ad_high= X"50"

AND state=s1 THEN

read < = '1'; - -寫

write < = '0';

cs_map < ='0';

ELSIF state=s0 THEN

read < = '1';

write < = '1';

cs_map < ='1';

END IF;

END IF;

END PROCESS;

Addr_count:PROCESS (clk) - -操作地址的獲取與地址的遞增

BEGIN

IF falling_edge(clk)THEN

IF state=s1 THEN addr_map< =ad-low;

ELSIF state=s3 THEN addr_map< =addr-map+1;

END IF;

END IF;

END PROCESS;

- - 操作信號的產生

addr < = addr-map WHEN state=s3 OR state=s4

ELSE "ZZZZZZZZZZZZZ"

trdy < = '0' WHEN state=s3 OR state=s4 OR state=s5

ELSE '1';

devsel < = '0'WHEN state=s3 OR state=s4 OR state=s5

ELSE'1';

cs < ='0'WHEN state=s3 OR state=s4 ELSE '1';

r-w < =NOT clk WHEN write='0'AND (state=s3 OR state=s4)ELSE'1';

state-change:PROCESS(clk,rst) - - 狀態機的變化

BEGIN

IF rst='0'THEN state < = s0;

ELSIF falling-edge(clk)THEN

CASE state IS

WHEN s0 = >

IF frame='1'AND irdy='1'THEN state < = s0;

ELSIF frame='0' AND irdy= '1' THEN state < = s1;

END IF;

WHEN s1 = >

IF cs_map='1'OR (read='1'AND write ='1')

THEN state < = s0;

ELSIF irdy='1'AND read='0' THEN state < =s2;

ELSIF frame='0'AND irdy='0'AND write='0'

THEN state < = s3;

ELSIF frame='1'AND irdy='0'AND write='0'

THEN state < = s4;

END IF;

WHEN s2 = >

IF frame='1'AND irdy='1'THEN state < = s0;

ELSIF frame='0'AND irdy='0'AND read='0'

THEN state < = s3;

ELSIF frame='1'AND irdy='0'AND read='0'

THEN state < = s4;

END IF;

WHEN s3 = >

IF frame='1'AND irdy='1'THEN state < = s0;

ELSIF frame='0' AND irdy= '1' THEN state < = s5;

ELSIF frame='1'AND irdy='0' THEN state < =s4;

ELSIF frame='0' AND irdy= '1' THEN state < = s3;

END IF;

WHEN s4 = >

ELSIF frame='1'AND irdy='0'THEN state < = s4;

END IF;

WHEN s5 = >

IF frame='1'AND irdy='1'THEN state < = s0;

ELSIF frame='0' AND irdy= '0'THEN state < = s3;

ELSIF frame='1'AND irdy='0' THEN state < =s4;

ELSE state < = s5;

END IF;

WHEN OTHERS = > state < = s0;

END CASE;

END IF;

END PROCESS state_change;

END behave。

圖5

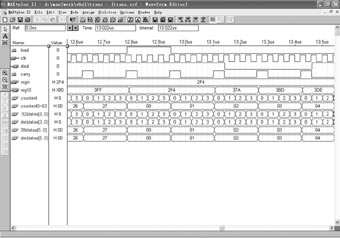

5 MaxPlusII的驗證

設計CPLD時,可使用MaxPlusII軟件來進行邏輯綜合、功能模擬與定時分析。本例選用 Altera 的Max7000系列在系統可編程器件EPM7064SLC84-5。圖5所示是其讀寫訪問的仿真波形圖。

電子發燒友App

電子發燒友App

評論