1.簡介

本文所述的Reed Solomon編譯碼器編譯器能夠產生多種代碼形式的Reed Solomon的宏編碼器和譯碼器,這些代碼形式在參數部分詳細說明,一旦確定了代碼,可以對頂層HDL代碼以Altera 10K器件進行編譯。通常,編碼器編譯包括裝配和布線不超過一分鐘,而譯碼器編譯也只要五分鐘。這個應用程序也能夠產生測試代碼,可以驗證所生成內核的功能。

有三種Reed Solomon 編譯碼器的宏單元,一個是編碼器,另兩個是譯碼器它們是為不同規模/性能要求而優化的。性能較低的譯碼器,也依據分立譯碼器,接收一個碼字,計算差錯位置和值,寫回糾正后的碼字。性能較高的譯碼器,或流譯碼器,連續讀取和寫回碼字。流譯碼器或多或少地多使用一些邏輯,但需要更多的存儲空間,由于譯碼模塊之間進行流水線作業因此性能有很大程度的改善。

2.參數

以下參數定義了Reed Solomon碼字。

A.每個碼字的符號總數

每個碼字有多達2m-1個符號,也就是N。對Reed Solomon編譯器,N必須大于3,受最小的R+1限制。

B.校驗符號數目

編譯器支持4到40個校驗符號,或者R,受最大N-1校驗符號限制。

C.每個符號的位數

雖然Reed Solomon碼字可以為每個符號定義任意位數m,但編譯器的有效范圍從4到8比特。

D.不可約域多項式

域多項式,或域(field),指定了有限域中元素的級數。域的大于由m給定,每個域大小僅受限于有效域多項式數目。域多項式通常由系統規范確定,但是對于給定的m,編譯器能夠使用任何有效的域多項式。另外FIELD.EXE應用程序可以根據任意m計算所有有效的域。

E.生成多項式的第一個根

域多項式描述的符號內各位之間的關系,而生成多項式則描述了符號之間的關系。生成多項式在編碼期間生成校驗符號。編譯器支持0到2m-1-R之間的genstart。

3.設計流程

使用第二節中描述的參數,DOS應用程序將生成用于HDL結構框架設計的插件。用于生成編碼器的應用程序是ENCRSV3,生成譯碼器的應用程序是DECRSV3。可以按第二節所列的參數順序調用這兩個應用程序。應用程序會檢驗并確認參數處于有效范圍內,確認這些參數組合能夠生成有效的RS碼。應用程序還可以為這個RS編譯碼產生測試代碼,馬上就可以進行功能測試了。

程序運行之后,就能夠以獨立的設計或作為更大系統設計的一部分編譯所需功能的頂層HDL。

4.資源要求

所需資源的數量主要取決于m和R。每個碼字的符號數目不會影響譯碼器所需邏輯,因為接收的符號存儲在Altera 10K器件的嵌入存儲塊中。

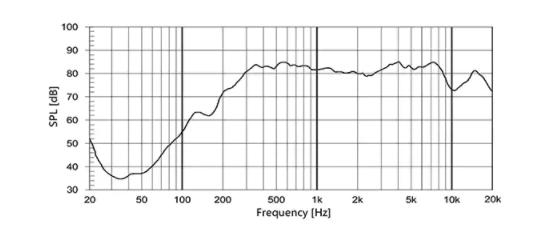

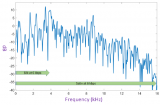

編碼器需要很少的邏輯單元,而不需要存儲塊。編碼器的規模隨m和R線性變化。圖1為當m=8時,編碼器規模和R的關系。

雖然對給定的m的R,分立和流式譯碼器之間有大略的線性關系,但它們的規模隨m和R呈幾何增長。除了邏輯之外,分立譯碼器需要兩個嵌入存儲塊,而流式譯碼器需要五個存儲塊。若生成多項式的第一個根大于零,那么需要更多的存儲塊。圖2為m=8時,譯碼器規模和R的關系。

5.計算系統性能

編碼器的性能取決于m和R,以及器件的布線和裝配。 通常絕大部分的參數組合都可以實現40MHz系統時鐘速度,這說明編碼器的性能一般高于譯碼器。當編碼每個時期你生一個符號,吞吐速率和系統時鐘速率一樣。

通常絕大部分的參數組合都可以實現40MHz系統時鐘速度,這說明編碼器的性能一般高于譯碼器。當編碼每個時期你生一個符號,吞吐速率和系統時鐘速率一樣。

譯碼器的系統性能取決于系統時鐘速率以及所選的RS碼字。處理一個碼字所需的最小和最大時鐘速率,取決于N和R。如果接收碼字的差錯小于最大差錯數目t,譯碼所需的時鐘周期小于最大周期數。若接收的碼字多于t個差錯,那么最大時鐘周期后,譯碼器輸出接收的碼字,并把DECFAIL標志置位。

分立和流式譯碼器均有規模/性能(size/performance)權衡參數speed,它可以設置為"single"或"double"。實現"double"(加倍)內部處理單元無需很多的額處邏輯,不多于2m2個邏輯單元。速度參數也會提高分立譯碼器的性能,但可能會影響流譯碼器的吞吐量。

當N為碼字的最大允許值(2m-1)時,譯碼器的吞吐量最大。

A.分立譯碼器

當speed為"single"時,分立譯碼器的最大延如下,其中包括讀取接收的碼字和寫回糾正后的碼字。

3N+3R 2 (1)

對于較大的R值,那么延遲主要決定于第二項。

當speed是"double"時,分立譯碼器的最大延遲為:

3N+1.7R 2 (2)

對于R小于14,譯碼可能需要額外延遲40個周期。若R值更大,延遲可能稍微短一些。

圖3為不同參數N,R以及speed對分立譯碼器吞吐量的影響。對于較小的R,N和speed譯碼器的性能沒有多大影響。

隨著R的增加,N對系統吞吐量變得非常重要。這是因為系統吞吐量是測算單位時間內符號的數目,隨著R增加,N對延遲的影響微不足道。

對于較大的R,譯碼器的吞吐量和N成正比。隨著R的增加,speed參數的影響簡單地由上述(1)和(2)式決定。當speed設置為"double"時,性能提升50%。

B.流式譯碼器

當speed是"single"時,流式譯碼器每個碼字的最大延遲為:

max{(N+R),(3R2)} (3)

當speed是"double"時,流式譯碼器每個碼字的最大延遲為:

max{(N+R),(1.7R2)} (4)

此外,和分立譯碼器一樣,延遲隨R變化很小(最多40個周期)。

圖4說明了不面N和R對性能的影響。R越大,增加N或者把speed參數設置為"double"的影響越大。

對特定的m,系統時鐘頻率保持相對穩定,隨m只有輕微變化。

6.結論

高性能的Reed Solomon 編碼器和譯碼器可以采用完全參數化的工具方便地進行設計。這些Reed Solomon核能綜合到可編程邏輯中,可以生成和標準器件(ASSP)面樣級數,或性能更優的編譯碼器。

在綜合之前要給定RS的參數,估計核的大小和性能。

電子發燒友App

電子發燒友App

評論