摘要: 給出一種基于FPGA的新型諧波分析儀的設(shè)計方案。在該方案中,采用FPGA實現(xiàn)快速的FFT運(yùn)算,使用實時操作系統(tǒng)結(jié)合Ethernet芯片實現(xiàn)TCP/IP協(xié)議直接接入局域網(wǎng),并給出實現(xiàn)的設(shè)計實現(xiàn)。

關(guān)鍵詞: FPGA Verilog HDL Nios 諧波分析儀 實時操作系統(tǒng)

引言

隨著節(jié)能技術(shù)和自動化技術(shù)的推廣,電力電子裝置如變頻設(shè)備、變流設(shè)備等,容量日益擴(kuò)大,數(shù)量日益增多,使電網(wǎng)中的諧波污染日益嚴(yán)重,給電力系統(tǒng)和各類用電設(shè)備帶來危害,輕則增加能耗,縮短壽命,重則造成用電事故,影響安全生產(chǎn)。因此,消除諧波污染,把諧波含量控制在允許范圍內(nèi),已成為主管部門和用電單位的共同奮斗目標(biāo)。

目前,電力系統(tǒng)中的諧波源,不但類型多,而且分布廣,用戶電網(wǎng)中的諧波電流可能來自本身的非線性設(shè)備,也可能來自外線路,如不加以區(qū)分將給諧波治理造成困難。因此進(jìn)行諧波治理之前,必須要了解電網(wǎng)中諧波的次數(shù)及其含量,即必須進(jìn)行諧波的測試。諧波測量是諧波問題的一個重要分支,它是諧波問題研究的主要依據(jù),也是研究分析問題的出發(fā)點。

當(dāng)前諧波測量的主要方式有3種。

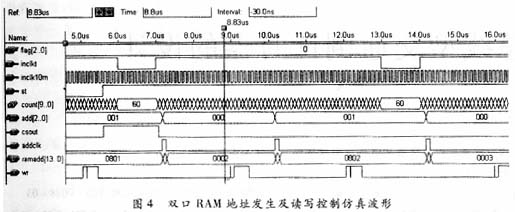

圖1

(1)采用模擬濾波器的諧波測量

最早的諧波測量是采用模擬濾波器實現(xiàn)的。即采用帶阻濾波器將基波分量濾波,得到諧波分量;或采用帶通濾波器得出基波分量,再與被檢測量相減得到諧波分量。該檢測方法的優(yōu)點是電路結(jié)構(gòu)簡單,造價低,輸出阻抗低,品質(zhì)因素易于控制。但也有很多缺點,如精度不高、誤差較大等。

(2)基于傅里葉變換的諧波測量

隨著計算機(jī)和微電子技術(shù)的發(fā)展,基于傅里葉變換的諧波測量是當(dāng)今應(yīng)用最多也是最廣的一種方法。它的核心理論建議在傅里葉變換的基礎(chǔ)上。根據(jù)傅里葉變換理論,將模擬信號采信變成離散化數(shù)字序列信號后,輸入微型計算機(jī)進(jìn)行傅里葉變換,計算得到基波和頻率為基波頻率整數(shù)倍的多次諧波的幅值和相位,然后將計算獲得的數(shù)據(jù)顯示在屏幕上或存放在磁盤中供將來統(tǒng)計使用。

(3)利用小波分析方法的諧波測量

小波分析作為調(diào)和分析的重大進(jìn)展,克服了傅里葉變換的頻域完全局部性,而在時域完全無局部性的缺點,即它在頻域和時域同時具有局部性。通過對含有諧波的電流信號進(jìn)行正交小波分解,利用多分辨的概念,將低頻段(高尺度)上的結(jié)果看作不含諧波的基波分量。基于這種算法,可以利用軟件構(gòu)成諧波檢測環(huán)節(jié),同時由于其計算速度快,能快速跟蹤諧波的變化。小波變換應(yīng)用在諧波測量方面尚處于初始階段。

目前市場主流的諧波測量儀器均基于快速傅里葉變換理論基礎(chǔ)。將輸入的模擬量電流電壓通過A/D采樣環(huán)節(jié)變換成離散的數(shù)字量,然后進(jìn)行快速傅里葉變換,計算獲得基波和各次諧波的復(fù)數(shù)值,然后根據(jù)國家標(biāo)準(zhǔn)計算相應(yīng)的諧波指標(biāo)并顯示最終結(jié)果。基于FFT的諧波時域測量儀器一般采用兩種實現(xiàn)方式:使用工業(yè)PC機(jī)或者采用高檔嵌入式系統(tǒng)。兩類實現(xiàn)方式性能可靠、運(yùn)算快速、技術(shù)成熟,是目前市場的主流產(chǎn)品。其缺點在于成本過高、難以擴(kuò)展輸入通道數(shù)、運(yùn)算時消耗系統(tǒng)資源大。就廣大電力系統(tǒng)用戶而言,對成本低廉、運(yùn)算快速、易于進(jìn)行通道擴(kuò)展的諧波分析儀有強(qiáng)烈的市場需求。

本文給出了種基于FPGA的新型諧波測量儀,該儀器集成了A/D采樣單元、FFT運(yùn)算處理單元、顯示單元和網(wǎng)絡(luò)通信單元。系統(tǒng)使用FPGA內(nèi)部實現(xiàn)的處理器Nios作為系統(tǒng)的嵌入式處理器,來控制14位高速A/D采樣芯片、FFT運(yùn)算核和實現(xiàn)網(wǎng)絡(luò)通信功能、顯示功能。其FFT運(yùn)算處理單元核心為基于FPGA的FFT運(yùn)算核,采用先進(jìn)的多層并行流水線技術(shù),可以在200μs內(nèi)完成1024點的標(biāo)準(zhǔn)單精度浮點數(shù)FFT運(yùn)算,理論上可以實現(xiàn)8路工頻輸入信號的FFT運(yùn)算處理;A/D采樣單元使用14位高速A/D采樣芯片實現(xiàn)8路信號掃描采樣功能,并利用鎖相環(huán)實現(xiàn)同步采樣;顯示單元為LCD顯示屏;網(wǎng)絡(luò)通信基于Ethernet和RS485,使用RFC 1600規(guī)范。該系統(tǒng)成本低廉,易于擴(kuò)展、處理能力強(qiáng)大、可測量8路輸入信號50次以內(nèi)諧波,精度可以達(dá)到GB/T 17626.7規(guī)定的A級測量儀器精度要求。

1 系統(tǒng)總體設(shè)計

系統(tǒng)總體結(jié)構(gòu)如圖1所示。

該系統(tǒng)從結(jié)構(gòu)上分為CT/PT變送單元、A/D采樣單元、FFT運(yùn)算處理單元、控制單元、顯示單元和網(wǎng)絡(luò)接口單元。CT/PT變送單元負(fù)責(zé)將輸入的150~390V電壓信號線性變換為5mA的電流信號,輸入的0~15A電流信號線性變換5mA的電流信號,并對信號進(jìn)行相位補(bǔ)償;A/D采樣單元對從CT/PT變送單元輸出的模擬信號每周波采樣256點,精確變換成14位的數(shù)字量;FFT運(yùn)算處理單元負(fù)責(zé)處理A/D采樣單元輸出的數(shù)字量,進(jìn)行256點FFT變換運(yùn)算;顯示單元負(fù)責(zé)顯示系統(tǒng)的全部顯示信息;網(wǎng)絡(luò)接口單元負(fù)責(zé)提供網(wǎng)絡(luò)通信的硬件實現(xiàn)電路;控制單元負(fù)責(zé)系統(tǒng)各個單元的控制,如控制A/D采樣單元的采樣頻率和采樣的啟動及停止、PLL電路的輸出頻率計算、鍵盤輸入的響應(yīng)、網(wǎng)絡(luò)通信的軟件實現(xiàn)、FFT運(yùn)算處理單元的控制和數(shù)據(jù)傳輸?shù)取?

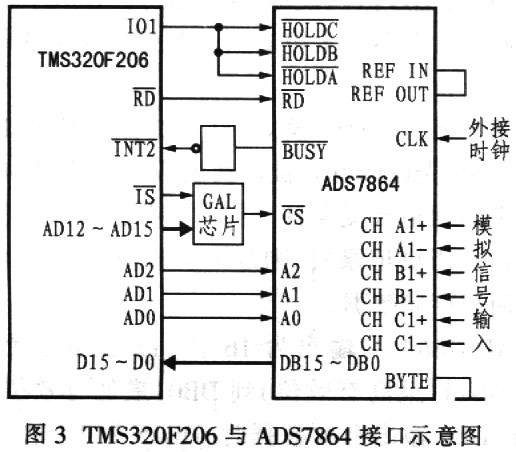

圖3

從該系統(tǒng)結(jié)構(gòu)可見,其FFT運(yùn)算處理單元承擔(dān)FFT運(yùn)算的巨大運(yùn)算任務(wù),從而大大減輕了控制單元的工作量,其處理器單元Nios只需完成TCP/IP的協(xié)議實現(xiàn)和簡單的控制功能。該系統(tǒng)提供了Ethernet和標(biāo)準(zhǔn)RS485接口,可以直接接入局域網(wǎng)或通過標(biāo)準(zhǔn)IEC4000-5-104規(guī)約直接接入電力調(diào)度網(wǎng),具有良好的網(wǎng)絡(luò)通信功能,便于用戶將該分析儀無縫接入電力調(diào)度網(wǎng)或生產(chǎn)控制網(wǎng)。用戶可以通過局域網(wǎng)對該分析儀進(jìn)行控制或進(jìn)行諧波數(shù)據(jù)傳輸,也可直接在該儀器上進(jìn)行控制數(shù)據(jù)查閱。

2 系統(tǒng)具體實現(xiàn)

CT/PT傳感器單元是該系統(tǒng)的關(guān)系環(huán)節(jié)之一,其性能直接決定整個系統(tǒng)能達(dá)到的精度等級。對其性能的主要要求有非線性度、相移、線性范圍、小信號響應(yīng)和高頻衰減。非線性度、相移、線性范圍是最基本的性能指標(biāo),按照該系統(tǒng)的精度要求,非線性度必須小于0.1%;相移必須小于5';線性范圍必須大于系統(tǒng)的輸入范圍并20%的裕量。小信號響應(yīng)主要針對于CT,因輸入電流從0~15A變化,當(dāng)輸入電流非常小時仍然需要精確變換,因此對CT的小信號性能要求較高。高頻衰減指標(biāo)主要對高次諧波,通常傳感器對于高頻率信號有較強(qiáng)的衰減作用,表現(xiàn)為低通濾波器。而本系統(tǒng)最高需對2.5kHz信號進(jìn)行采樣分析,因此高頻衰減也是非常重要的指標(biāo)不。本系統(tǒng)按照以上指標(biāo)選用高性能CT/PT傳感器,滿足系統(tǒng)的精度要求。

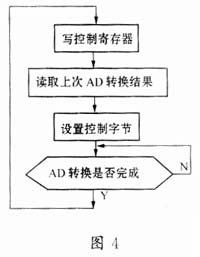

A/D采樣單元采用了Maxim公司的MAX125高速8通道14位同步A/D采樣芯片,該芯片具有8個采樣通道,可以時對4個通道進(jìn)行掃描采樣,每個采樣周期只需對該芯片進(jìn)行兩次讀操作便能完成8個通道的采樣。A/D轉(zhuǎn)換使用逐次逼進(jìn)去,采樣總速率為250kHz,4通道同步掃描采樣時單個通道的采樣速率大于30kHz,遠(yuǎn)遠(yuǎn)超過本系統(tǒng)對16個通道同步采樣的速率要求。該芯片通過內(nèi)部集成的多路開關(guān)來實現(xiàn)4通道同步掃描采樣,芯片內(nèi)部有一個4×16位的RAM用于存放每次掃描采樣的4通道數(shù)據(jù)。該芯片提供了14位的數(shù)據(jù)線,可以在一次掃描采樣結(jié)束后在4個時鐘周期內(nèi)將4個采樣結(jié)果全部輸出。當(dāng)采樣位數(shù)為14位,其LSB代表(1/2 13)VIN(VIN為最大電壓輸入值)即VIN/8192,而該芯片的采樣誤差僅為2個LSB即2VIN/8192,約為0.025%VIN,所以該采樣芯片能較好滿足本系統(tǒng)的精度要求。系統(tǒng)對單個通道的采樣速率要求為12.8kHz(每工頻周波采樣256點),而該芯片的單通道采樣速率大于30kHz,所以該芯片能較好滿足本系統(tǒng)的采樣速率要求。

從FFT的分析可知,其誤差很大程度來自采樣窗口和實際波形的同步不嚴(yán)格,造成頻譜泄漏。為消除頻譜泄漏引起的誤差,常用的方法有:硬件同步、加窗處理。硬件同步的方法比較多,常用的主要有使用PLL電路進(jìn)行同步。按照GB/T14549-1993要求,只允許使用矩形窗和漢寧窗,使用矩形窗時窗口間不能有間隔和重疊。為減少信號的混疊和頻譜泄漏,本系統(tǒng)的A/D采樣單元通過使用高精度的PLL實現(xiàn)嚴(yán)格的同步采樣,以保證窗口間無重疊和間隔,并能嚴(yán)格與被測信號頻同步,并在FFT運(yùn)算單元實現(xiàn)了加漢寧窗處理。采樣單元基本原理如圖2所示。

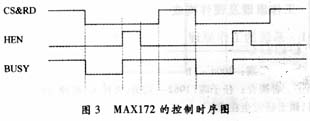

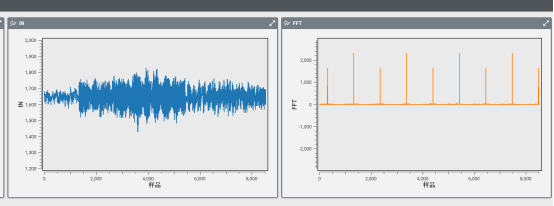

FFT運(yùn)算處理單元基于一塊Altera公司的EP1C20FPGA芯片,該芯片帶有294912位RAM,具有20060個LE,最大I/O引腳301。FFT運(yùn)算處理單元采用先進(jìn)的多層并行流水線技術(shù),工作在30MHz的頻率下,可以在1ms內(nèi)完成8路工頻輸入信號的256點FFT運(yùn)算處理。該處理單元的原理如圖3所示。

該單元實際包含兩大部分,即采樣控制邏輯部分和FFT運(yùn)算部分。采樣邏輯部分負(fù)責(zé)MAX125的讀數(shù)據(jù)邏輯控制。FFT運(yùn)算部分包括FFT控制邏輯、采樣數(shù)據(jù)緩存、FFT處理核與結(jié)果存儲FIFO。從IDT72V845輸出的14位采樣數(shù)據(jù),首先暫存于采樣數(shù)據(jù)緩存中;然后FFT處理核從該緩存中讀取數(shù)據(jù)進(jìn)行處理;處理完畢的數(shù)據(jù)存放于結(jié)果FIFO中;FFT控制邏輯單元向Nios處理器申請中斷,Nios處理器響應(yīng)應(yīng)該中斷向FFT控制邏輯單元發(fā)送讀信號;然后從結(jié)果FIFO讀取分析結(jié)果。

以往FFT設(shè)計中,往往使用定點數(shù)。因為使用定點數(shù)時,系統(tǒng)結(jié)構(gòu)相對簡單、運(yùn)算速度快,但精度不高。在FPGA中使用浮點數(shù)時,系統(tǒng)相對設(shè)計復(fù)雜,但精度高。基于本系統(tǒng)對精度的苛刻要求,故采用浮點數(shù)進(jìn)行FFT的硬件算術(shù)實現(xiàn)。FFT處理核采用先進(jìn)的多層并行流水線技術(shù),可以在1ms內(nèi)完成8路256點的FFT運(yùn)算。該單元實際相當(dāng)于一個基于標(biāo)準(zhǔn)單精度浮點數(shù)的FFT變換協(xié)處理器,提供了簡單可靠的接口以連接采樣單元和處理器,并能獨立進(jìn)行FFT處理。

顯示單元為一塊普通點陣LCD顯示屏,可以顯示各種諧波分析的數(shù)據(jù)和簡單波形。該LCD顯示屏由處理器直接控制。

網(wǎng)絡(luò)接口單元是由1塊MAX485芯片和1塊RealTek8019以太網(wǎng)接口芯片構(gòu)成。MAX485芯片提供了標(biāo)準(zhǔn)的RS485接口,其通信協(xié)議為標(biāo)準(zhǔn)IEC4000-5-104規(guī)約,該規(guī)約為IEC規(guī)定的標(biāo)準(zhǔn)電力系統(tǒng)通信規(guī)約。通過處理器的系統(tǒng)軟件實現(xiàn),可以直接傳送分析結(jié)果數(shù)據(jù)給上層使用同樣規(guī)約的第三方綜合自動化站或監(jiān)控系統(tǒng)。RealTek8019是一塊全雙工以太網(wǎng)接口芯片,該芯片實現(xiàn)了RFC 1600規(guī)范中要求的物理層,提供了標(biāo)準(zhǔn)的以太網(wǎng)接口,其通信協(xié)議為標(biāo)準(zhǔn)的TCP/IP協(xié)議,通過處理器的軟件實現(xiàn)。

控制單元核心為使用FPGA實現(xiàn)的處理器Nios。Nios是Altera公司提供的基于Harvard結(jié)構(gòu)的RISC通用處理器IP Core,目前最新版本為3.0,有16位和32位兩個版本。兩個版本均使用16位的RISC指令集,差別主要于系統(tǒng)總線帶寬。在系統(tǒng)開發(fā)中使用Nios,可以根據(jù)需要自行配置處理器數(shù)目可多達(dá)512個。開發(fā)者可在FPGA容量允許范圍內(nèi),自由配置處理器的Cache大小、指令集ROM大小、片內(nèi)RAM和ROM大小、I/O引腳數(shù)目和類型、中斷引腳數(shù)目、定時器數(shù)目、通用串口數(shù)目、擴(kuò)展地址和數(shù)據(jù)引腳等處理器的性能指標(biāo),而且可以在處理器ALU中直接加入自行定義的數(shù)字邏輯,并添加自行定義的處理器指令。可見,使用Nios具有極大靈活性和很高的處理效率。使用Altera公司推出的SOPC Builder開發(fā)工具,開發(fā)者可以快速開發(fā)出滿足設(shè)計需要的處理器。該開發(fā)工具支持C、C++語言,并提供了常用的功能類庫。開發(fā)者可以直接使用C、C++語言進(jìn)行系統(tǒng)軟件開發(fā),然后在線調(diào)試自行設(shè)計的Nios處理器和軟件。當(dāng)軟件達(dá)到設(shè)計要求時,可通過該工具將執(zhí)行代碼轉(zhuǎn)換成Flash文件格式或HEX文件下載到啟動Flash或FPGA器件中,使所設(shè)計的系統(tǒng)可獨立運(yùn)行。本系統(tǒng)使用的Nios為32位版本,約使用了2093個邏輯單元,具有64KB ROM和4KB RAM,工作在50MHz頻率。設(shè)計帶有3個中斷引腳、1個通用定時器/計數(shù)器和1個通用串行口,與FFT運(yùn)算單元整合在同一FPGA芯片中。所有FPGA設(shè)計均使用Verilog HDL硬件描述語言進(jìn)行設(shè)計。

在高速數(shù)字系統(tǒng)中,使用直接整合在FPGA芯片中的處理器具有優(yōu)越的性能。在高速數(shù)字系統(tǒng)中,由于信號頻率的增加導(dǎo)致PCB連線呈現(xiàn)傳輸線特性,從而影響到信號的完整性。線路間的串?dāng)_、芯片間的連接拓?fù)洹⑿酒囊_分布和封裝形式、PCB的幾何特性及介電特性、過孔及電壓參考平面等均會嚴(yán)重影響高速信號的完整性。將電路中的高速數(shù)字信號部分整合在同一FPGA芯片中,則能有效解決以上的大部分影響因素,且可充分利用FPGA內(nèi)部豐富的連線資源來增加系統(tǒng)的數(shù)字總線資源。FPGA可實現(xiàn)絕大部分數(shù)字電路設(shè)計,而將所需的功能直接整合在FPGA的設(shè)計中,因此可大大減小處理器外圍擴(kuò)展電路數(shù)目,降低外圍電路和布局走線復(fù)雜度,減少影響高速信號完整性的因素,提高系統(tǒng)的抗干擾能力。FPGA具有豐富的部I/O引腳,可以充分滿足電路設(shè)計時的外部擴(kuò)展連接需求。

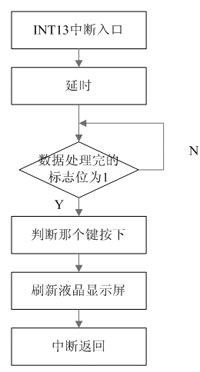

基本接口電路如圖4所示。

圖4

由于處理器承擔(dān)著多重任務(wù),因此在系統(tǒng)軟件中入了實時操作系統(tǒng)RTOS作為操作系統(tǒng)環(huán)境。使用RTOS的優(yōu)勢是非常明顯的,它可屏蔽底層設(shè)備,提供多進(jìn)程的并發(fā)操作,合理調(diào)配優(yōu)先極不同的任務(wù),有效管理內(nèi)存空間,使開發(fā)者可以集中精力關(guān)注于功能的實際算法,并且為軟件的調(diào)試、移植和有效復(fù)用提供良好的條件。本系統(tǒng)使用RTOS為源代碼開放的μC/OSII。ΜC/OSII是由Jean J.Labrosse編寫的源代碼公開的RTOS,目前被移植到多種平臺上廣泛使用,是一個經(jīng)過實踐考驗的優(yōu)秀RTOS。ΜC/OSII可以同時管理64個進(jìn)程,每個進(jìn)程必須有不同優(yōu)先級。其中優(yōu)先級0、1、2、3、OS_LOWEST+PRIO-3,OS_LOWEST_PRIO-2,OS_LOWEST_PRIO-1和OS_LOWEST_PRIO為系統(tǒng)保留,所以最大可使用54個進(jìn)程。ΜC/OSII是一個搶占式的RTOS,即系統(tǒng)能中止低優(yōu)先級進(jìn)程的執(zhí)行,使高優(yōu)先級的進(jìn)程獲得執(zhí)行權(quán),這樣能有效保障進(jìn)程調(diào)度的實時性。由于μC/OSII的內(nèi)存管理功能過弱,因此本系統(tǒng)軟件中只使用了其進(jìn)程調(diào)度、互斥同步機(jī)制及通信機(jī)制部分,自行編寫了內(nèi)存管理部分以適應(yīng)系統(tǒng)網(wǎng)絡(luò)通信時對內(nèi)存管理的需求。在系統(tǒng)中創(chuàng)建了6個進(jìn)程,包括中斷響應(yīng)進(jìn)程、Ethernet管理進(jìn)程、串口管理進(jìn)程、采樣控制進(jìn)程、FFT管理進(jìn)程及顯示進(jìn)程,其優(yōu)先級依次下降。中斷響應(yīng)進(jìn)程負(fù)責(zé)處理中斷的響應(yīng)和中斷的響應(yīng)進(jìn)程調(diào)用;Ethernet管理進(jìn)程負(fù)責(zé)處理TCP/IP通信事件;串行口管理進(jìn)程負(fù)責(zé)處理RS485串口通信事件;采樣控制進(jìn)程負(fù)責(zé)管理采樣控制;FFT管理進(jìn)程負(fù)責(zé)FPGA的FFT處理單元和處理器之間的事務(wù)處理;顯示進(jìn)程負(fù)責(zé)控制LCD的顯示。

具體的軟件工作流程為:中斷響應(yīng)進(jìn)程由于優(yōu)先級最高,所以可以及時對所有中斷進(jìn)行響應(yīng)處理。在具體中斷發(fā)生時,中斷響應(yīng)進(jìn)程首先判斷為何種中斷,然后調(diào)用相應(yīng)的處理進(jìn)程,同時中斷響應(yīng)進(jìn)程放棄CPU主動休眠,從而讓處于低優(yōu)先級的處理進(jìn)程可以獲得CPU時間運(yùn)行。在處理完中斷后,處理進(jìn)程主動休眠,在更低優(yōu)先級的處理進(jìn)程可以處理完被打斷的工作。當(dāng)所有處理進(jìn)程均無處理工作時,主動喚醒中斷響應(yīng)進(jìn)程。處于休眠態(tài)的中斷響應(yīng)進(jìn)程可實時被中斷信號所喚醒,從而保證所有中斷均能得到實時響應(yīng)。該系統(tǒng)軟件使用RTOS后,程序結(jié)構(gòu)清楚,開發(fā)人員可以把精力集中于控制算法上,而不必過多考慮底層的問題,從而有效縮短開發(fā)時間,程序的可靠性大大提高。

3 總結(jié)

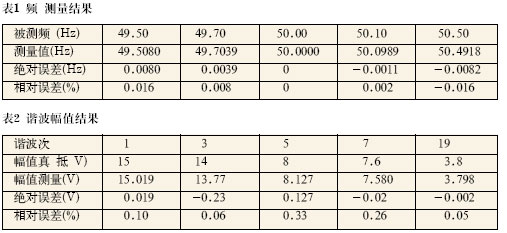

按照本系統(tǒng)所制造的產(chǎn)品已經(jīng)通過實際測試,其基波幅值誤差小于0.2%,諧波幅值誤差小于5%,相位誤差小于0.2%,其精度滿足GB/T 17626.7規(guī)定的A級測量儀器精度要求。該產(chǎn)品成本低廉,結(jié)構(gòu)緊湊,抗干擾性強(qiáng)。實際應(yīng)用中,用戶可按實際需求在變電站二次側(cè)任意設(shè)置諧波監(jiān)測點,并可通過局域網(wǎng)或RS485接口方便地接入變電站管理系統(tǒng)中,從而有效實現(xiàn)對線路諧波的監(jiān)測。

電子發(fā)燒友App

電子發(fā)燒友App

評論