從操作系統能否滿足實時性要求來區分,可把操作系統分成分時操作系統和實時操作系統,分時操作系統按照相等的時間片調度進程輪流運行,分時操作系統由調度程序自動計算進程的

2011-11-14 17:39:30 12251

12251 51單片機使用哈佛結構,它RAM和ROM的總線是同一套總線分時復用的還是兩套總線?

2023-05-09 16:03:12

CPLD在DSP系統中的應用設計

2011-08-03 16:15:49

CPLD在汽車制動性能檢測系統中的應用汽車制動性是汽車主動安全的主要性能之一,是汽車行駛安全的重要保障。因此,汽車的制動性能的檢測研究為其制動性能試驗研究和生產檢測提供了條件,為提高制動性能提供了

2009-04-16 13:56:57

作為一個新的系統時鐘,所有的設計都是基于這個時鐘來設計呢在編譯時候會出現警告,是一個關于buff的警告并且仿真時正確的,但是下載到硬件發現不是很符合設計要求查閱資料說有的CPLD里面會有PLL模塊,可是有的么有。沒有的用時鐘分頻后的信號作為新的時鐘觸發是不科學的,所以在此詢問各位大神。給個經驗說法吧

2013-04-25 09:39:35

分時操作系統(Time-sharing Operating System) 分時操作系統將系統處理機時間與內存空間按一定的時間間隔(劃分時間片),采用輪轉運行方式輪流地切換給各終端用戶的程序

2021-12-14 08:28:38

的試驗變壓器。變頻串聯諧振試驗裝置在電力系統應用中的優點1、所需電源容量大大減小。串聯諧振電源是利用諧振電抗器和被試品電容諧振產生高電壓和大電流的,在整個系統中,電源只需要提供系統中有功消耗的部分,因此

2020-09-05 00:12:40

資料:AG32中cpld的基礎

2024-01-03 10:20:43

]/ UHPI_HD[2]/ GP0[2]若系統中,通過EMIFA外掛了一個8位NAND FLASH,且同時支持SD卡,是不是意味著上述這類型管腳需分時復用,即操作SD卡配置為SD用途,操作NAND FALSH時又切換為EMIFA模塊功能?

2020-05-25 06:42:18

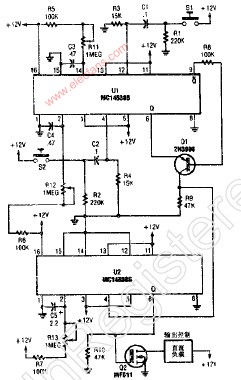

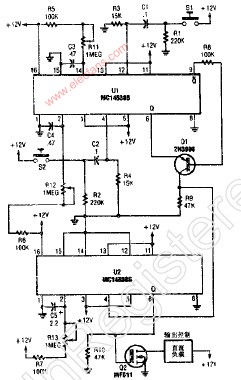

的速度是480Mbits/s,完全可以滿足圖像采集、傳輸以及后續處理的要求。系統中采用 DSP+CPLD的硬件設計方案,采用現場可編程芯片 CPLD及兩片 SRAM構成的圖像采集和存儲系統,可以根據

2019-06-20 07:31:29

是480Mbits/s,完全可以滿足圖像采集、傳輸以及后續處理的要求。系統中采用 DSP+CPLD的硬件設計方案,采用現場可編程芯片 CPLD及兩片 SRAM構成的圖像采集和存儲系統,可以根據

2019-07-26 07:16:41

**本文轉載自《#2023盲盒+碼# OpenHarmony組件復用示例》,作者zhushangyuan_**

● 摘要:在開發應用時,有些場景下的自定義組件具有相同的組件布局結構,僅有狀態變量等

2023-08-29 14:40:32

SPI復用時,調試之后讀寫數據總是不對是為什么?

2022-02-17 07:16:37

STM32外設為什么不需要開啟復用時鐘(AFIO時鐘)呢?STM32外設什么時候需要開啟AFIO時鐘呢?

2021-11-24 08:05:59

lattice的LC4000的CPLD一個腳可否分時輸出3.3、3、0V的電壓呀?PCB打樣找華強 http://www.hqpcb.com 樣板2天出貨

2013-03-28 16:00:26

如果輸入時鐘時差分時鐘信號,如何編寫testbench?

2014-09-15 19:37:38

文章目錄1簡介1uCOS-II中的任務1簡介uCOS-II實時操作系統實時操作系統與分時操作系統的區別:分時操作系統將時間一塊一塊的分給不同的任務。實時操作系統提供給用戶三樣東西:內存管理

2021-12-14 06:42:55

串口通信為何要打開復用時鐘???小白不是很理解,求大佬解釋?

2023-10-23 06:04:02

1、觸摸屏中的外部中斷初始化里面有個句子(如下紅色的語句),明明是PC時鐘使能,而且前面已經使能了, 再次賦值不是沒有用嗎?哪里有使能復用時鐘?2、在觸摸屏實驗中怎么我找不到spi的使能的?直接調用

2019-10-31 22:44:38

什么是CPLD,怎么選擇?CPLD在雙軸位置檢測系統中的應用設計

2021-04-30 06:24:23

特點:①多路性。用戶通過各自的終端,可以同時使用一個系統。②及時性。用戶提出的各種要求,能在較短或可容忍的時間內得到響應和處理。③獨占性。在分時系統中,雖然允許多個用戶同時使用一個 CPU,但用戶之間

2011-11-02 10:47:56

低漏電多路復用器在高阻抗PLC系統中是否重要?

2020-11-27 06:25:59

關于STM32單片機的復用功能我有點疑問:什么時候用復用輸出????什么時候開啟復用時鐘????謝謝!!!!

2017-08-13 10:22:47

特點:①多路性。用戶通過各自的終端,可以同時使用一個系統。②及時性。用戶提出的各種要求,能在較短或可容忍的時間內得到響應和處理。③獨占性。在分時系統中,雖然允許多個用戶同時使用一個 CPU,但用戶之間

2011-11-23 08:48:34

請問,我要是只有一個iic,但有兩個設備需要用到iic,那iic可以分時復用,會不會有沖突??????

2023-10-26 07:39:35

一.需求采用8腳MCU,需要檢測5路輸入信號,輸出4路控制信號二.設計構思5路輸入信號中,1路需要獨占I/O口,分配給P3.5。其余4路與輸出信號,可以分時使用I/O口,故4路輸入與4路輸出同時

2015-12-24 21:25:43

基于CPLD的系統中I2C總線的設計

2012-08-17 11:17:28

現在大多數的CPLD(復雜可編程邏輯器件)都采用可減少功耗的工作模式,但當系統未使用時,應完全切斷電源以保存電池能量,從而實現很多設計者的終極節能目標。圖1描述了如何在一片CPLD 上增加幾只

2018-09-26 17:29:24

現在大多數的CPLD(復雜可編程邏輯器件)都采用可減少功耗的工作模式,但當系統未使用時,應完全切斷電源以保存電池能量,從而實現很多設計者的終極節能目標。

2019-10-08 10:45:26

本文設計的基于CPLD的雙CAN控制器已運用于實際應用中,電池管理系統運行可靠,CAN報文收發平穩,完全適合混合動力汽車的使用。

2021-05-06 06:51:07

嗨, 我正在通過App。關于如何連接CRII CPLD中的LED的說明805。該說明提到CPLD可以在LED的情況下吸收電流,即。如果連接的引腳處于邏輯0,那么LED將發光,反之亦然。如果連接的引腳

2019-08-08 06:20:48

本系統以AD7892SQ和CPLD(復雜可編程邏輯器件)為核心設計了一個多路信號采集電路,包括模擬多路復用、集成放大、A/D轉換,CPLD控制等。采用硬件描述語言Verilog HDL編程,通過采用CPLD使數據采集的實時性得到提高。

2021-05-08 07:51:14

基于CPLD的三相五電平變頻器PWM脈沖發生器的原理是什么基于CPLD的級聯型多電平變頻器脈沖發生器的設計

2021-05-08 06:18:39

從事便攜式或手持產品設計的工程師都明白對于如今的設計,最大限度地降低功耗是必不可少的要求。但是,只有經驗豐富的工程師理解盡可能地延長系統的電池壽命的那些微妙但又重要的細節。本文中我們的重點是,如何使用超低功耗的復雜可編程邏輯器件(CPLD)?如何在嵌入式設計中降低CPLD的功耗?

2019-08-01 08:19:42

不出來————小白??如果你存在按鍵Key和顯示Led共用同一個IO時,需要分時復用的需求,則可以移植代碼進行使用:代碼所占code少于0.5K線程安全,中斷安全可移植性高,配置容易注意:系統需要存在一個至少為1ms的時鐘中斷01 - PCB原理圖例程??舉2個Key和Led共用IO口的

2021-12-16 07:41:59

FDM系統中,波分復用器用于發射端將多個波長的信號復合在一起并注入傳輸光纖中,而波分解復用器則用于在接收端將多路復用的光信號按波長分開分別送到不同的接收器上,波分復用/解復用器可以分成兩大類,即有源(主動

2016-08-11 15:42:21

電機變頻調速系統主要優點電機變頻調速系統主要缺點

2021-01-21 06:38:54

原子哥,***和sd卡和w25q16同時在戰艦板子上如何使用分時復用而不影響各自的功能,求詳細解說,實在不行我只能模擬spi來驅動***了。

2020-07-24 03:08:31

AFIO復用時鐘什么時候打開?手冊上說,在對寄存器AFIO_EVCR,AFIO_MAPR和AFIO_EXTICRX進行讀寫操作前,應當首先打開AFIO的時鐘。但是我看STM32官方提供的《TM32

2020-07-29 05:21:21

請問DMA總線訪問APB外設和SRAM1,CPU操作CCM RAM,這個是同時進行的,還是分時復用的呢?

2024-03-08 07:45:09

什么是復用?請問一下STM32的復用時鐘何時開啟?

2021-11-24 07:19:24

另外,在DSP系統中為什么要使用CPLD?有大俠指導嗎?

2019-07-05 03:42:00

請問,我要是只有一個iic,但有兩個設備需要用到iic,那iic可以分時復用,會不會有沖突??????

2019-03-15 06:35:07

如何實現CPLD的在系統編程?

2021-04-25 07:05:12

高速數據采集系統的硬件結構MAX7000系列CPLD及其開發平臺介紹CPLD在高速數據采集系統中的應用

2021-04-08 06:11:56

基于CPLD的系統中I2C總線的設計 摘要: 在介紹I2C總線協議的基礎上,討論了基于CPLD的系統中I2C總線的設計技術,并結合工程實例設計了I2C總線IP核,

2008-08-13 13:43:38 31

31 介紹了一種基于DSP 和CPLD 的十二相交- 交變頻器的全數字化設計。實驗表明,由定點DSP 和CPLD 構成的全數字交交變頻器,設計、調試方便,控制性能優良,穩定性好,可靠性高。

2009-04-06 14:56:20 26

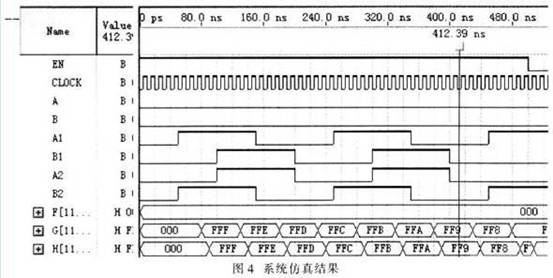

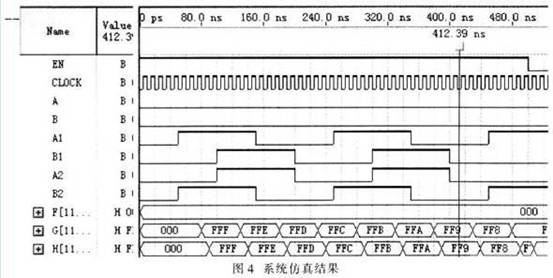

26 簡要介紹利用MaxplusII 軟件來實現VVVF 控制SPWM 變頻調速的方法。設計中提出一種三相分時運算思路, 詳細闡明其具體實現方式。試驗證明,CPLD 應用于變頻調速系統控制是非常有效的

2009-05-14 13:32:58 23

23 在單片機系統中使用CPLD,可使系統構成靈活,提高可靠性,縮短開發周期。介紹在MCS-51 應用系統中的CPLD 應用設計實例, 詳細分析CPLD 的應用和實現方法,提出設計中選用和使用CPLD

2009-05-14 13:49:49 39

39 本文介紹了一種基于CPLD的溫度采集系統的設計方法,設計分為溫度采集和LED顯示兩個功能模塊。與常用溫度采集系統相比,本設計采用高精度數字溫度傳感器MAX6627與CPLD控制芯片E

2009-07-07 13:44:56 22

22 基于CPLD 和DSP 設計了線陣CCD 檢測系統,CCD 的時序驅動由CPLD 實現,經過運放后的視頻信號由TMS320F2812 進行采集和處理,此檢測系統已成功應用于醫藥包裝行業的數粒機系統,能夠可

2009-08-13 14:53:46 22

22 介紹了基于CPLD 和EDA 技術的BIT(機內測試)系統的實現。本系統以CPLD 為控制核心,在MAX+PLUSII 環境下采用VHDL 語言實現了系統接口及測頻電路。該系統具有集成度高、靈活性強、易于開

2009-09-03 09:30:51 9

9 復雜可編程邏輯器件(CPLD)結合了專用集成電路和DSP 的優勢,既具有很高的處理速度,又具有一定的靈活性。因此,基于CPLD 的數字調制系統的研究具有重要的實際意義。本文論

2009-11-30 16:30:17 20

20 CPLD 器件應用隨著生產工藝的逐步提高以及 CPLD 開發系統的不斷完善,CPLD 器件容量也由幾百門飛速發展到百萬門以上,使得一個復雜數字系統完全可以在一個芯片中實現。HDL

2010-01-27 11:40:02 48

48 在單片機系統中使用CPLD,可使系統構成靈活,提高可靠性,縮短開發周期。介紹在MCS-51應用系統中的CPLD應用設計實例,詳細分析CPLD的應用和實現方法,提出設計中選用和使用CPLD的

2010-07-14 14:04:25 39

39 介紹了基于CPLD的刷卡式電腦聯網集控型自動存包系統的設計,并對系統的軟硬件構成、CPLD內部邏輯設計、工作原理等進行了詳細說明。該系統速度快、安全性好、可靠性高,而且具

2010-07-16 15:11:12 20

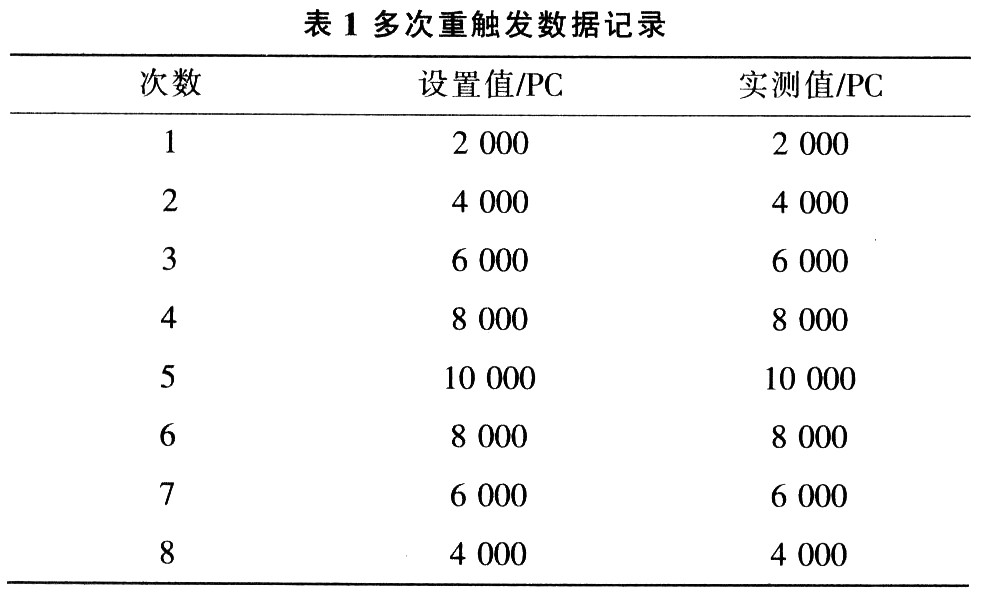

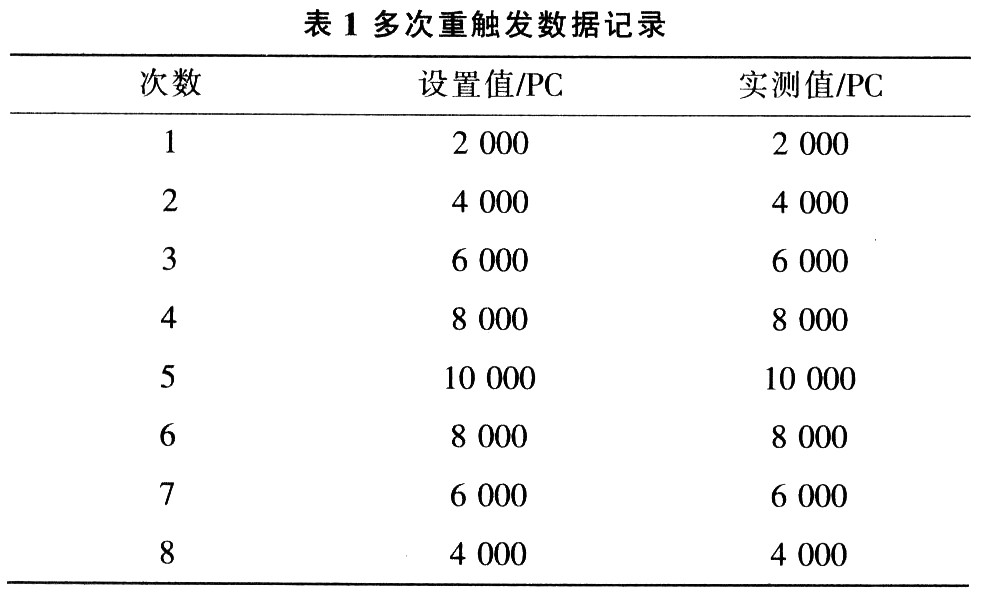

20 提出一種基于CPLD的多次重觸發存儲測試系統設計方案,詳細介紹系統硬件設計以及CPLD內部控制原理,并對CPLD控制電路仿真。該系統體積小、功耗低,能夠實時記錄多次重觸發信號

2010-12-30 16:05:11 22

22 基于CPLD的非多路復用與多路復用總線轉換橋的設計與實現

微處理器對外并行總線接口方式一般分為兩種,一種為多路復用方式,數據與地址采用共用引腳,分時傳輸;另一

2009-03-28 15:08:27 753

753

什么是CPLD

CPLD(Complex Programmable Logic Device)是Complex PLD的簡稱,一種較PLD為復雜的邏輯元件。CPLD是一種用戶根據各自

2009-03-30 13:40:43 3143

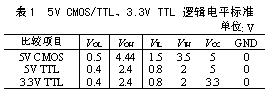

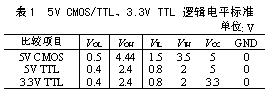

3143 摘要: 較詳細地闡述不同邏輯電平的接口原理。以低壓CPLD EPM7512A為例,給出在混合電壓系統中的具體設計方案。

關鍵詞: 低壓CPLD 邏輯電平

2009-06-20 10:53:23 801

801

分時安全電路

當開

2009-10-05 15:02:18 429

429

基于CPLD和嵌入式系統的高速數據采集系統的設計與實現

介紹一種基于CPLD和嵌入式系統的高速數據采集系統,并詳細闡述了系統的結構和軟硬件的實

2009-10-15 23:46:59 616

616

CPLD在雙軸位置檢測系統中的應用

1 引言數控機床的加T精度主要南位置檢測系統的精度決定,

2009-10-30 08:32:33 431

431

采用CPLD的多次重觸發存儲測試系統解決方案

概述:提出一種基于CPLD的多次重觸發存儲測試系統設計方案,詳細介紹系統硬件設計以及CPLD內部控制

2010-03-17 11:37:51 531

531

波分復用系統(WDM),波分復用系統(WDM)結構原理和分類

波分復用系統簡要介紹

光波分復用技術是在一根光纖中傳輸多波長光信號的一項

2010-03-19 17:17:09 5357

5357 CPLD,CPLD是什么意思

CPLD是指結構比較復雜的可編程邏輯器件,它包括下述輸出宏單元結構:

(1)可編程I/O 允

2010-03-26 17:08:50 3081

3081 今天,大多數的CPLD(復雜可編程邏輯器件)都采用可減少功耗的工作模式,但當系統未使用時,應完全切斷電源以保存電池能量,從而實現很多設計者的終極節能目標。圖1描述了如

2010-07-16 09:47:26 685

685

本系統以AD7892SQ和CPLD(復雜可編程邏輯器件)為核心設計了一個多路信號采集電路,包括模擬多路復用、集成放大、A/D轉換,CPLD控制等。采用硬件描述語言Verilog HDL編程,通過采用CPLD使數

2011-08-23 10:08:38 1447

1447

介紹了采用光纖陀螺器件共享、基于時分復用的三軸一體化光纖陀螺的結構及其工作原理。針對時分復用方案的特點,在滿足相關器件工作要求的條件下,重點討論了三軸陀螺時分復用工

2011-09-13 14:37:44 35

35 CPLD在高速數據采集系統中的應用! 介紹了高速數據采集系統的整體框架分析了其中的通用部分CPLD系列產品的特點及其開發軟件.CPLD根據高速數據采集系統的需要VHDL語言的形式,介紹了由

2011-12-17 00:12:00 26

26 利用W INDOW S 消息驅動機制實現對任務的調度, 并給出一種基于分時操作系統原理的單片機多任務控制, 系統應用實例.

2012-04-10 14:30:29 81

81 導波雷達物位計是一種利用時域反射原理實現的高性能物位計。為了實現導波雷達物位計這一高精度時差測量系統,采用了CPLD和MSP430單片機協同工作的電路設計。CPLD為信號收發模塊的

2012-11-26 14:49:42 53

53 基于CPLD的多路音頻采集系統,有需要的下來看看。

2016-01-21 11:07:07 28

28 基于ARM和CPLD的無線內窺系統設計

2017-01-24 16:15:38 19

19 基于CPLD高速數據采集系統設計_鮮果

2017-03-19 11:45:23 3

3 硬件在回路實時仿真是研究復雜機電系統過程中的一個重要環節,由于仿真通道數量有限,不能滿足復雜機電系統大量信號的同步仿真需求。提出一種信號復用/解復用算法,其基本思想是信號復用算法在仿真器的FPGA

2018-02-04 10:12:22 0

0 本文介紹了變頻器、高性能變頻調速系統、典型調速系統及控制環節以及其應用時的注意事項。它是筆者在該領域多年工作的體會和總結,其特點是以工程師和教授的雙重眼光來看待和認識這項技術,既有原理介紹

2018-06-01 11:25:34 7

7 介紹了一種用CPLD(復雜可編程邏輯器件)作為核心控制電路的測試系統接口,通過時cPLD和竹L電路的比較及cPLD在系統中實現的強大功能,論述了CPLD在測試系統接口中應用的可行性和優越性,簡單介紹

2019-01-01 16:18:00 1472

1472

現在大多數的CPLD(復雜可編程邏輯器件)都采用可減少功耗的工作模式,但當系統未使用時,應完全切斷電源以保存電池能量,從而實現很多設計者的終極節能目標。圖1描述了如何在一片CPLD 上增加幾只分立

2019-04-18 16:00:42 516

516

變頻器與自控系統配合使用時,由于變頻器與調節閥的使用是不同的,所以有些問題需要重視和注意。

2019-04-29 16:00:59 1070

1070 晶閘管無換向電動機變頻系統分AC-DC-AC(交-直-交)變頻及AC-AC(交一交)變頻。(1) AC-DC-AC變頻系統。該類系統采用電流型變頻器,它是由晶閘管構成電源側變換器(整流器)及直流電

2021-11-08 18:21:01 15

15 什么是引腳的分時復用?? 引腳的分時復用是一種技術,它允許在一組引腳上充分利用多種不同的功能,從而降低硬件成本和引腳數量。這種技術在許多電子產品中廣泛使用,包括智能手機、計算機、電視機和汽車電子系統

2023-09-15 17:49:56 1208

1208

電子發燒友App

電子發燒友App

評論