??? 關(guān)鍵詞:PWM? CPLD? IGBT? VHDL? 自頂向下

??? 隨著國(guó)民經(jīng)濟(jì)的不斷發(fā)展,變頻調(diào)速裝置的應(yīng)用越來越廣泛。如何打破國(guó)外產(chǎn)品的壟斷,已成為一個(gè)嚴(yán)肅的課題擺在我國(guó)工程技術(shù)人員的面前。

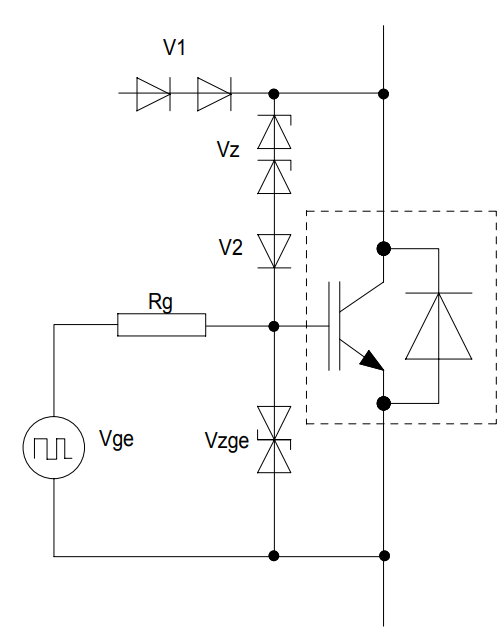

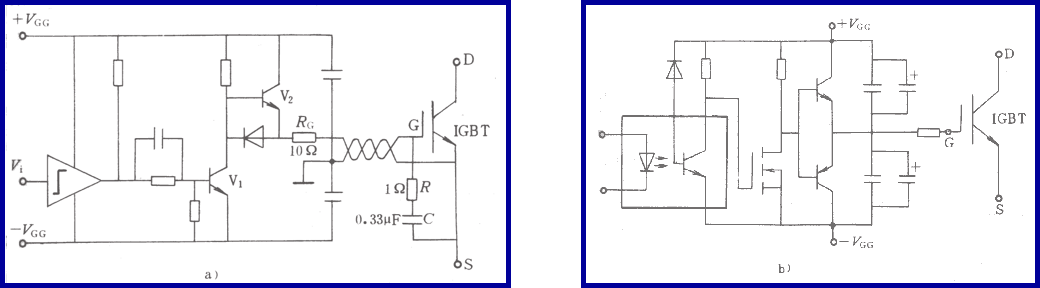

??? 在某型號(hào)大功率變頻調(diào)速裝置中,由于裝置的尺寸較大,考慮到結(jié)構(gòu)和散熱的條件,主控板上DSP產(chǎn)生的PWM信號(hào)需經(jīng)過較長(zhǎng)的距離才能送到IGBT逆變單元中。為保證PWM信號(hào)傳輸?shù)臏?zhǔn)確性和可靠性,必須解決以下幾個(gè)問題:首先是抗干擾問題?變頻器工作時(shí),IGBT的開關(guān)動(dòng)作會(huì)產(chǎn)生高頻干擾信號(hào)??其次是如何保證PWM信號(hào)的前、后沿質(zhì)量,減少IGBT開關(guān)動(dòng)作的過渡過程?最后是如何減少布線電感,盡可能縮短PWM信號(hào)傳輸距離,避免過多的內(nèi)部連線。

1 總體設(shè)計(jì)

??? 原則上說,從觸發(fā)電路到IGBT柵極和發(fā)射極的引線應(yīng)做到既短又一致。但隨著變頻調(diào)速裝置功率的不斷增大,裝置的尺寸也在增大,散熱條件要求更高。由于結(jié)構(gòu)設(shè)計(jì)上的種種原因,真正做到這點(diǎn)有很多實(shí)際困難。

??? DSP產(chǎn)生的PWM信號(hào)既可以采用串行方式又能以并行方式進(jìn)行傳輸,但這兩種方式都有著各自的特點(diǎn)。采用并行方式傳輸信號(hào)(即每一個(gè)IGBT模塊的柵控端都接一根信號(hào)線)會(huì)造成系統(tǒng)內(nèi)部接線過多、接地困難,抗干擾性大大降低,這種情況尤以采用了多重化、多電平技術(shù)的變頻裝置為甚。若利用串行方式,PWM信號(hào)的傳輸速率又受到介質(zhì)的極大限制。在目前諸多傳輸介質(zhì)中,只有光纖具有損耗低、頻帶寬、重量輕、不受電磁干擾等突出優(yōu)點(diǎn)。GI型光纖用LED做光源時(shí),傳輸速率可達(dá)140Mbit/s,傳輸損耗可忽略不計(jì)。IGBT的工作頻率通常很少用在15kHz以上,因此以異步串行方式高速傳輸PWM信號(hào)時(shí),采用光纖作為傳輸介質(zhì)是唯一的選擇。

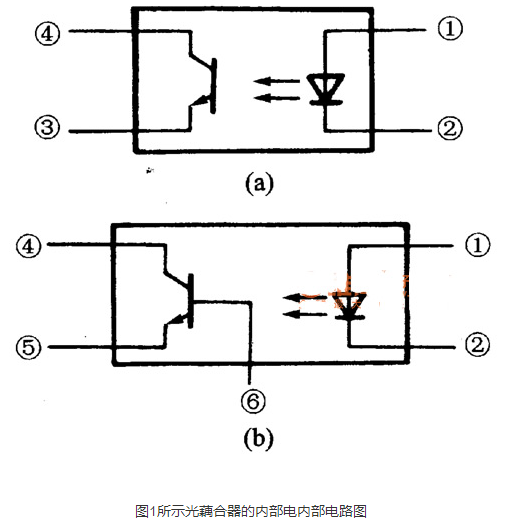

??? 在串行的PWM信號(hào)送到IGBT的柵控端之前,還需將該信號(hào)轉(zhuǎn)化為并行形式。盡管采用普通的串/并轉(zhuǎn)換芯片可以實(shí)現(xiàn)上述功能,但這些芯片的最高工作頻率有限,如74166的最高工作頻率為35MHz,對(duì)于目前廣泛采用多重化和多電平技術(shù)的變頻裝置來講,這種工作頻率顯然有著較大的局限性。尤其是在實(shí)時(shí)性、快速性要求甚高的電機(jī)控制領(lǐng)域,不可能采用應(yīng)答方式完成信號(hào)的傳輸,因此接收端需要有較強(qiáng)的糾錯(cuò)和容錯(cuò)能力。若采用普通的芯片,難以只用一兩片芯片完成上述功能。但CPLD具有極強(qiáng)的靈活性,內(nèi)含128?jìng)€(gè)宏單元,最高工作頻率可達(dá)167MHz(以Cypress CY37128為例),可以只用一兩片芯片就能完成較復(fù)雜的邏輯功能,因此CPLD與光纖的結(jié)合是解決大功率變頻器中信號(hào)傳輸?shù)淖詈眠x擇。系統(tǒng)信號(hào)流程圖如圖1所示。

2 通訊方案

??? 異步串行格式的一個(gè)數(shù)據(jù)幀包括1位起始位和8位數(shù)據(jù)位,最后是停止位。起始位規(guī)定為0,8位數(shù)據(jù)位由高到低順次發(fā)送,前7位組成1個(gè)編碼字符,第八位為奇偶校驗(yàn)位。停止位可以選擇1位、1位、2位。從系統(tǒng)實(shí)際要求出發(fā),我們對(duì)標(biāo)準(zhǔn)的異步串行格式進(jìn)行了修改,將三相PWM信號(hào)進(jìn)行編碼,用以下數(shù)據(jù)格式發(fā)送到信號(hào)轉(zhuǎn)換單元:0-a3c3a2c2a1c1-V-1111。其中0為起始位,a1、a2、a3分別對(duì)應(yīng)三相逆變橋每個(gè)橋臂的柵控信號(hào),c1、c2、c3分別對(duì)應(yīng)三相逆變橋每個(gè)橋臂的封鎖信號(hào),V是一位校驗(yàn)位,最后四個(gè)1為結(jié)束標(biāo)志位。信號(hào)轉(zhuǎn)換單元的CPLD接收到該信號(hào)后,將此串行PWM信號(hào)轉(zhuǎn)換為并行形式。另一方面,為保證逆變單元能夠正常工作,還需將逆變單元故障信號(hào)送到上位機(jī)以供故障診斷。

故障信號(hào)以以下串行編碼格式送出:0-a1a2a3a4a5a6-V-1111,0為起始位,a1、a2、a3分別對(duì)應(yīng)每個(gè)橋臂的驅(qū)動(dòng)故障信號(hào),a4為過熱信號(hào),a5、a6為通訊故障 信號(hào),V為校驗(yàn)位,最后四個(gè)1為結(jié)束標(biāo)志位。上位機(jī)板上的CPLD將此信號(hào)轉(zhuǎn)換為并行形式。事實(shí)上,PWM信號(hào)和故障信號(hào)的處理過程是相同的。

??? 對(duì)于異步串行通訊,通常要保證發(fā)送的信號(hào)在接收端能被正確接收,往往采用兩類同步處理辦法:一類是使用硬件手段實(shí)現(xiàn)通信協(xié)議的部分功能;另一類是使用各種短小的幀來實(shí)現(xiàn)通信功能。在本系統(tǒng),由于實(shí)時(shí)控制對(duì)時(shí)間的要求,不可能采用上述形式的通訊方案。因此根據(jù)系統(tǒng)實(shí)際需要,數(shù)據(jù)傳輸采用起止式同步方案,即用“0”代表起信號(hào),“1”代表止信號(hào)。在不發(fā)送信息時(shí),一直發(fā)送止信號(hào)。第一個(gè)由“1”到“0”的轉(zhuǎn)換表示字符的開始收端檢測(cè)到這個(gè)轉(zhuǎn)換后控制位時(shí)鐘輸出,以便對(duì)接受信號(hào)進(jìn)行碼位中點(diǎn)取樣判決。

??? 針對(duì)系統(tǒng)的實(shí)際要求,為確保數(shù)據(jù)通訊的正確性,在正常工作以前,DSP模塊必須向信號(hào)轉(zhuǎn)換單元固定發(fā)送一個(gè)標(biāo)志字。只有當(dāng)信號(hào)轉(zhuǎn)換單元連續(xù)幾次正確收到標(biāo)志字后,才能建立正常通訊。在正常通訊時(shí),為避免隨機(jī)干擾的作用,只有在連續(xù)出現(xiàn)多次幀錯(cuò)誤的情況下,信號(hào)轉(zhuǎn)換單元才向上位機(jī)發(fā)出通訊故障信號(hào),以確保系統(tǒng)工作的穩(wěn)定性。

3 CPLD的實(shí)現(xiàn)

??? 20世紀(jì)90年代,引起數(shù)字系統(tǒng)設(shè)計(jì)方式發(fā)生突破性變革的技術(shù)是VHDL設(shè)計(jì)技術(shù)。VHDL ?Very High Speed Integrated Circuit ?VHSIC? Hardware Description Language?作為IEEE-1076標(biāo)準(zhǔn)所規(guī)范的硬件描述語(yǔ)言,非常適用于可編程邏輯器件的應(yīng)用設(shè)計(jì),并正在得以普及。采用自頂向下的設(shè)計(jì)方法,是用VHDL設(shè)計(jì)系統(tǒng)硬件最突出優(yōu)點(diǎn)之一。

??? 通過前面對(duì)數(shù)據(jù)流和通訊方案的分析,按照自頂向下的原則,我們對(duì)信號(hào)處理單元進(jìn)行功能分解,將其分解到下面的各個(gè)單元中,見圖2。 通過功能分解,我們可以看到,單元內(nèi)部構(gòu)造可以分為三個(gè)部分:一部分對(duì)柵控信號(hào)進(jìn)行處理;另一部分對(duì)故障信號(hào)進(jìn)行處理;最后一部分用于產(chǎn)生控制故障信號(hào)發(fā)送的時(shí)鐘。

通過功能分解,我們可以看到,單元內(nèi)部構(gòu)造可以分為三個(gè)部分:一部分對(duì)柵控信號(hào)進(jìn)行處理;另一部分對(duì)故障信號(hào)進(jìn)行處理;最后一部分用于產(chǎn)生控制故障信號(hào)發(fā)送的時(shí)鐘。

??? 從圖2我們可以發(fā)現(xiàn)柵控信號(hào)處理部分與故障信號(hào)處理部分都含有功能相同單元:校驗(yàn)位生成單元、數(shù)據(jù)通信控制單元及鎖存單元,因此可以對(duì)以上這些單元進(jìn)行參數(shù)化設(shè)計(jì)。在參數(shù)化設(shè)計(jì)以前,我們還需要構(gòu)造一些公共的基本元件,如觸發(fā)器、寄存器、計(jì)數(shù)器和同步器等。這以后,我們就可以對(duì)前面提到的功能相同的單元進(jìn)行參數(shù)化設(shè)計(jì)。

??? 在進(jìn)行參數(shù)化設(shè)計(jì)以前,我們需要對(duì)各功能單元的輸入輸出信號(hào)進(jìn)行分析以確定信號(hào)使用的數(shù)據(jù)類型。由于IGBT控制問題的特殊性,在這里我們統(tǒng)一使用Bit和Bit-vector型數(shù)據(jù)。Bit型數(shù)據(jù)只有兩種狀態(tài):“0”和“1”,可以有效地防止多態(tài)數(shù)值系統(tǒng)給控制和編程帶來的麻煩。

??? 在進(jìn)行傳統(tǒng)的電子線路設(shè)計(jì)時(shí),設(shè)計(jì)師的工作是按電路原理圖將各個(gè)單元電路和器件連接起來,形成一個(gè)完整的系統(tǒng)。而在利用VHDL設(shè)計(jì)電路時(shí),設(shè)計(jì)師所要完成的不過就是將那些用VHDL語(yǔ)言描述的單元電路和器件連接起來。在這個(gè)意義上,利用VHDL語(yǔ)言進(jìn)行設(shè)計(jì)與利用傳統(tǒng)方法設(shè)計(jì)沒有太大的區(qū)別,但采用自頂向下的設(shè)計(jì)方法時(shí),VHDL具有無(wú)可比擬的優(yōu)越性。作為一種硬件描述語(yǔ)言? VHDL語(yǔ)言有別于一般的計(jì)算機(jī)語(yǔ)言。它既有并行執(zhí)行的語(yǔ)句,又有只能順序執(zhí)行的語(yǔ)句。利用VHDL這種特性,我們可以將整個(gè)系統(tǒng)分成若干個(gè)相對(duì)比較獨(dú)立的模塊來進(jìn)行電路設(shè)計(jì)。在下面的程序中,進(jìn)程COUNTER描述了一個(gè)16位計(jì)數(shù)器,它通過對(duì)40MHz時(shí)鐘進(jìn)行分頻,產(chǎn)生進(jìn)程CONTROLLER所需的2.5MHz時(shí)鐘。進(jìn)程CONTROLLER構(gòu)造了一個(gè)發(fā)送控制計(jì)數(shù)器,它通過對(duì)進(jìn)程COUNTER所產(chǎn)生的時(shí)鐘信號(hào)進(jìn)行計(jì)數(shù),產(chǎn)生故障信號(hào)的發(fā)送控制信號(hào)。

??? CONTROLLER: PROCESS (reset, Tclk)

??? VARIABLE scit_v:BIT_VECTOR(5DOWNTO 0):=″000000″;

??? BEGIN

??? IF (reset='0') THEN

??? scit_v:=″000000″?

??? ELSIF (Tclk'EVENT AND Tclk='1'?

??? THEN

??? IF(scit_v<=″000111″)THEN

??? IF(tdEMPTY_s='0')THEN

??? scit_v:=″001000″;

??? ELSE

??? scit_v:=″000000″;

??? END IF;

??? ELSE

??? scit_v:=scit_v+1;

??? END IF;

??? END IF;

??? scit<=scit_v;

??? END PROCESS;

??? COUNTER: PROCESS(clk,reset)

??? BEGIN

??? IF(reset='0')THEN

??? count_4<=″0000″;

??? ELSIF(clk'EVENTANDclk='1')

??? THEN

??? count_4<=count_4+1;

??? END IF;

??? END PROCESS;

??? 通過上面的程序,對(duì)照?qǐng)D2,我們可以看到整個(gè)設(shè)計(jì)分為三層:基本元件層-功能單元層-頂層;用基本元件構(gòu)成功能單元,再由功能單元組成整個(gè)系統(tǒng)。每完成一個(gè)模塊的設(shè)計(jì),便對(duì)其進(jìn)行仿真測(cè)試,逐步加入各個(gè)構(gòu)造模塊,模塊間通過一定的信號(hào)傳遞,構(gòu)成整個(gè)系統(tǒng)。采用這種方法,仿真測(cè)試貫徹系統(tǒng)硬件設(shè)計(jì)的全過程,從而可以在系統(tǒng)設(shè)計(jì)早期發(fā)現(xiàn)設(shè)計(jì)中存在的問題。與傳統(tǒng)電路設(shè)計(jì)后期進(jìn)行仿真相比可大大縮短系統(tǒng)的設(shè)計(jì)周期,節(jié)約大量的人力和物力。

4 仿真與實(shí)驗(yàn)結(jié)果

??? 圖3是對(duì)上述芯片進(jìn)行的仿真結(jié)果,Data代表來自IGBT的故障信號(hào),仿真時(shí)Data輸入值為“0101”,即“5”。由于通訊正常,a5a6為“11”,因此上述六位產(chǎn)生校驗(yàn)位為“1”,Txd輸出為“0-1010110-1111”。Rxd輸入為“0-1101111-1111”,Pcs?0,2,4?三位輸出表達(dá)式為:aI AND cI ,pcs?1,3,5?三位輸出表達(dá)式為:?NOT a1 ?AND c1,因此Pcs?0,1,2,3,4,5?輸出為“011001”,即“19”。通過對(duì)仿真結(jié)果的分析,可以看到設(shè)計(jì)滿足功能需要。該芯片已成功地用于某型號(hào)的大功率變頻調(diào)速裝置中。

??? 通過上面的設(shè)計(jì),整個(gè)PWM信號(hào)與故障信號(hào)傳輸通路只需3片CPLD芯片就可實(shí)現(xiàn)。系統(tǒng)電路的體積大為縮小,從而提高了系統(tǒng)的可靠性。CPLD的應(yīng)用縮短了系統(tǒng)的設(shè)計(jì)周期,降低了開發(fā)成本。CPLD與光纖的結(jié)合是解決PWM信號(hào)長(zhǎng)距離傳輸中準(zhǔn)確性和可靠性的有

力保障。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論