摘 要: 闡述了自校驗技術(shù)在容錯系統(tǒng)中的作用,給出了自校驗網(wǎng)絡(luò)實現(xiàn)原理及實現(xiàn)方法,指出用VHDL語言結(jié)合FPGA/CPLD是實現(xiàn)大規(guī)模自校驗網(wǎng)絡(luò)的有效途徑。

??? 關(guān)鍵詞: 容錯 自校驗 完全自校驗 VHDL FPGA/CPLD

??? 容錯是容忍錯誤的簡稱,容錯系統(tǒng)是指在發(fā)生硬件故障或存在軟件錯誤的情況下,仍能繼續(xù)正確完成指定任務(wù)的系統(tǒng)。設(shè)計與分析容錯系統(tǒng)的各種技術(shù)稱為容錯技術(shù)。有關(guān)計算機容錯技術(shù)的各種理論及研究已經(jīng)發(fā)展成為計算機學(xué)科的一個重要分支,稱為容錯計算(Fault-tolerant Computing)。設(shè)計容錯系統(tǒng)的指導(dǎo)思想是:系統(tǒng)發(fā)生故障時能自動檢出并使系統(tǒng)自動恢復(fù)正常運行。

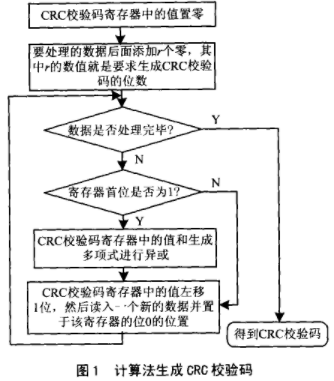

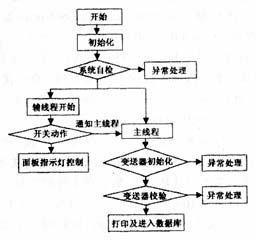

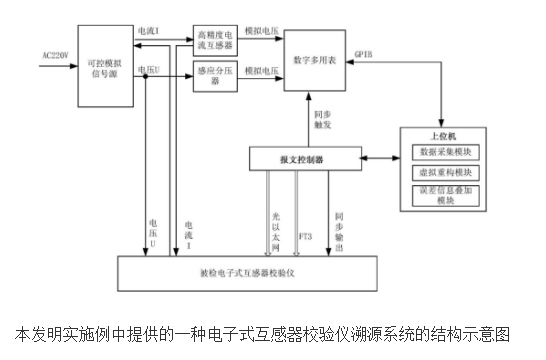

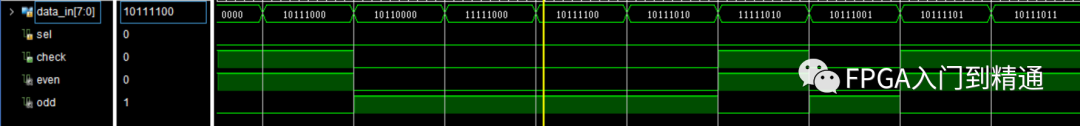

???  為保證系統(tǒng)具有高可靠、長壽命和響應(yīng)迅速,必須采用容錯技術(shù)。從功能上講,一個容錯系統(tǒng)可用圖1所示框圖來描述,系統(tǒng)模塊可由若干個功能相同的子模塊并聯(lián)組成,故障檢測模塊對系統(tǒng)模塊的功能進(jìn)行檢測,檢測到故障后由故障處理模塊對系統(tǒng)模塊進(jìn)行重新配置,使系統(tǒng)在部分模塊失效的情況下,仍能輸出正確結(jié)果。在這個系統(tǒng)中,故障檢測模塊和故障處理模塊起著至關(guān)重要的作用,它們往往是系統(tǒng)的薄弱點。因此,容錯系統(tǒng)要有高的可靠性必須保證故障檢測和處理模塊的可靠性,故障檢測系統(tǒng)不僅要檢測系統(tǒng)模塊的故障,而且還要能夠檢測自身的故障,使故障處理模塊得以正確處理所發(fā)生的故障。

為保證系統(tǒng)具有高可靠、長壽命和響應(yīng)迅速,必須采用容錯技術(shù)。從功能上講,一個容錯系統(tǒng)可用圖1所示框圖來描述,系統(tǒng)模塊可由若干個功能相同的子模塊并聯(lián)組成,故障檢測模塊對系統(tǒng)模塊的功能進(jìn)行檢測,檢測到故障后由故障處理模塊對系統(tǒng)模塊進(jìn)行重新配置,使系統(tǒng)在部分模塊失效的情況下,仍能輸出正確結(jié)果。在這個系統(tǒng)中,故障檢測模塊和故障處理模塊起著至關(guān)重要的作用,它們往往是系統(tǒng)的薄弱點。因此,容錯系統(tǒng)要有高的可靠性必須保證故障檢測和處理模塊的可靠性,故障檢測系統(tǒng)不僅要檢測系統(tǒng)模塊的故障,而且還要能夠檢測自身的故障,使故障處理模塊得以正確處理所發(fā)生的故障。

??? 自校驗技術(shù)是用于故障快速檢測的一種有效手段,特別是具有完全自校驗性質(zhì)的自校驗裝置,它不僅能及時檢出系統(tǒng)模塊的差錯,還能檢測出自身的差錯。在容錯系統(tǒng)設(shè)計中,將自校驗網(wǎng)絡(luò)置于系統(tǒng)中,可大大提高系統(tǒng)對差錯的反應(yīng)能力,使差錯潛伏期縮短,有效地防止錯誤傳播。

??? 1 自校驗網(wǎng)絡(luò)定義

??? 一個容錯系統(tǒng),其所有可能的輸出值組成的集合U(稱輸出空間)由S和U-S兩部分組成。當(dāng)系統(tǒng)中無故障時,系統(tǒng)輸出S中的元素,一旦系統(tǒng)發(fā)生故障則輸出U-S中的元素。

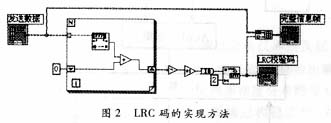

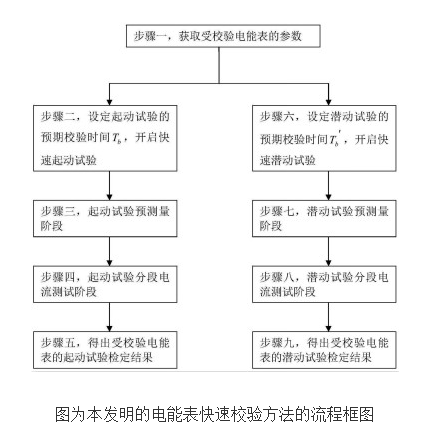

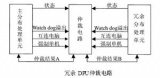

??? 如果一個電路的正常輸出集S是一個檢錯碼集,則該電路稱為自校驗電路。在無故障發(fā)生的情況下,自校驗電路輸出碼向量;當(dāng)預(yù)定故障發(fā)生時,則輸出非碼向量。連接在自校驗電路輸出端的校驗器監(jiān)督電路的輸出,當(dāng)非碼向量出現(xiàn)時,校驗器給出差錯指示。自校驗電路與校驗器一起構(gòu)成了自校驗網(wǎng)絡(luò),其結(jié)構(gòu)如圖2所示。

如果一個電路的正常輸出集S是一個檢錯碼集,則該電路稱為自校驗電路。在無故障發(fā)生的情況下,自校驗電路輸出碼向量;當(dāng)預(yù)定故障發(fā)生時,則輸出非碼向量。連接在自校驗電路輸出端的校驗器監(jiān)督電路的輸出,當(dāng)非碼向量出現(xiàn)時,校驗器給出差錯指示。自校驗電路與校驗器一起構(gòu)成了自校驗網(wǎng)絡(luò),其結(jié)構(gòu)如圖2所示。

??? 下面我們給出自校驗網(wǎng)絡(luò)的幾個概念,設(shè)S(X)是輸入向量空間,![]() 是合法輸入向量空間,

是合法輸入向量空間,![]() 是非法輸入向量空間,S(F)是輸出向量空間,

是非法輸入向量空間,S(F)是輸出向量空間,![]() 是合法輸出向量空間,

是合法輸出向量空間,![]() 是非法輸出向量空間,

是非法輸出向量空間,![]() 是組合邏輯網(wǎng)絡(luò)所考慮的單故障集,網(wǎng)絡(luò)的所有輸入取自其合法輸入集。

是組合邏輯網(wǎng)絡(luò)所考慮的單故障集,網(wǎng)絡(luò)的所有輸入取自其合法輸入集。

??? 定義1:組合邏輯網(wǎng)絡(luò)對![]() 是自測試的(簡稱ST),若:對任意故障

是自測試的(簡稱ST),若:對任意故障![]() 存在

存在![]() ,使網(wǎng)絡(luò)輸出

,使網(wǎng)絡(luò)輸出![]() 。

。

??? 該定義是說對給定單故障集中的任何一個故障,總存在一個合法輸入,它將導(dǎo)致組合邏輯網(wǎng)絡(luò)產(chǎn)生非法輸出,即用該輸入可檢測此故障。

??? 定義2:組合邏輯網(wǎng)絡(luò)對![]() 是故障保險的(簡稱FSE),若:對任意故障

是故障保險的(簡稱FSE),若:對任意故障![]() 存在

存在![]() 使網(wǎng)絡(luò)輸出

使網(wǎng)絡(luò)輸出![]() ,或者

,或者![]() ,其中G(X)是網(wǎng)絡(luò)的正確輸出。

,其中G(X)是網(wǎng)絡(luò)的正確輸出。

??? 該定義是說在合法輸入條件下,對給定單故障集中的任何一個故障,組合邏輯網(wǎng)絡(luò)將給出一個合法輸出或一個非法輸出,但不會給出同該合法輸入不相對應(yīng)的另一個合法輸出。

??? 定義3:組合邏輯網(wǎng)絡(luò)對![]() 是完全自校驗的,若它對

是完全自校驗的,若它對![]() 是自測試的和故障保險的。

是自測試的和故障保險的。

??? 對給定單故障集中的任何一個故障,完全自校驗的組合邏輯網(wǎng)絡(luò)在合法輸入的情況下,或者產(chǎn)生一個合法輸出,或者產(chǎn)生一個非法輸出,且后者在故障存在期間是必然要出現(xiàn)的。這就使得網(wǎng)絡(luò)在不產(chǎn)生不正確合法輸出的同時,能并發(fā)檢測![]() 中的所有故障,這也正是在線測試對差錯檢測及時性的要求。

中的所有故障,這也正是在線測試對差錯檢測及時性的要求。

??? 若采用檢錯編碼技術(shù)實現(xiàn)自校驗邏輯網(wǎng)絡(luò)時,校驗器的任務(wù)是用來檢查功能模塊輸出碼字的有效性,它能區(qū)分功能模塊輸出是否合法,這種特性被稱為碼分離特性,其定義如下。

??? 定義4:一個邏輯網(wǎng)絡(luò)具有碼分離特性,若滿足:

??? (1)任給![]() ,有

,有![]() (合法輸入映射為合法輸出)

(合法輸入映射為合法輸出)

??? (2)任給![]() ,有

,有![]() (非法輸入映射為非法輸出)

(非法輸入映射為非法輸出)

??? 定義5:一個邏輯網(wǎng)絡(luò)是完全自校驗器,若它具有完全自校驗及碼分離特性。

??? 設(shè)組合邏輯網(wǎng)絡(luò)正確輸入矢量為![]() ,則矢量空間

,則矢量空間![]() 稱作錯誤輸入空間,記作

稱作錯誤輸入空間,記作![]() ;空間

;空間![]() 被稱作非法及錯誤輸入空間,記作

被稱作非法及錯誤輸入空間,記作![]() 。由正確輸入空間

。由正確輸入空間![]() 經(jīng)電路G可在S(F)中產(chǎn)生一個子空間,這個子空間稱為正確輸出空間,記為

經(jīng)電路G可在S(F)中產(chǎn)生一個子空間,這個子空間稱為正確輸出空間,記為![]() 。同樣,對于合法輸入

。同樣,對于合法輸入![]() ,由組合邏輯網(wǎng)絡(luò)可映射為合法輸出空間

,由組合邏輯網(wǎng)絡(luò)可映射為合法輸出空間![]() 它也是輸出矢量空間S(F)的子集。同樣,空間

它也是輸出矢量空間S(F)的子集。同樣,空間![]() 被稱作錯誤輸出空間,記作

被稱作錯誤輸出空間,記作![]() ;空間

;空間![]() 被稱為非法及錯誤輸出空間,表示為

被稱為非法及錯誤輸出空間,表示為![]() 。上述輸出之間有如下關(guān)系:

。上述輸出之間有如下關(guān)系:

![]()

??? 由上面集合之間的關(guān)系我們可以看出,對于無故障組合網(wǎng)絡(luò)的正確輸入,其輸出應(yīng)落入正確輸出空間![]() 中。通過對網(wǎng)絡(luò)的輸出可部分判定系統(tǒng)工作是否正常(無法判斷某些故障)。當(dāng)網(wǎng)絡(luò)發(fā)生故障時,可分成以下幾種情況:①非法及錯誤輸入被映射成

中。通過對網(wǎng)絡(luò)的輸出可部分判定系統(tǒng)工作是否正常(無法判斷某些故障)。當(dāng)網(wǎng)絡(luò)發(fā)生故障時,可分成以下幾種情況:①非法及錯誤輸入被映射成![]() ;②輸入

;②輸入![]() 被映射成為

被映射成為![]() ;③

;③![]() 映入

映入![]() 但已不是正確的映射關(guān)系,也就是說輸入輸出關(guān)系發(fā)生了變化。對于一個高可靠容錯系統(tǒng)來說,必須能夠以比較高的故障覆蓋率來檢測出以上三類差錯(最好在一拍內(nèi)檢出),使系統(tǒng)及時采取措施,隔離故障,將其影響減小到最低限度。在三類錯誤中,第①類和第②類與第③類相比要好檢測一些,高效檢測第③類錯誤是提高系統(tǒng)故障覆蓋率的關(guān)鍵,只有設(shè)計出對以上三類錯誤檢出率均較高的檢錯系統(tǒng),才能保證系統(tǒng)有較高的可靠性。

但已不是正確的映射關(guān)系,也就是說輸入輸出關(guān)系發(fā)生了變化。對于一個高可靠容錯系統(tǒng)來說,必須能夠以比較高的故障覆蓋率來檢測出以上三類差錯(最好在一拍內(nèi)檢出),使系統(tǒng)及時采取措施,隔離故障,將其影響減小到最低限度。在三類錯誤中,第①類和第②類與第③類相比要好檢測一些,高效檢測第③類錯誤是提高系統(tǒng)故障覆蓋率的關(guān)鍵,只有設(shè)計出對以上三類錯誤檢出率均較高的檢錯系統(tǒng),才能保證系統(tǒng)有較高的可靠性。

??? 2 自校驗網(wǎng)絡(luò)的結(jié)構(gòu)

??? 自校驗網(wǎng)絡(luò)具有在無任何外加激勵的情況下能自動檢測其內(nèi)部是否存在故障,這些故障或是永久性的或是暫時性的。設(shè)計自校驗網(wǎng)絡(luò)的主要技術(shù)有檢錯編碼技術(shù),基于自對偶函數(shù)的交替邏輯技術(shù)(交織邏輯技術(shù)),基于對偶函數(shù)的互補邏輯技術(shù),還有基于多值邏輯的實現(xiàn)方法,下面我們主要討論一些實用的實現(xiàn)方法。

??? 2.1 雙軌碼校驗器

??? 雙軌碼校驗器的原理圖如圖3所示。

??? 輸入矢量為![]() ,其中

,其中![]() ,(i=1,2),輸出矢量為

,(i=1,2),輸出矢量為![]() 且滿足:

且滿足:

???

![]() 若

若![]() 且校驗器無故障。

且校驗器無故障。

??? 利用雙軌碼校驗器的上述特點,設(shè)計一對偶組合邏輯網(wǎng)絡(luò),使其輸出向量![]() 和

和![]() 恰好反相,將

恰好反相,將![]() 和

和![]() 加到雙軌碼校驗器輸入端,根據(jù)

加到雙軌碼校驗器輸入端,根據(jù)![]() 就可以判定系統(tǒng)是否發(fā)生故障。

就可以判定系統(tǒng)是否發(fā)生故障。

??? 2.2 可分碼校驗器

??? 可分碼校驗器的結(jié)構(gòu)如圖4所示。校驗器的輸入矢量為![]() ),矢量

),矢量![]() 和

和![]() 分別對應(yīng)可分碼的信息分量和校驗分量。其中,信息分量寬度為

分別對應(yīng)可分碼的信息分量和校驗分量。其中,信息分量寬度為![]() 是校驗分量的寬度,且1+K=n, n=‖Y‖。校驗位生成電路根據(jù)信息位

是校驗分量的寬度,且1+K=n, n=‖Y‖。校驗位生成電路根據(jù)信息位![]() 重新生成校驗位W,由雙軌碼校驗器比較W與

重新生成校驗位W,由雙軌碼校驗器比較W與![]() 的一致性,在無故障的情況下,校驗器的輸出

的一致性,在無故障的情況下,校驗器的輸出![]() 指示輸入矢量的有效性。下面的定理給出了圖4完全自校驗可分碼校驗器的構(gòu)造條件。

指示輸入矢量的有效性。下面的定理給出了圖4完全自校驗可分碼校驗器的構(gòu)造條件。

??? 定理:圖4所示的可分碼校驗器是完全自校驗的,若校驗位生成器是一個無冗余的組合邏輯網(wǎng)絡(luò),且比較器是完全自校驗的。

??? 2.3 互補邏輯網(wǎng)絡(luò)

??? 利用互補邏輯也可以構(gòu)成自校驗電路,如果某一邏輯網(wǎng)絡(luò)其輸入輸出關(guān)系為![]() ,則可構(gòu)造一互補邏輯網(wǎng)絡(luò),使其輸入輸出關(guān)系為

,則可構(gòu)造一互補邏輯網(wǎng)絡(luò),使其輸入輸出關(guān)系為![]() 其中f和f是互補的,在無故障的情況下,其輸出是互補的;若發(fā)生輸出相同,則兩個邏輯電路中必定有存在故障的情況。互補邏輯網(wǎng)絡(luò)實現(xiàn)原理比較直觀,但對較復(fù)雜的系統(tǒng),有許多故障它是檢測不出來的。

其中f和f是互補的,在無故障的情況下,其輸出是互補的;若發(fā)生輸出相同,則兩個邏輯電路中必定有存在故障的情況。互補邏輯網(wǎng)絡(luò)實現(xiàn)原理比較直觀,但對較復(fù)雜的系統(tǒng),有許多故障它是檢測不出來的。

??? 2.4 交織邏輯網(wǎng)絡(luò)

??? 交織邏輯網(wǎng)絡(luò)是基于自對偶函數(shù)的自校驗邏輯網(wǎng)絡(luò)。一個二進(jìn)制變量是交替的,記作![]() 若x在兩個連續(xù)的時間間隔內(nèi)所取的值互補。

若x在兩個連續(xù)的時間間隔內(nèi)所取的值互補。

??? 對任意一個開關(guān)函數(shù)![]() ,若假設(shè)

,若假設(shè)![]() 是交替二進(jìn)制變量,且它們是同步交替的,則g的輸入矢量可表示為

是交替二進(jìn)制變量,且它們是同步交替的,則g的輸入矢量可表示為![]() ,其輸出可表示為

,其輸出可表示為![]() ,要使輸出變量也是交替的,必須滿足

,要使輸出變量也是交替的,必須滿足![]() ,顯然,g必須是自對偶函數(shù)。利用交織邏輯網(wǎng)絡(luò)的這個特點,可以檢測出系統(tǒng)的一部分故障。

,顯然,g必須是自對偶函數(shù)。利用交織邏輯網(wǎng)絡(luò)的這個特點,可以檢測出系統(tǒng)的一部分故障。

??? 3 自校驗網(wǎng)絡(luò)實現(xiàn)方法

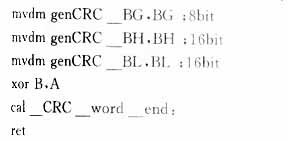

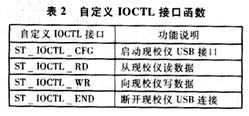

??? 對于一些比較簡單的應(yīng)用場合,利用數(shù)字邏輯方法進(jìn)行設(shè)計,使用SSI及MSI集成電路即可方便地構(gòu)成自校驗網(wǎng)絡(luò)。但實際容錯系統(tǒng)非常復(fù)雜,涉及大量邏輯設(shè)計,若仍采用傳統(tǒng)的數(shù)字邏輯設(shè)計方法,不僅工作量大、容易出差錯,而且修改和功能仿真都不方便。使用電子設(shè)計硬件描述語言VHDL(或Verilog HDL對電路功能進(jìn)行描述,用FPGA或CPLD器件實現(xiàn)自校驗網(wǎng)絡(luò)是比較現(xiàn)實的,對于大批量生產(chǎn),可將VHDL描述的電路送半導(dǎo)體器件廠進(jìn)行批量生產(chǎn),VHDL硬件描述語言實現(xiàn)自校驗網(wǎng)絡(luò)的步驟如下:

??? ①建立自校驗網(wǎng)絡(luò)的功能模型。對系統(tǒng)的輸入/輸出、狀態(tài)轉(zhuǎn)換、信號傳遞等進(jìn)行詳細(xì)的說明。

??? ②用VHDL語言或Verilog HDL語言對電路功能進(jìn)行描述。對復(fù)雜系統(tǒng)可采用撟隕隙?聰?shù)脑O(shè)計方法,將系統(tǒng)分解成不同層次的、功能較簡單的模塊,利用VHDL語言對系統(tǒng)功能進(jìn)行分層描述,減少系統(tǒng)描述造成的錯誤。

??? ③對不同層次的模塊進(jìn)行功能仿真,以檢驗各模塊設(shè)計的正確性,最后對整個系統(tǒng)進(jìn)行功能仿真,及早排除系統(tǒng)設(shè)計中的錯誤。

??? ④用VHDL或Verilog HDL綜合編譯器對設(shè)計好的系統(tǒng)進(jìn)行編譯,經(jīng)過邏輯化簡及綜合布線,生成可對FPG A或CPLD編程的數(shù)據(jù)文件。

??? ⑤將數(shù)據(jù)文件通過編程器寫入FPGA或CPLD,進(jìn)行實際測試,若測試數(shù)據(jù)滿足設(shè)計要求,則開發(fā)工作完成;否則,轉(zhuǎn)①重新進(jìn)行檢查和設(shè)計。

??? 采用自校驗技術(shù)后,可有效地提高容錯系統(tǒng)的可靠性,隨著集成電路技術(shù)的飛速發(fā)展,可將一些自校驗功能模塊進(jìn)行封裝,作為標(biāo)準(zhǔn)單元使用,在模塊級上提高容錯系統(tǒng)的可靠性。采用高級語言和FPGA或CPLD開發(fā)容錯系統(tǒng)具有重要的現(xiàn)實意義,可有效縮短開發(fā)周期,降低開發(fā)成本,提高系統(tǒng)可靠性,應(yīng)在工程設(shè)計中加以推廣應(yīng)

電子發(fā)燒友App

電子發(fā)燒友App

評論